Вычислитель параметров статисти-ческого распределения

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советсмнх

Сецналнстннесмых

Республик

807335

h ЯВ1ЕФЯЯЕНЮ hh hhhhhl Chhh (6t) Дополнительное к авт. свид-ву(22) Заявлено 06.04.76 (21) 2344340/18-24 51 К .з

G G 7/52 с присоединением заявки Н9

Государственнмй комнтет

СССР но делам нзобретеннй н открытий (23) Приоритет—

Опубликовано 230281 Бюллетень 89

Дата опубликования описания 25. 02. 81 (53} УДК 681 ° .3(088.8) гражданской авиации (54) ВЫЧИСЛИТЕЛЬ HAPANETP0B СТАТИСТИЧЕСКОГО

РАСПРЕДЕЛЕНИЯ

Изобретение относится,к специализированным аналоговым вычислительным устройствам и предназначено для обработки статистических данныХ (например, результатов измерений) или стационарных случайных процессов.

Известны устройства,.предназначенные для определения параметров статистических распределений., .Эти устройства содержат накапливающие сумматоры (интеграторы), решающие усилители, нелинеййые преобразователи схемы сравнения и управлял ия (1

Наиболее близким к предлагаемому является вычислитель, содержащий накапливающие сумматоры,. в обратную связь которых включены контакты реле возврата в исходное состояние, блок управления, первый решающий усилитель, выход которого подключен к пер- вому входу второго решающего. усилителя, выход которого является выходом вычислителя 21 .

В схеме этого вычислителя применены также нелинейные .элементы (схема формирования модуля, нелинейные резисторы), которые ограничивают точ ность определения. среднего значения и среднеквадратического отклонения случайных величин °

Цель изобретения - повьтаение точности вычислителя.

Поставленная цель достигается тем, что в вычислитель введены схемы сравнения, первые входы которых являются входом вычислителя, а выходы

1О через контакты второго управляющего реле блока управления подключены к входам соответствующих накапливающих сумматоров, блоки задания порядков интеграторы, входы которых через контакты третьего управляющего реле блока управления соединены с выходами соответствующих накапливающих сумматоров и блоков задания порядков, а выходы интеграторов под2О ключены к вторым входам соответствующих схем сравнения, инвертор, вход которого подключен к выходу первого интегратора и второму входу второго решающего усилителя, а выход интег25 ратора подключен к первому входу пер вого решающего усилителя, второй вход которого соединен с выходом второго интегратора, кроме того, блок управления содержит узел задания объема выборки, первый выход ко/.

807335

:торого соединен.с первым входом счетчика объема. выборки, второй выход — через генератор тактовых импульсов подключен к обмотке второго управляющего реле к второму входу счетчика объема выборки и к первому входу узла управления интеграторами, второй вход которого соединен с выходом счетчика объема, а выходы узла управления интеграторами подключены к обмоткам .соответственно первого и третьего управляющих реле.

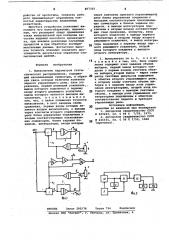

На фиг. 1 представлена блок-схема вычислителя. на Фиг. 2 — схема бло1 ка управления.

Устройство содержит схему 1 сравнения> накапливающие сумматоры 2, интеграторы,3, блоки задания, порядков 4, решающие усилители 5<, 5 2 q инввртор 5 (инвертирующий усилитель) контакты управляющих реле б, 7 и 8.

Влок.9 задания объема выборки, гене". ратор 10 тактовых импульсов,.счет чик 11 объема выборки, узел уравления интеграторами 12 н управляющие реле - 134, 132, 133.

Вычисдитель работает следующим образом.

Коммутация блоков вычислителя осуществляется блоком управления, (фиг. 2). Генератор 10 тактовых импульсов генерирует импульсы, длительность которых обратно пропорциональна объему выборки, задаваемому блоком 9; С частотой тактовых импульсов срабатывает реле 13> (нормально разомкнутые. контакты б на фиг. 1), подключенное к выходу генератора 10, После окончания выборки счетчик 11 .выдает импульс на двухтактиый узел управления интеграторами 12, к выходу которого подключены вторыв и третьи реле.

Причем в первом такте срабатывает рвлв 13 (нормально разомкнутые контактй 8 иа фиг. 1) и во: втором такте - реле 134 (нормально разомкнутыв контакты 7 на фиг. 1).

Далее цикл управления. повторяется.

Собственно вычислитель (фиг. 1) в каждом цикле управления работает следующим образом °

На первые входы схем сравнения

1 подается анализируемое напряже.нив x(t), а на вторые входы — выходные напряжения х, х интеграторов 3. В первом цикле измерения к<е хл О, В случае x(t)cx, первая схема сравнения и, в случае х()ах вторая схема сравнения выдают иа выходе положительные напряжения,фиксированной величины..В противополож. иых случаях, то есть когда x(t)>x+ и x(t)Zx на выходах схем сравнв, л ния напряжения равно нулю.

При срабатывании реле 13 контакты 6 эаьыкаются на время, равное длительности тактового импульса.

Контакты 7 и 8 разомкнуты до конца выборки. На.сумматорах 2 накапливается напряжение, пропорциональное ординатам интегральной Функции распределения F (x) н F (v<), другими словами, пропорциональное порядкам квантилей х и х . На блоках 4 задается некоторое положительное напряжение в пределах от нуля до максимума. Крайние точки нежелательны, поскольку при этом расширяются инте срвалы доверительности. Кроме того, при задании величин F(t<) и F(g) необходимо соблюдать условие F(t<)

F(ty). Близкие значения F(t<) и

F(t ) также нежелательны, так как требуют больших коэффициентов передачи решающих усилителей.

После окончания выборки замыкаются контакты 8 реле блока управле20 ния и в течение определенного интервала времени разности измененных и заданных значений интегральной функции распределения подаются на интеграторы 3, на выходах которых получаются уточненные значения кван,тилей х и х < соответствующие заданным значениям их порядков.

Во втором такте работы узла управления 12 замыкаются контакЗр ты 7 реле, 13. которые устанавли- вают интеграторы 2 в исходное положение. В результате нескольких циклов измерения на выходах интеграторов Z устанавливаются такие эначеЗ5 ния х и х, что с достаточной для практйки точностью можно считать

F (x ) F (t «), Г "(х ) - F (t< )

Поскольку аргумент t нормированной интегральной функции распределения связав со случайной величи" ной х соотношением

Х-x ф,а гдв х — среднее значение, 6 — среднвквадратическое отклонение случайной величины, то последнйе вычисляются на решающих усилителях 5 по известным величинам квантилей х1 и х

6 "g(xq х ); х-х -" 6

4 . гдв R < p k с - постоянные

2 известные коэффициенты, определяемые значениями F(tq) и Г(е, ).

Сходимость процесса. вычисления определяЕтся величинами постоянных времени интеграторов 3. Точность вычисления параметров нормального

40 статистического распределения прак тически определяется точностью вычисления х и х> и при достаточном числе итеграций приближается к точности линейных решающих блоков. Это в5 выгодно отличает предлагаемое уст907335

Заказ 295176 Тираж 756 Подписное

ВНИИПИ

Филиал ППП "Патент, г. Ужгород, ул. Проектная, 4 ройство от прототипа, точность кото . рого принципиальн ограничена точностью характеристик нелинейных резисторов.

Простота устройства позволяет выполнить его малогабаритным, переносным, что расширяет .сферу применения таких вычислителей при контроле качества изделий массового.производства, при анализе различных случайных процессов и при обработке. экспериментальных данных. Достаточно высокая точность позволит увеличить дос товерность результатов обработки статистических данных.

1%

Формула изобретения

1. Вычислитель параметров статистического распределения, содержащий накапливающие сумматоры, в обрат 20 ную связь которых включены контакты первого управляющего, реле, блок уп равления, первый решающий усилитель,, выход которого подключен к первому входу второго решающего. усилителя, Я выход которого является выходом вычислителя, отличающийся тем, что, с целью повышения точности вычислителя, в него введены схемы сравнения, первые входы которых яв- З ляются входом вычислителя, а выходы через контакты второго управляющего реле блока управления подключены к входам соответствующих накапливающих сумматоров, блоки задания порядков, интеграторы, входы которых через контакты третьего управляющего реле блока управления соединены с выходами соответствующих накапливающих сумматоров н блоков задания порядков, а выходы интеграторов подключены к вторым входам соответствующих схем сравнения, инвертор, вход которого подключен к выходу первого интегратора и второму входу второго решающего усилителя, а выход интегратора подключен. к первому входу пер-вого решакщего усилителя, второй вход которого соединен с выходом второго интегратора.

2. Вычислитель по п. 1, о т л и ч а ю шийся тем, что, блок. Управ ления содержит узел задания объема выборки, первый выход которого соединен с первым входом счетчика объема выборки второй выход - через гекес ратор тактовых импульсов подключен к обмотке второго управляющего реле, к второму входу счетчика объема выборки и к первому входу узла управления интеграторами, второй вход которого соединен с выходом счетчика объема, а выходы узла управления интеграторами подключены к обмоткам соответственно первого и третьего управляющих реле.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 409243, кл. С 96 С 7/52, 1973.

2. Авторское свидетельство СССР

9 246161, кл. G 06. С 7/52, 1968 (прототип).