Вычислитель статистических момен-tob

Иллюстрации

Показать всеРеферат

ОПИСЛНИЮ

ИЗОБРЕ Е ИЯ

К АВТОРСКОМУ СВИ ИТИЛЬСТВУ

Союз Советсннк

Сецналнстнческик

Республик («> 807342 (61) Дополнительное к авт. сеид-ву(22) Заявлено 21.08. 78 (21) 2660915/18-24 с присоединением заявки Мо(23) Приоритет— ()публиковано 230281„Бюллетень ЙЫ 7

Датаопубликованияописания 25 02.81 (5 )м. Мл.з

С 06 Я 7/52

Государственный комитет

СССР но делам изобретений. и открмтий (53) УДК 681. 3 (088.8) .f

1 (72) Авторы изобретения

А.Г. Струнин и В.И. Губарь

Киевский ордена Ленина политехнический институт им. 50-летия Великой Октябрьской социалистической революции (71) Заявитель (54) ВЫЧИСЛИТЕЛЬ СТАТИСТИЧЕСКИХ МОИЕНТОВ

Изобретение относится к вычислительной технике и может быть использовано для измерения числовых характеристик совокупности стационарных $ и нестационарных случайных процессов с высокой точностью.

Известен вычислитель статистических моментов, содержащий цифроаналоговый преобразователь, аналого-цифро- 1Q вой преобразователь, ключи, блоки управления, нуль-орган и запоминающее устройство (11 .

Однако такой вычислитель очень сложен при аппаратурной реализации и не позволяет измерять многомерные статистические моменты.

Наиболее близким по технической сущности к предлагаемому является вычислитель статистических моментов,. содержащий последовательно соединенные входной сумматор и масштабный усилитель, выход которого подключен к одному входу первого переключателя, ко второму входу которого под- 2с ключен выход логарифматора, а выход ко входу второго переключателя через последовательно соединенные антилогарифмический усилитель и усредняющий усилитель, к управляющему входу которого подключен через блок запрета один выход автоматического регулятора масштаба, второй выход которого подключен к управляющему входу масштабного усилителя и вход которого - к выходу второй из К последовательцо соединенных дифференцирующих цепочек, один выход второго переключателя подключен к одному входу бло-. ка деления, а второй выход — ко входу запоминающего устройства, выход которого соединен со входом логарифматора и со вторым входом через квадратор блока деления, выход которого подключен ко входу первой дифференцирующей цепи I2) .

Основным источником погрешности такого вычислителя является аналоговый нелинейный блок-антилогарифмический усилитель, работающий на переменном токе s большом динамическом диапазоне, погрешности которого входят в результат измерения К-ого момента как K(5 +gP где О и g -аддитивная и мультипликативная погрешности антилогарифмического усилителя, что не позволяет измерять статистические моменты высоких порядков с погоешностями менее единиц процентов;

807 <4 .. если О и у более десятков процентов,, что для простых антилогарифмических усилителей, работающих в большом динамическом диапазоне в большинстве случаев имеет место., Целью изобретения является повышение точности вычисления многомерных статистических моментов.

Поставленная цель достигается тем, что вычислитель статистических момен- 10 тов, содержащий К последовательно соединенных блоков дифференцирования, входной сумматор, разрядные входы которого являются соответственно входами вычислителя, а выход входного сумматора соединен с первым входом масштабного усилителя, выход которого соединен с первым входом первого переключателя, второй вход которого подключен к выходу логарифматора, а выход через антилогарифмический усилитель 20 соединен с первым входом усредняющего усилителя, выход которого подключен к первому входу второго переключателя, выход которого подключен к первому входу блока деления, а второй вход к входу первого запоминающего блока, при этом второй вход усредняющего усилителя, соединен с выходом блока запрета, вход которого подключен к первому выходу автоматического регулято-. ра масштаба, второй выход которого соединен с вторым входом масштабного усилителя, а вход автоматического регулятора масштаба подключен к выходу второго иэ К последовательно соединенных блоков дифференцирования, содержит третий и четвертый переключатели, блок умножения и второй запоминающий блок, выход которого соединен с первым входом третьего переключателя, выход которого подключен к 40 входу антилогарифматора и второму входу блока деления, выход которого соединен с первым входом блока умножения, выход которого соединен с входом первого из К последовательно сое- щ диненных блоков дифференцирования и входом четвертого переключателя, выход которого подключен к входу второго запоминающего блока, при этом второй вход блока умножения соединен с выходом первого запоминающего блока и вторым входом третьего переключателя.

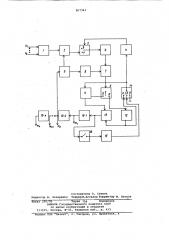

На чертеже представлена блок-схема вычислителя статистических моментов.

Вычислитель содержит входной сумматор 1, масштабный усилитель 2, первый переключатель 3, логарифматор 4, второй переключатель 5,.антилогарифмический усилитель 6, усредняющий усилитель 7, блок 8 запрета, автоматический регулятор 9 масштаба,,К блоков Щ дифференцирования (10-1) †(10-K)> блок

11 деления, первый запоминающий блок

12, блок 13 умножения, третий переклю.чатель 14, второй запоминающий блок .15, четвертый переключатель 16. 65

Входы входного сумматора 1 являются входами вычислителя, а выходы К дифференцирующих цепочек являются соответствующими выходами вычислителя.

Выход сумматора 1 подключен ко входу масштабного усилителя 2, выход которого подключен к одному входу первого переключателя 3, ко второму входу которого подключен выход логарифматора 4, а выход которого подключен ко входу второго переключателя 5 через последовательно соединенные антилогарифмический усилитель 6 и усредняю щий усилитель 7, к управляющему входу которого подключен через блок 8 запрета один выход автоматического регулятора 9 масштаба, второй выход которого подключен к управляющему входу масштабного усилителя 2, и вход которого подключен к выходу второй из К последовательно соединенных блоков дифференцирования (10-1)-ф0-K) один выход второго переключателя 5 подключен к одному входу блока 11 деления, а второй выход — ко входу запоминающего устройства 12, выход которого подключен к входу блока 13 умножения, второй вход которого соединен с выходом блока 11 деления и к первому входу третьего переключателя

14, второй вход которого подключен к выходу блока 13 умножения и кб входу

1 первой дифференцирующей цепи (10-1) через последовательно соединенные второе запоминающее устройство 15 и ключ

16, выход переключателя 14 подключен ко входам логарифматора 4 и блока 11 деления.

Вычислитель статистических моментов работает в и тактов. В первом такте переключатели 3,5 и 14 стоят в положении а, ключ 16 замкнут. На входы сумматора 1 поступают сигналы Х, Х2, ..., ХП, суММа котоРых дя через масштабный усилитель 2, антилогарифмический усилитель 6 и интегратор 7 принимает значение многомерной производящей функции моментов 5:

)о(у А) -М(ехр у() 6)(4 Ц=Е

Эта величина фиксируется в запоминающем устройстве 12 и поступает на один вход умножителя 13 и через логарифматор 4 на клемму б переключателя 3.

Во втором такте переключатели 3 и 5 переводят в положение б, тогда величина )про с выхода логарифматора 4 проходит через антилогарифмический усилитель 6 и интегратор 7 на другой вход схемы 11 деления, на выходе которой образуется величина:

Z.(empt(a))«z) gnz ) а на выходе блока умножения:

z, / å i ð () Ü) ) ô ü z.) =

= ехр 2 у (1+8)((+ I) j /e)),p)II { (+Б) (+ 1 =

807342

=-ехр(2(+Щ g L-(<-о) Ъ+ Z) ) g-. е ру(-)е «) -е«) е г М=е, которая фиксируется в запоминающем устройстве 15. В третьем такте ключ

16 размыкают, а переключатель 14 переводят в положение б, при этом величина Zq поступает на один вход делителя 11 и через логарифматор 4, антилогарифмический усилитель 6, интегра- )(Q тор 7 на другой вход делителя 11, на выходе которого образуется величина:

Z,/å р() +8)(< «))ЕпZ,), а на выходе блока умножения: 15

4о 1

Ех((И БИ g)8)Z Д ехрqÖ Ö(1 g г 26г 26г6г г г =за ехр ((1+ Ь) (+ ) (г g 2 ф г 28 г г гц

=е"РЯ4+(Ь.р 6(3"

«(52, 2, 2 II 62 26 2> Zg2)) которую можно рассматривать как второй скорректированный результат измерения производящей функции моментон S, содержащий погрешность третьего порядка малости. Следующие скорректированные результаты получают так: пе" реключатель 14 ставят в положение в, а ключ 16 замыкают, затем ключ 16 размыкают, а переключатель- 14 ставят в положение б. При этом на выходе умножения 13 последовательно третий, четвертый и т.д. скорректированные результаты Z>, Z4,..., Zt„ причем

z<-exp )(1i)-<) )е iуе)) * 4p

„рг+ 2,2 6г,2 г,,г,-г) «, является результатом измерения производящей функции моментов с погреш" ностью i+1-го порядка малости. При достижении требуемой точности полученную величину S последовательно дифференцируют К раз !

$0 к . — = к

Btк блоками дифференцирования (10-1)(10-K). При этом погрешность изме- рения К-ого момента не превышает вели%йны К(8ФИ1Ф4.

Таким образом, вычислитель статистических моментов выгодно отличается от известных, так как позволяет опре, @j делять одномерные и многомерные статистнческие моменты с наперед заданной точностью, применяя простые, надежные и дешевые блоки для построения вычислителей статистических моментон с самыми высокими метрологическими характеристиками.

Формула изобретения

Вычислитель статистических моментов, содержащий К последовательно соединенных блоков дифференцирования, входной сумматор, разрядные входы которого являются соответственно входами вычислителя, а выход входного сумматора соединен с первым входом масштабного усилителя, выход которого соединен с первым входом первого переключателя, второй вход которого подключен к выходу логарифматора, а вы-. ход — через антилогарифмический усилитель соединен с первым входом ус.редняющего усилителя, ныход которого подключен к первому входу второго переключателя, выход которого подключен к первому входу блока деления, а второй вход - к входу первого запоминающего блока, при этом второй вход усредняющего усилителя соединен с выходом блока запрета, вход которого подключен к первому выходу автомати-: ческого регулятора масштаба, второй выход которого соединен с вторым входом масштабного усилителя, а вход автоматического регулятора масштаба подключен к выходу второго из К последовательно соединенных блоков дифференцирования, о т л и ч а ю щ и йс я тем, что, с целью повышения точности вычисления, вычислитель содержит третий и четвертый переключатели, блок умножения и второй запоминающий блок, выход которого соединен с первым входом третьего переключателя, выход которого подключен к входу ан.тилогарифматора и второму входу блока деления, выход которого соединен с первым входом блока умножения, выход которого соединен с входом первого из К последовательно соединенных блоков дифференцирования и входом четвертого переключателя, .выход которого подключен к входу второго запоминающего блока, при этом второй вход блока умножения соединен с выходом первого запоминающего блока и вторым входом третьего переключателя.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 385284, кл. Q 06 g 7/52, 1971.

2. Авторское свидетельство СССР по заявке Р 2556264/18-24, кл. G 06 g 7/52, 1977 (прототип) °

807342

Составитель Э. Сечина

Редактор В. Лазаренко Техред И.Асталош КорректоР М. Вигула

Заказ 295/ 6 Тираж 756 Подпис ное

ВНИИПИ ГосударственноГо комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35 у Раушская наб., д. 4/5

Филиал IIIIII Патент, г. Ужгород, ул. Проектная, 4