Запоминающее устройство с сохранениеминформации при отключении питания

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

С оцмалистнческик

Республик (>807388 (61) Дополнительное к авт. свил-ву (22) Заявлено 02.02,79 (21) 2720096/18-24 (51)M. Кл.

G 11 С 11/34 с присоединением заявки Ж

Гевударстввииый комитет

СССР (23) Приоритет— (53) УДК б81З27 (088.8) Опубликовано 23.02.81, Бюллетень М 7

Дата опубликования описания 25.02.81

/ по дедам извбрвтвиий и аткрытий

/,:, .У

А 1

Г. К. Алдабаев, К. И. Диденко, Г. И. Загарий, А. Н. онарев," ., -...

А. И. Литкевич и А. А. Ручинский / ..;--, у Ъ; г (72) Авторы изобретения (71) Заявитель

Специальное конструкторское бюро систем автоматнчес управления (54) ЗАПОМИНАЮ111ЕЕ УСТРОЙСТВО С СОХРАНЕНИЕМ ИНФОРМАЦИИ

ПРИ ОТКЛЮЧЕНИИ ПИТАНИЯ

Изобретение относится к запоминающим устройствам.

Известно запоминающее устройство с сохранением информации при отключении питания, содержащее накопитель и схемы регенерации 111.

Недостаток устройства — большие аппаратурные затраты, Наиболее близким к предлагаемому является запоминающее устройство, содержащее основной и резервный источники питания, матрицу памяти, подключенную через диод к питающему входу устройства и зашунтированнукг конденсатором на шину нулевого потенциала и схему сопряжения, адресные, информационные и управляющие входы которой подключены к соответствующим входным шинам устройства, а к выходной информационной шине устройства подключен через схему сопряжения выход матрицы памяти (2).

Однако в известном устройстве при отклю- чении основного источника питания далеко не полностью используются возможности снижения потребляемой энергии матрицей памяти из-за того, что ее адресные, управляющие и информационные входы подключены непосредственно к схеме сопряжения, в результате чего не обеспечивается режим минимального потребления энергии матрицей памяти, а также сложна аппаратурная реализация схем перехода на режим минимального потребления энергии матрицей памяти.

Цель изобретения — уменьшение потребляемой энергии при отключении основного источника питания и упрощение устройства.

Поставленная цель достигается тем, что в запоминающее устройство с сохранением информации при отключении питания, содержащее накопитель, блок сопряжения, первый разделительный элемент, фильтрующий элемент, основной и резервный источники питания, причем вход питания накопителя подключен через первый разделительный элемент к выходу основного источника питания и через фильтрующий элемент — к шине нулевого потенциала, информационный выход накопителя подключен к одному из входов блока сопряжения, другие входы которого являются входами устройства, введены стабилизатор тока, второй и тре807388

50

55 тий разделительные элементы, нагрузочные элементы и элементы гальванической развязки, причем вход резервного источника питания подключен через второй разделительный элемент к выходу стабилизатора тока и через третий разделительный элемент — ко входу питания накопителя, один из выходов, блока сопряжения соединен со входом стабилизатора. тока, другие выходы блока сопряжения через элементы гальванической развязки подключе.ны ко входам накопителя, которые через элементы нагрузки соединены со входом питания накопителя.

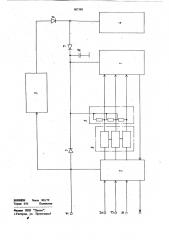

На чертеже изображена функциональная схема предлагаемого устройства.

Устройство содержит накопитель 1, блок 2 сопряжения, стабилизатор 3 тока, резервный источник питания, выполненный в виде блока

4 ионисторов, первый 5, второй 6 и третий 7 разделительные элементы, выполненные в виде диодов, группу элементов 8 гальванической развязки, группу нагрузочных элементов 9, вы. полненных в виде резисторов, фильтрующий элемент 10, например конденсатор,.вход 11 питания накопителя, к которому подключен основной источник питания (на чертеже не показан). Входы блока 2 сопряжения подключены к управляющей 12, адресной 13 и информационной 14 шинам устройства и к информационному выходу накопителя 1, В качестве элементов 8 гальванической развязки могут быть применены трансформаторы, оптроны и т.д. Накопитель 1 может быть построен на интегральных полупроводниковых запоминающих элементах, например КР188РУ2, КМДП-структур, а блок 4 ионисторов может быть составлен из элементов, например, КИ1-1 и КИ1-2.

Вход блока 4 подключен через диод 6 к выходу стабилнзатора тока и через диод 7— ко входу питания накопителя 1. Один из вых дов блока 2 соединен со входом стабилизатора 3 тока, другие выходы через элементы 8 гальванической развязки подключены ко входам накопителя 1, которые через резисторы 9 соединены со входом пигания накопителя 1.

Устройство работает следующим образом.

В штатном режиме напряжение с основного источника питания подается с входа 11 устройства на стабилизатор 3 тока, на блок 2 сопряжения, через первый диод 5 на накопитель 1 непосредственно и на элементы 8 гальванической развязки череЪ резисторы 9, явля- . ющиеся в данном случае их нагрузкой. Таким образом обеспечивается питание всех элементов устройства и происходит зарядка блока 4 иокисторов стабилизированным номинальным зарядным током, при этом зарядке блока иони5

15 го

Зо

35 заторов 4 непосредственно от основного источника питания препятствует третий диод 7.

При исчезновении напряжения основного источника питания напряжение на накопитель 1 поступает с блока 4 ионисторов через третий диод 7, а остальные элементы устройства обеспечиваются благодаря наличию первого 5 и второго 6 диодов.

При этом накопитель 1 переходит на режим хранения с минимальным потреблением энергии по своему питающему входу. Этот режим обеспечивается при помощи резисторов 8, через которые подается напряжение с блока 4 ионисторов на управляющий, адресный н информационный входы накопителя 1. Так как входы потребляют очень малые токи, потенциал на них практически равен напряжению питания накопителя 1, что соответствует упомянутому режиму минимального потребления энергии по питающему входу накопителя 1.

Дополнительную утечку энергии через выход- ные цепи обесточенного блока 2 предотвращают элементы 8 гальванической развязки.

Таким образом, энергия, запасенная в блоке 4 ионисторов, используется только по питающему входу накопителя 1 для сохранения информации, записанной в него ранее. В процессе разряда блока 4 ионисторов напряжение на питающем входе накопителя 1 падает, но если это падение не превышает 50% номинального напряжения, то информация не разрушается. Напряжение такой величины к тому же является рекомендуемым напряжением питания для запоминающих элементов накопителя в режиме хранения информации, так как при этом резко падает потребляемая ими энергия.

Запоминающее устройство на 1024 бит, по-. строенное по предлагаемому принципу на элементах КР188РУ2 и блоке ионисторов из элементов КИ1-1 с общей емкостью 50 ф, после отключения напряжения основного источника питания сохраняет информацию более одного месяца. За указанное время напряжение на блоке ионисторов снижается с 5 В до 2,5 В, что является допустимым для сохранения информации.

Формула изобретения

Запоминающее устройство с сохранением информации при отключении питания, содержащее накопитель, блок сопряжения, первый разделительный элемент, фильтрующий элемент, основной и резервный источники питания, причем вход питании накопителя подключен через первый разделительный элемент к выходу основного источника питания и через фильтрую807388 щий элемент — к шине нулевого потенциала, информационный выход накопителя подключен к одному из входов блока сопряжения, другие входы которого являются входами устройства, о т л и ч а ю щ е е с я тем, что, с целью уменьшения потребляемой энергии при отключении основного источника питания и прощения устройства, оно содержит стабили. затор тока, второй и третий разделительные элементы, нагрузочные элементы и элементы гальванической развязки, причем вход резервного источника питания подключен через второй разделительный элемент к выходу стабилизатора тока и через третий разделительный элемент — ко входу питания накопителя, один из выходов блока сопряжения соединен со входом стабилизатора тока, другие выходы блока сопряжения через элементы гальванической развязки подключены ко входам накопителя, которые через элементы нагрузки соединены со входом питания накопителя.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР У 580587, кл. G 11 С 29/00, 1976.

2. Патент США У 3980935, кл. 340-173, опублик. 1975 (прототип) .