Устройство для асинхронной передачицифровой информации по синхронномуканалу связи

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ИЗЛЬСТВУ

Союз Советскик

Сециапистическик

Республик

<ц807495

4 г. сг" -„

« (61) Дополнительное к авт. свид-ву (22) Заявлено 251278 (21) 2702653/18-09 с присоединением заявки ¹ (23) Приоритет

Опубликовано 2302.81. Бюллетень р 7

Дата опубликования описания 03. 03. 81

Р1 М К э

Н 04 J 3/06

Государствеииый комитет

СССР ио делам изобретеиий и открытий (53) УДК 621. 396. .4 (088.8) 3

Р

C ( (72) Авторы изобретения

В.С..Мальков и В.И.Котов (71) Заявитель (54) УСТРОЙСТВО ДЛЯ АСИНХРОННОЙ ПЕРЕДАЧИ

ЦИФРОВОЙ ИНФОРМАЦИИ ПО СИНХРОННОМУ

КАНАЛУ СВЯЗИ

1 2

Изобретение относится к радиосвязи и может использоваться в много=. канальных импульсных системах с временным уплотнением каналов.

Известно устройство для асинхронной передачи цифровой информации по синхронному каналу связи, содержащее последовательно соединенные задающий генератор, управляемый делитель, выход- которого подключен к первому входу анализатора двойного стробирования, выход которого подключен к входу фазового дискриминатора, при этом выход управляемого делителя подключен к первому вкоду блока регистрации, второй вход которого является входом усто ройства (1).

Однако известное устройство имег ет низкую устойчивость фазирования 20 при превышении скорости передачи информации по каналу связи над скоростью ее ввода более, чем в два раза.

Цель изобретения — повышение устойчивости фазирования при превышении скорости передачи информации по каналу связи над скоростью ее ввода более, чем в два раза . 30

Поставленная цель достигается тем, что в устройство для асинхронной передачи цифровой информации по синхронному каналу связи, содержащее. последовательно соединенные задающий генератор, управляемый делитель, выход которого подключен к первому входу анализатора двойного стробирования, выход которого подключен к входу фазового дискриминатора, при этом выход управляемого делителя подключен к первому входу блока регистрации, второй вход которого является входом устройства, введены кольцевой делитель, дополнительные анализаторы двойного стробирования, дополнительные фазовые дискримийаторы, ключи и .элементы ИЛИ, при этом выход управляемого делителя подключен к первым входам дополнительных анализаторов двойного стробирования, выходы которых подключены к входам соответствующих дополнительных фазовых дискриминаторов, каждый выход кольцевого делителя подключен к второму входу соответствующего анализатора двойного стробирования и к первому входу ключа, второй вход. блока регистрации соединен с вторыми входа807495 ми ключей, выходы которых подключены к другим входам соответствувщих фазовых дискриминаторов, первые выходы фазовых дискриминаторов подключены к входам первого элемента

ИЛИ, а вторые выходы фазовых дискриминаторов подключены к входам второго элемента ИЛИ, при этом выхо, ды элементов ИЛИ, подклвчены к другим входам управляемого делителя.

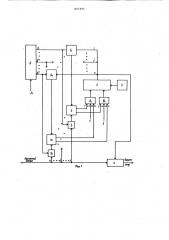

На фиг. 1 приведена структурная электрическая схема предлагаемого устройства; на фиг. 2 — временные диаграммы,. пояснявщие его работу;

Устройство для асинхронной передачи цифровой информации по синхронному каналу связи содержит ос- новной и дополнительные фазовые дискриминаторы 1„...1„, управля-. емый делитель 2, задающий генератор 3, блок 4 регистрации, основной и дополнительные анализаторы

5.>...5>> двойного стробирования, кольцевой делитель б, ключи 71...7„, элементы 8,1 ИЛИ.

Устройство работает следующим образом.

На передаюц>ем конце передаваемый сигнал (фиг. 2 ) преобразуется методом наложения с помощьв импульсов канальной частоты f>.> (фиг. 2 ) в сигнал., изображенный на фиг. 2» и передается по синхронному каналу связи. Принятый иэ канала связи сигнал преобразуется в вид, изображенный на фиг. ?4, и подается на входы- фазовых дискриминаторов 1 через ключи 7. Двоичные знаки принятого сигнала подаются на входы фазовых дискриминаторов 1 только в момекты открывания ключей 7 импульсами с выхода кольцевого делителя б.

Последний делит канальную частоту

Хн в и раз, поэтому íà его выходах формируются частоты f„ - „, равиые по величине f„ /n н сдвинутые по фазе относительно друг друга на один такт частоты

Таким образом, ключи 7 -7>, пропускают двоичные сигналы в моменты формирования импульсов на выходах ,кольцевого делителя б, и на вход каждого из и фазового дискриминатора 1 поступает последовательность двоичных знаков с частотой f>(g=1, 2, 3» ...., и). В каждом из и аналиэаЖров 5 двойного стробирования производится анализ взаимного положения импульсов тактовых частот и ff>, т.е. частоты регистрации, поступающей с выхода управляемого делителя 2. При этом каждый раз когда на один период частоты регистрации fp приходятся два импульса частоты f, анализатор 5 двойнс3го стробирования выдает сигнал на фазовый дискриминатор 1, по которому осуществляется анализ четырех знаков последовательности двончных энаков, поступающих с выхода ключа 7>. Эта последовательность состоит иэ двух знаков, попавших в период частоты Гр, одного предшествующего и одного последующего знака, попавших соответственно в предыдущий и последуюций периоды чаfð

При сфазированном положении импульсов частоты регистрации f>. иэ анализируемых четырех знаков второй и третий одновременны. для этого случая в одном фазовом дискриминаторе 1 анализируются знаки а1, б, бз > в, в другом — В> г, Ãó р д, в третьем — x. а, а,, б, гДе х знак, предшествующий знаку А (см. фиг. 2, 5, б и 7). Так как б является знаком, дублирующим знак Б, r — знаком, дублирующим знак Г, а а З вЂ” знаком, дублирующим знак

2О A то во всех трех четверках знаков (квартах) второй и третий знаки однаковы, что является признаком синфазности частоты fp (фиг. 2 ), поэтому ни один из фазовых дискриминаторов 1 не выдает сигнала рассогла25 сования.

На фиг. 2о представлены импульсы частоты регистрации Гр, фаза которых сдвинута относительно синфазного состояния (фиг. 2 ) в сторону

39 отставания. В этом случае анализируются кварты х>, а, б, б>, (фиг.2 )> б,, в, r, г з (фиг. 2 ), г, д, е, е > (фиг. 2 ), у которых второй и третий знаки могут быть раэноимен35 HbIMH (3To зависит от сТруКТур передаваемой информации) . В том случае, когда второй и третий знаки принимаются разноименными и в то же вре- мя оказываются разноименными первый

4О и второй знаки (при приеме комбинаций вида 0100, как на фиг. 2, или

1011) срабатывают соответствующие фазовые дискриминаторы 1 и выдают сигналы отставания через элемент

81 ИЛИ на вход управляемого делите45 ля 2. На фиг. 2 моменты, в течение которых может выдаваться сигнал, (сигналы 1-3). Аналогичные им (сигналы опережения) вырабатывают фазовые дискриминаторы 1 при приеме

5р комбинаций вида 1101 или 0010 в случае опережения импульсов частоты регистрации относительно нх синфазного положения.

На фиг, 2 стрелками отмечен пе55 риод, с которым повторяется фаза импульсов любой из частоты f на выходе кольцевого делителя б относительно импульсов частоты передаваемого сигнала (в качестве последних можно принять фронты посылок на 0 фиг. 2>). Так как частота на выходе управляемого делителя 2 f больше частоты ГЭ» передаваемого сигнала, но при этом . 1< i 2, то каждый

ff фазовый дискримиХатор 1 предлага65 емого устройства в отдельности раS

807495 ботает так же, как и фазовый дискриминатор в известном. Однако, за время, равное одному периоду повторения, с выходов всех фазовых дискриминаторов 1 может поступить и сигналов рассогласования, каждый из которых вырабатывается в результате анализа отличных друг от друга кварт. При выборе коэффициента деления управляемого делителя 2 в и раз больше, чем в известном, величина изменения фазы импульсов частоты регистрации fg от действия одно сигнала рассогласования в известном и от и сигналов рассогласования в предлагаемом устройстве за один период повторения одинакова. !5

Таким образом, положительный эффект, заключающийся в увеличении устойчивости фазирования частоты регистрации принятого сигнала, достигается путем введения и каналов вы- ;щ деления сигналов рассогласования на периоде повторения. При этом устойчивость фазирования в каждом канале такая же, что и в известном, а устойчивость, обеспечиваемая каналами, значительно выше (примерно в и раз).

Формула изобретения

Источники информации, принятые во внимание при экспертизе, 3S

1. авторское свидетельство СССР

9 634466, кл. Н 04 3 3/06, 1977 (прототип).

Устройство для асинхронной передачи цифровой информации по синхронному каналу связи, содержащее последовательно соединенные заданий генератор, управляемый делитель, выход которого подключен к первому входу анализатора двойного стробирования, выход которого подключен к ю входу фазового дискриминатора, при этом выход управляемого делиТеля подключен к первому входу блока регистрации, второй вход которого является входом устройства, о т л и ч аю щ е е с я тем, что, с целью повышения устойчивости фазирования при превышении скорости передачи ин" формации по каналу связи над скоростью ее ввода более, чем в два раза, введены кольцевой делитель, дополнительные анализаторы двойного стробирования, дополнительные фазовые дискриминаторы, ключи.и элементы ИЛИ, при этом вЫход управляемого делителя подключен к первым входам дополнительных анализаторов двойного стробирования каждый выход

1 кольцевого делителя подключен к второму входу соответствующего анализатора двойного стробирования и к первому входу ключа, второй вход блока регистрации соединен с вторыми входами ключей, выходы которых подключены к другим входам соответ« ствующих фазовых дискриминаторов, первые выходы фазовых дискриминаторов подключены к входам первого элемента ИЛИ, а вторые выходы фазовых дискриминаторов подключены к входам второго элемента ИЛИ, при этом выходы элементов ИЛИ подключены к другим входам управляемого делителя.

Период щЖщоемю

0»

Awas2

Же.2

Составитель В.Маврин

Редактор В.Жиленко Техред М.Голинка Корректор Н.Бабинец

Заказ 338 5 Тираж 709 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб, д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4