Устройство для декодирования вре-мя-импульсных кодов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СЭ ЕТВЛЬСТВУ

Союз Севетскик

Соцналистнческик

Уеслублии (ц807496 (61) Дополнительное к авт. сеид-ву (22) Заявлено 02Ë.078 (21) 2670354/18-09 (Я М. Кл.

Н 04 L 3/02

Н 04 L 17/30

Н 03 IC 13/00

Ф с присоединением заявки Мо

Государственный комнтет

CCCP но дмам нэабретеннй в открытий (23) Приоритет

Опубликовано 23.02.81.бюллетень N9 7

Дата опубликования описания 03. 03. 81 (53) УДК 621.394. .14(088.8) (72) Авторы . изобретения

В.А. Антонов и P.È.Ãàëüïåð (Щ3еяеитель (54) УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ ВРЕМЯИМПУЛЬСНЫХ КОДОВ

Изобретение относится к технике сааза и.может использоваться в системах .передачи информации по каналаи связи, подверженным воздейст9gio помехе

Известно устройство для декодирования время»импульсных кодов, содерващее последовательно соединенйые генератор тактовых импульсов и счетчик, а также элемент И (13.

Однако известное устройство сложно из-за больщого числа счетчиков к элементов И.

Цель изобретения — упрощение устройства путем сокращения числа счетчи ов и элементов И.

° °

Поставленная цель достигается . тем, что в устройство для декодирования время-импульсных кодов, содержащее последовательно соединенные генератор тактовых импульсов и счетчик, а также элемент И, введены последовательно, соединенные формирователь номеров кодового интервала, запоминающий блок, сумматор и блок сравнения., а также запоминающий блок кодовых интервалов, при этом выход счетчика поразрядно соединен с другим входом блока сравнения и .кодовым входом запоминающего блока, другой выход запоминающего блока подключен к соответствующим входам элемента И и формирователя номеров кодового интервала непосредственно и через запоминающий блок кодовых интервалов к другому входу сумматора, один из выходов блока сравнения подключен.к управляющемуовходу считывания запоминающего блока, а другой выход — к соответствующим входам формирователя номеров кодового интервала и элемента И, информационный вход которого объединен со входом записи запоминакщего блока.

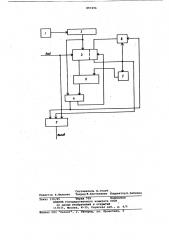

15 На чертеже представлена структурная электрическая схема предлагаемого устройства.

Устройство для декодирования время-импульсных кодов содержит генера20 тор 1 тактовых импульсов, счетчик 2, запоминающий блок 3, блок 4 сравнения, элемент 5 И, сумматор 6, запоминающий блок 7 кодовых интервалов, формирователь 8 номеров кодового интервала.

Устройство работает следующим образом.

Счетчик 2 непрерывно считывает тактовые импульсы,.поступающие с

30 генератора 1. B момент прихода ка807496 кого-либо импульса на вход устрой ства число из счетчика 2 переписывается в запоминающий блок 3, одновременно происходит запись номера кодового интервала (первоначально - единица) в двоичном коде в индексную часть запоминающего блока

3. Он характеризуется тем, что порядок записи чисел соответствует порядку их считывания. Таким образом, записанное число появляется на входах сумматора 6, складывается .с числом (кодовый интервал), извлеченным из запоминающего блока 7 кодовых интервалов, под воздействием соответствующего номера кодового интервала, появившегося на индексном выходе запоминающего блока 3.

Одновременно данный "номер" поступает на вход, формирователя 8 номеров кодового интервала, которое подготавливает для будущей записи следующий номер кодового интервала.

Сумматор 6 представляет собой замкнутое (подобно счетчику) устройство, на. выходе которого не может появиться число большее, чем максимальный кодовый интервал в декодируемом время-импульсном коде.

Блок 4 сравнения сравнивает два числа: число с выхода сумматора 6 и постоянно меняющееся число на вы.ходе счетчика 2. Когда два числа сравняются, на выходе блока 4 сравнения врабатывается сигнал, по которому на выходе формирователя 8 по-. является следующий по порядку номер кодового интервала. Если в этот момент приходит очередной импульс кодовой последовательности, то в кодовую часть запоминающего блока 3 из счетчика 2 переписывается число, а в индексную часть запоминающего блока 3 - подготовленный номер кодового интервала. В случае отсутствия импульса на входе устройства в момент появления сигнала на выходе блока 4 сравнения никакой записи не производится, так как обрабатывается сигнал помехи. После пропа- . дания сигнала на одном выходе, появляется сигнал на другом выходе блока 4 сравнения, по которому происходит считывание из запоминающего блока 3 очередного числа и соответствующего номера кодового инте вала и т.д.

В случае появления на выходе запоминающего блока 3 номера последнего кодового интервала и появления сигнала на выходе блока 4 сравФормула изобретения

Устройство для декодирования время-импульсных кодов, содержащее последовательно соединенные генератор тактовых импульсов и счетчик, а также элемент И, о т л и ч а ю щ е е- . с я тем, что, с целью упрощения

ЗО устройства путем сокращения числа счетчиков и элементов И, введены последовательно соединенные формирователь номеров кодового интервала, запоминающий блок, сумматор и блок

З5 сравнения, а .также запоминающий блок кодовых интервалов, при этом выход счетчика поразрядно соединен с другим входом блока сравнения и кодовым входом запоминающего блока, 40 другой выход запоминающего блока подключен к соответствующим входам элемента И и формирователя номеров кодового интервала непосредственно и через запоминающий блок кодовых

45 интервалов к другому вход сумматора, один из выходов блока сравнения подключен к уравляющему входу считывания запоминающего блока, а другой— выход — к соответствующим входам формирователя номеров кодового интервала и элемента И, информационный вход которого объединен со входом записи запоминающего блока.

Источники информации, принятые во внимание при экспертизе

5!

15

20 кения, на выходе элемента 5 И появляется импульс, совпадающий во времени с последним импульсом декодируемого время-импульсного кода.

Из приведенного описания следует, что генератор 1 и счетчик 2 составляют схему преобразования времякод, а счетчики всех остальных ветвей заменяются запоминающим блоком

3 магазинного типа, причем каждый счетчик эквивалентен одному числу в запоминающем блоке 3, а увеличение числа импульсов в коде вообще приводит лишь к незначительному расширению емкости запоминающего блока 3 (на единицы бит). Поскольку "упаковка" чисел в запоминающем блоке 3, по крайней мере, на 2 порядка плотнее, чем в микросхемах счетчика, применение предлагаемой структуры дает значительный экономический эффект.

1. Авторское свидетельство СССР

9 365039, кл. Н 03 К 13/24, 1971 (прототип).

807496

Составитель Е.Голуб

Редактор B.éèëåíêî ТехредЖ.Кастелевич Корректор Н.Бабинец

Заказ 338 85 Тиразк 709 Подписное

ВНИИПИ,Государственного комитета СССР по делам изобретений и открытий

113о35, Москва, М-35, Раушская наб., д. 4/5.

Филиал ППП "Патент, r. Уигород, ул. Проектная,