Дискретный электропривод

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

809055 (61) Дополнительное к авт. свид.-ву— (22) Заявлено 06.04.77 (21) 2473871/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл з

G 05 В 11/14

Государственный комитет

СССР (53) УДК 62-50 (088.8) Опубликовано 28.02.81. Бюллетень №8

Дата опубликования описания 10.03.81 ао делам изобретений н открытий (72) А вторы изобретения

Б. В. Новоселов, В. М. Архипов, В. И. Платанный, P. М. Трахтенберг, Б. А. Староверов и В. П. Галас (71) Заявитель (54) ДИСКРЕТНЫЙ ЭЛЕКТРОПРИВОД

Изобретение относится к автоматике, а именно к следящим приводам.

Известны дискретные электроприводы с системой фазирования, в которых угловое положение выходного вала устанавливается в cîîòBåòñòâèè с тактовыми импульсами (им- 5 пуль ами фазирования) и которые являются первым приближением следящего привода, замкнутого по углу (1).

Недостатком этих электроприводов является их малая устойчивость и точность.

1о

Наиболее близким к предлагаемому является электропривод, содержащий последовательно соединенные фазовый дискриминатор, усилитель мощности, двигатель, редуктор, дифференциальный датчик и привод стабильной скорости, выход которого соединен со вторым входом дифференциального датчика, выход двигателя через датчик скорости соединен с первым входом. фазового дискриминатора, второй вход которого подключен к выходу делителя частоты (2) .

Недостаток этого привода заключается в узкой области применения и малой точности.

Указанная цель достигается тем, что электропривод содержит два двоичных умножителя, сумматор, преобразователь код-фаза и логический блок, первый и второй входы которого соединены соответственно с двумя выходами дифференциального датчика, третий вход — с выходом преобразователя код-фаза, один вход которого соединен с выходом логического блока, а второй вход с первым входом первого двоичного умножителя, второй вход и выход которого соединены соответственно со вторым выходом и четвертым входом логического блока, пятый вход которого связан с выходом второго двоичного умножителя, один вход которого соединен со вторым выходом первого двоичного умножителя и первым входом сумматора, а другой вход — с третьим выходом логического блока и вторым входом сумматора, третий вход которого связан со вторым выходом второго двоичного умножителя, а выходы соединены соответственно со входом усилителя мощности и входом делителя частоты.

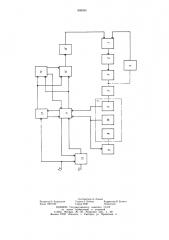

На чертеже представлена блок-схема дискретного электропривода, где обозначены код задающего угла (d.3) и эталонная час809055

55 тота, определяющая дискретность по углу (1»).

Дискретный электропривод содержит последовательно соединенные фазовый дискриминатор 1, усилитель мощности 2, двигатель 3, датчик скорости 4, редуктор 5, статор 6 дифференциального датчика Г, ротор 8 которого соединен с приводом стабильной скорости 9, вход которого подсоединен к выходу неподвижного статора 10 дифференциального датчика 7 и входу логического блока 11, другой вход которого соединен с выходом подвижного статора 6, а третий вход — с выходом преобразователя кодфаза 12, один вход которого соединен со входом электропривода й», другой вход— с выходом логического блока 11, а третий вход соединен с шиной эталонной частоты и входом первого двоичного умножителя 13, второй двоичный умножитель 14, сумматор

15 и делитель частоты 16.

Дискретный электропривод работает следующим образом.

Пусть код задающего угла Ю» на входе преобразователя код-фаза 12 равен нулю и выходной вал привода стабильной скорости 9 не вращается. При этом подвижный статор 6 дифференциального датчика 7 занимает определенное угловое положение и, если это положение такового, что сдвиг между зубцами подвижного 6 и неподвижного

10 статоров датчика 7 отсутствует, то импульсы с выходов подвижного 6 и неподвижного 10 статоров датчика 7 синфазны. Логический блок 11 с приходом импульса с неподвижного статора 10 разрешает прохождение импульсов эталонной частоты f», которая определяется требуемой дискретностью по углу, на преобразователь код-фаза 12.

Последний представляет собой счетчик, если задающий угол подается в цифровом двоичном коде, причем при равенстве задающего кода нулю импульс с выхода преобразователя код-фаза 12 формируется с первым импульсом частоты 1» . Логический блок

11 при поступлении на него импульса с преобразователя код-фаза 12 запрещает прохождение на последний имппульсов f» до следующего импульса с неподвижного статора 10.

Логический блок 11 анализирует величину фазового рассогласования между импульсом с преобразователя код-фаза 12 и импульсом с подвижного статора 6. Если величина этого рассогласования не превышает периода частоты fq, то на двоичный умножитель 13 импульсы частоты f » не поступают и частота на его выходе равна нулю.

В случае, если код задающего углами» не равен нулю, импульс с выхода преобразователя код-фаза 12 сдвинут по фазе относительно импульса с неподвижного статора 10 на время, пропорциональное коду задающего угла Ы», т. е. возникает рассогласование по фазе между импульсом с пре о

15 го

25 зо

4 образователя код-фаза 12 и импульсом подвижного статора 6, которое дискретный электропривод 9 должен отработать. Логический блок 11 на время, равное рассогласованию по фазе между указанными импульсами разрешает прохождение импульсов частоты э на двоичный умножитель 13, где формируется код ошибки между заданным угловым положением и положением подвижного статора 6. С выхода двоичного умножителя 13 частота, пропорциональная ошибке рассогласования, поступает на сумматор 15 и двоичный умножитель 14, который служит для повышения точности электропривода. Смысл введения в электропривод двоичного умножителя 14 состоит в том, что за счет вырабатываемого им корректирующего сигнала необходимая скорость может развиваться электроприводом при сравнительно малой величине сигнала рассогласования. В зависимости от знака рассогласования частота с двоичного умножителя 13 поступает на положительный или отрицательный вход реверсивного счетчика двоичного умножителя 14, а для облегчения формирования выходного сигнала двоичного умножителя 14 в частотно-импульсной форме логический блок 11 обеспечивает вычисление корректирующего сигнала только в прямом коде. Это достигается за счет того, что логическим блоком 11 фиксируется каждое нулевое состояние реверсивного счетчика, входящего в состав двоичного умножителя 14. Если после нулевого состояния на реверсивный счетчик двоичного умножителя 14 приходят вначале импульсы, соответствуюшие положительному рассогласованию, т. е. когда импульс с подвижного статрра 6 отстает от импульса с преобразователя кодфаза 12, то .они поступают на положительный вход реверсивного счетчика, а импульсы, соответствующие отрицательному рассогласованию, поступают на отрицательный его вход, причем знак результата будет положительный. Если же после нулевого состояния реверсивного счетчика двоичного умножителя 14 приходят вначале импульсы, соответствующие отрицательному рассогласованию, то они также поступают на положительный его вход, а импульсы, соответствую;цие положительному рассогласованию, поступают уже на отрицательный вход реверсивного счетчика, причем знак результата будет отрицательный.

Логический блок 11 фиксирует нулевое состояние реверсивного счетчика двоичного умножителя 14 и подключает его положительный вход к выходу двоичного умножителя 13, а знак результата устанавливает аналогичным знаку рассогласования в первый момент. При изменении знака рассогласования с двоичного умножителя 13 логический блок 11 подключает его выход к отрицательному входу реверсивного счетчика двоичного умножителя 14, однако знак

809055

1О

15 го

Формула изобретения

35 результата меняется лишь тогда, когда зафиксируется нулевое его состояние, а на вход после этого будет поступать сигнал рассогласования другого знака.

Частота с выхода двоичного умножителя

14, пропорциональная сигналу коррекции, поступает на второй вход сумматора 15, который производит алгебраическое сложение частот с выходов двоичных умножителей 13 и 14. Так как импульсные последовательности с указанных блоков имеют неравномерный характер, то их сумма и разность будут также иметь неравномерный характер, а поэтому алгебраическая сумма частот сумматора 15 подается на фазовый дискриминатор 1 через делитель частоты 16, который служит для сглаживания неравномерности импульсной последовательности.

Фазовый дискриминатор 1 выявляет фазовое рассогласование частот с делителя частоты 1б и частотного датчика скорости 4 и в функции фазового рассогласования через силовой преобразователь 2 управляет двигателем 3.

Таким образом, введение в известный электропривод вышеперечисленных блоков позволяет использовать его в следящем режиме и значительно lIQBblcHTb точность слежения, т. е. создать помехоустойчивый, термостабильный, высокоточный электропривод. который имеет гораздо лучшие массо-габаритные характеристики по сравнению, например, с цифровыми электроприводами.

Дискретный электропривод, содержащий последовательно соединенные фазовый дискриминатор, усилитель мощности, двигатель, редуктор, дифференциальный датчик и привод стабильной скорости, выход которого соединен со вторым входом дифференциального датчика, выход двигателя через датчик скорости соединен с первым входом фазового дискриминатора, второй вход которого связан с выходом делителя частоты, отличаюи ийся тем, что, с целью расширения области применения и повышения точности электропривода, в него введены два двоичных умножителя, сумматор, преобразователь код-фаза и логический блок, первый и второй входы которого соединены соответственно с двумя выходами дифференциального датчика, третий вход — с выходом преобразователя код-фаза, один вход которого соединен с выходом логического блока, а второй вход — с первым входом первого двоичного умножителя, второй вход и выход которого соединены соответственно со вторым выходом и четвертым входом логического блока, пятый вход которого соединен с выходом второго двоичного умножителя, один вход которого соединен со вторым выходом первого двоичного умножителя и первым входом сумматора, а другой вход — с третьим выходом логического бло- . ка и вторым входом сумматора, третий вход которого соединен со вторым выходом второго двоичного умножителя, а выходы соединены соответственно со входом усилителя мощности и входом делителя частоты.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 2152282/24, кл. G 05 В 11/30, 1975.

2. Авторское сивидетельство СССР № 2310754/24, кл. G 05 В 1!/30, 1977 (прототип).

809055

Составитель А. Лащев

Редактор Н. Безродная Техред А. Бойкас Корректор В. Бутяга

Заказ 10877/52 Тираж 9чО Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», r. Ужгород, ул. Проектная, 4