Цифровая следящая система

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

< i809059

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 02.12.76 (21) 2424901/18-24 с присоединением заявки №вЂ”

1 (23) Приоритет— (51) М. Кл.

G 05 В 11/26

Государственный комитет

СССР ао делам изобретений н открытий

Опубликовано 28.02.81. Бюллетень № 8

Дата опубликования описания 10.03.81 (53) УДК 62-50 (088.8) (73) А вторы изобретения

В. С. Потапов, М. А. Штимер и: В. Д. P (7! ) Заявитель (54) ЦИФРОВАЯ СЛЕДЯЩАЯ СИСТЕМА

Предлагаемая цифровая следящая система относится к радиотехнике и предназначена для получения разностного отсчета при слежении за фазой сигналов в условиях помех.

Известна цифровая следящая система, содержащая линии задержки, генератор опорной частоты, делители, схемы запрета, счетчики результатов, вспомогательные счетчики, триггеры, временной дискриминатор и схемы перезаписи (1).

Однако данная схема не решает вопро- 10 сов фильтрации сигналов и получения разностного отсчета в условиях действия помех.

Известны следящие системы, содержащие опорный генератор, интегратор, реверсивный счетчик, делитель и дискриминатор знака рассогласования (2).

Недостатками данных следящих систем являются снижение надежности системы из-за необходимости введения устройств, . подстраивающих по частоте опорный генератор с тем, чтобы выходная частота системы, находящаяся в прямой зависимости от частоты опорного генератора, была равна частоте сигнала, ибо при расстройке частот получение разностного отсчета становится невозможным,, и снижение быстродействия, а также надежности системы при работе со схемой совпадения кодов большой разрядности или при работе на частоте, близкой к граничной, из-за задержки в цепях переноса делителя.

Цель изобретения — повышение быстродействия и надежности цифровой следящей системы.

Указанная цель достигается тем, что в ци фровую сл едящую систему, содержа щую последовательно соединенные делитель частоты, дискриминатор знака рассогласования> интегратор, реверсивный счетчик, а также генератор опорной частоты, введены блок перезаписи, последовательно соединенные триггер и элемент И, блок задержки и элемент ИЛИ, выходы которых соединены со входами триггера, а входы — соответственно с первым входом блока перезаписи и выходом делителя частоты, входы которого соединены с выходами элемента И и блока перезаписи, другие входы которого соединены с выходами реверсивного счетчика, а выход генератора опорной частоты соединен со вторым входом элемента И.

809 059 в исходно= состояние и закрывает схему И 6, и на вход делителя частоты 9 прекращается поступление импульсного напряжения до момента появления очередного импульса

45 напряжения сигнала f, Следовательно, период выходной последовательности импульсов fII ® задается импульсной последовательностью напряжения сигнала 1,, т. е неф зависимо от расстроики опорного генератора (расстройка определяется заданной инструментальной точностью), частота выходного напряжения 1в „равна частоте сигнала (с, Импульсная последовательность напря- 55 жения f I„x è сигнал f c< подаются на дискриминатор 10 знака рассогласования, где сравниваются между собой по фазе. В резульСистема работает следующим образом.

При поступлении импульсной последовательности одного сигнала на блок перезаписи в делителе частоты устанавливается код, обратный коду реверсивного счетчика (код реверсивного счетчика — начальное

5 значение разности фаз), и на вход делителя частоты начинает поступать импульсная последовательность напряжения опор ного генератора. При переполнении делителя частоты, т. е. с задержкой, определяемой начальным значением разности фаз, на выходе появляется импульс напряжения, стопорящий делитель,. Фаза импульса („ь,„ сравнивается с фазой второго сигнала, в результате чего меняется код в реверсивном счетчике, а следовательно и фаза импульса 15 напряжения на выходе делителя частоты.

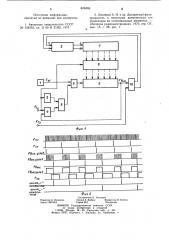

На фиг. 1 представлена блок-схема цифровой следящей системы; на фиг. 2 — диаграммы напряжений.

Система содержит ъпорный генератор 1, интегратор 2, блок 3 задержки, схему ИЛИ 4, триггер 5, схему И 6, реверсивный счетчик 7, блок 8 перезаписи, делитель 9 частоты, дискриминатор 10 знака рассогласования.

Цифровая следящая система работает следующим образом. 25

Импульсная последовательность напряжения опорного генератора 1 подается на один из входов схемы И 6, сигнал f подается

I на вход блока 3 задержки, блока 8 перезаписи и на один из входов схемы ИЛИ 4, сигнал f, подается на один из входов дис-ЗО криминатора 10 знака рассогласования. При поступлении импульса напряжения сигнала

fI„. на вход блока 8 перезаписи на делитель

9 частоты передается дополнительный код реверсивного счетчика 7. Этот же импульс через блок 3 задержки подается на триггер 5, опрокидывает его; и импульсное напряжение f I с опорного генератора 1 подается через схему И 6 на вход делителя 9 частоты. При переполнении делителя частоты 9, т. е. с задержкой, определяемой кодом ре- 40 версивного счетчика, на его выходе появляется импульс напряжения 1,„, который через схему ИЛИ 4 возвращает триггер 5 тате сравнения определяется знак рассогласования между ними, в зависимости от которого с соответствующего выхода дискриминатора импульс напряжения 1 „„поступает на соответствующий (шина сложения или шина вычитания) вход интегратора 2, предназначенного для фильтрации помех, а в конечном счете на вход реверсивного счетчика 7.

Таким образом, меняется код реверсивного счетчика 7, а следовательно и время появления импульсов напряжения f<>® (фаза. импульсов напряжения fw,). При поступлении очередного импульса напряжения сигнала работа схемы повторяется.

Очевидно, что код реверсивного счетчика 7 меняется до тех пор, пока временное положение переднего фронта импульсов напряжения fssIx не совпадет с передним фронтом сигнала f4, т.е. пока импульсы этих напряжений не совпадут по фазе. Наряду с этим каждый импульс выходного напряжения 1 ц„сдвигается по времени относительно соответствующих импульсов напряжения сигнала fr< на число периодов частоты, равное коду реверсивного счетчика 7. Следовательно, в реверсивном счетчике 7 записывается код, соответствующий разности фаз сигналов 1с и 1с, т.е. разностный отсчет.

Использование изобретения позволяет синхронизироваться работе делителя частоты импульсами напряжения сигнала, вследствие чего отпадает необходимость в подстройке частоты опорного генератора, что значительно (примерно в 2 раза) упрощает схему устройства, и вследствие этого повышает его надежиость (примерно в 2,5 раза), и вместо схемы совпадения использовать блок перезаписи, реализация которого более, чем в 1,5 раза проще схемы совпадения и обеспечивает надежную работу следящей системы большой разрядности на частотах, близких к граничной частоте срабатывания элементов.

Формула изобретения

Цифровая следящая система, содержащая последовательно соединенные делитель частоты, дискриминатор знака рассогласования, интегратор, реверсивный счетчик, а также генератор опорной частоты, отличаюи4аяся тем, что, с целью повышения быстродействия и йадежности системы, в нее введены блок перезаписи, последовательно соединенные триггер и элемент И, блок задержки и элемент ИЛИ, выходы которых соединены со входами триггера, а входы — соответственно с первым входом блока перезаписи и выходом делителя частоты, входы которого соединены с выходами элемента И и блока перезаписи, другие входы которого соединены с выходами реверсивного счетчика, а выход генератора опорной частоты соединен со вторым входом элемента И.

809059 фиг. 1 тоГ

Яых. узла т бь/х.узла 6 6Ь/Х.

7бых.узла5

Составитель Н. Ткаченко

Редактор А. Лежнина Техред А. Бойкас Корректор В. Бутяга

Заказ 10878/53 Тираж 951 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5Филиал ППП «Патент>, г. Ужгород, ул. Проектная, 4

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 334553, кл. G 05 В 21/02, 1975. т са шина„+" накепите шина„-" накопй теля

2. Земляков А. И. и др. Дискретный фазовращатель и некоторые возможности его реализации на потенциальных элементах.—

«Вопросы радиоэлектроники», 1970, сер. ОТ, 5 вып. 15, с. 28, рис. i.