Цифровое устройство для воспроизве-дения функций

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗЬБРЕТЕН ИЯ

К .АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (»)809126 (61) Дополнительное к авт. свид-ву— (22) Заявлено 07.03.79 (21) 2735829/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл.

G 06 F 1/02

Геаударатваивыа кеннтет

СССР ао делан нзабретекий н юткрытнй

Опубликовано 28.02.81. Бюллетень № 8

Дата опубликования описания 05.03.81 (53) УДК 681.3 (088.8) (72) Авторы изобретения

А. Н. Флоренсов и В. И. Потапов

Омский политехнический институт(71) Заявитель (54) ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ВОСПРОИЗВЕДЕНИЯ

ФУНКЦИЙ

Изобретение относится к вычислительной технике и может быть использовано для аппаратурной реализации функций в специализированных и универсальных быстродействующих цифровых вычислительных машинах. 5

Известно устройство, содержащее регистры старших и младших разрядов аргумента, блоки памяти, блоки умножения и сумматор (1).

Недостаток известного устройства состоит в ограниченной точности.

Наиболее близким к предлагаемому является устройство, содержащее регистры старших и младших разрядов аргумента, два коммутатора, первый буферный регистр, сумматор, регистр результата, первый, второй и третий блоки памяти, адресные входы которых подключены к выходу регистра старших разрядов аргумента, а выходы первого, второго блоков памяти и первого буферного регистра соединены соответственно с первым, вторым и третьим входами первого коммутатора, выход которого подключен к.первому входу сумматора, выход которого подключен ко входам регистра результата и первого буферного регистра, выход третьего блока памяти соединен. с первым входом второго коммутатора, а управляющие входы первого и второго коммутаторов подключены соответственно к первому и второму выходам блока управления (2) .

Однако такое устройство характеризуется возможностью применения лишь для малоразрядных ЦВМ.

Цель изобретения — расширение класса решаемых задач за счет возможности применения с ЦВМ средней и большой разрядности.

Поставленная цель достигается тем, что в устройство введены четвертый и пятый блоки памяти, второй буферный регистр, третий коммутатор и блок деления, вход делимого которого соединен с выходом второго коммутатора, а выход делителя подключен к выходу сумматора, выход блока деления через второй буферный регистр соединен с первым входом третьего коммутатора, второй вход которого соединен с выходом регистра младших разрядов аргумента, выход третьего кОммутатора подключен ко второму входу сумматора, адресные входы четвертого и пятого блоков памяти соединены с выходом регистра старших раз809126 рядов аргумента, а их выходы соответственно с четвертым входом первого и вторым входом второго коммутаторов, управляющий вход третьего коммутатора подключен ко второму выходу блока управления.

Вычисление значений функции в предлагаемом устройстве производится на основе следующих соотношений. Пусть задана функция F(x), 0 (3.(х =5 (1, удовлетворяющая условию /F(x)/ <1, значения аргумента Х представляются и разрядным двоичным кодом, а значения функции Y = F(X) тре-1О буется находить с и верными двоичными циф рами после запятой. Фиксируем значение параметра К, 1 (К (и, и разбиваем аргумент X = О, Х, Х ... Х . в сумму двух слагаемых Хо = О,Х4 ..X О...О и ЬХ = 0,0...0Х ..Хк, Х = Xo+ АХ.

Расчеты показывают, что значения заданной функции F (X) можно аппроксимировать выражением

U(X) = A(Xo) + р-д.-у, (О 20

5(Xo> (о) Х р.„), ( где коэффициенты А(Хо), В(Хо) С(Хо)

p(Xo) и E(Xo) зависят только от промежуточного аргумента Хр, но не зависят от

ДХ и определяются следующим образом через вспомогательные функции фХ), (Z) ср(2) = (ф(2)- 4 (Z) Фз(2))/(Фз(2)— — Ф,(Z) ф4(Z) );

9(Z) = (Фс() Ф4(2) — Фг(Х) Фз(Х) ) /

/(Фз(Х) — Ф (Х) ф4(2) );

А(Хо) = Фо(Хо) + Ф (Х ) (Хо) + Ф (Х )1

xx(f(XO);

В (Хо ) = Ф (Xo) (Р(Хо) — / (X o) )

Ф2(ХО) Ч(ХО) Чl (Хо), Е (Хо) = фХр) (Ф4(Хо) Y (Xo) + Ф (Х )

ФХо))/ Ф(Хо) (У (Хо) — y(Xo)) +

+ q,(Х,) ю(Хо) (Х 3;

С (Хо) = 1 (Xo) — E (Xo)

13(ХО) = 4У(Хо) — С(Хо) Е(Хо); ф;(Х) = —, F (Z), где i = 0,5. (i) 4

Значение параметра К для. получения верными всех двоичных разрядов результата и необходимо при этом взять из выражения К = (и+1+ !од М)/5, где

М=-0<74 Ь

0 <, <..2

à(Z) + +(Z) qjZ) + В(+ ) S (Z)

Значения коэффициентов А(Хо), В(Хо)

С(Х ), p(Xo) и Е(Хо) предварительно рассчитываются по указанным формам и запоминаются по соответствующим адресам блоков памяти предлагаемого устройства.

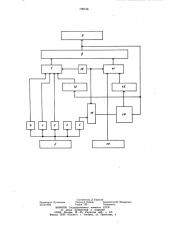

На чертеже представлена блок-схема устройства.

Цифровое устройство содержит блоки

1, 2, 3, 4 и 5 памяти, регистр 6 старших разрядов аргумента, первый коммутатор 7, сумматор 8, регистр 9 результата, регистр

10 младших разрядов аргумента, третий коммутатор 11, первый буферный регистр 12, второй буферный регистр 13, блок 14 деления, второй коммутатор 15, блок 16 управления.

Предлагаемое устройство работает следующим образом.

В первом такте по адресу Хо, передаваемому с выхода регистра 2 старших разрядов аргумента на входы блоков 1, 2, 3, 4 и 5 памяти, на выходах блоков памяти появляются соответственно значения коэффициентов Е(Хо), С(Хо), В(Хо), А(Хо) и В(Хо).

Значение коэффициента P (Xо) через первый вход второго коммутатора 15, подключаемого в этом такте блоком 16 управления, передается на вход делимого блока 14 деления. Одновременно с этим на вход делителя блока 14 деления с выхода многоразрядного комбинационного сумматора 8 поступает E(Xo) + h)(,,образованное в результате подачи на этот сумматор через первый вход первого коммутатора 7 значения коэффициента Е(Х©) с выхода блока 1 памяти и подачи на другой вход сумматора через первый вход третьего коммутатора 11 значения приращения ЬХ, хранящегося на регистре 10 младших разрядов аргумента.

В результате выполнения первого такта на выходе блока деления образуется значение

P (Х о) / (Е (X о) + hX), запоминаемое на втором буферном регистре 13.

Во втором такте работы значение промежуточного результата В(Хо)/(E(Xo) + ЬХ) через второй вход третьего коммутатора со

809126 го

/ (Е (Х o) + ЬХ) запоминается на втором буферном регистре 13.

В последнем, четвертом, такте работы устройства на многоразрядном комбинационном сумматоре 8 происходит сложение значения коэффициента А (Хд), поступающего через четвертый вход первого коммутатора с выхода блока 4 памяти, и промежуточного результата, поступающего через второй вход третьего коммутатора 11 с выхода второго буферного регистра 13, что дает согласно формуле (1) искомое значение функции, запоминаемое на регистре 9 результата.

Таким образом, предлагаемое устройство расширяет область применения аппаратурной реализации ряда функций, в частности элементарных, на ЦВМ средней и боль- 3s шой разрядности.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 575647, кл. G 06 F 7/38, 1977.

4О 2. Авторское свидетельство СССР по заявке № 2415788/18 — 24, кл. G 06 F 1/02, 20.04.77 (прототип) .

Формула изобретения второго буферного регистра 13 и значение коэффициента С(Хр) через второй вход первого коммутатора с выхода блока памяти поступают на многоразрядный комбинационный сумматор, образуя результат Р = С(ХО)

+ Р(Х ЯЕ(Х ) + hX), запоминаемый на первом буферном регистре 12.

В третьем такте работы устройства на вход делимого блока 14 деления через второй вход второго коммутатора 15 с выхода блока5 памяти поступает значение В (Xa) а на вход делителя с выхода многоразрядного комбинационного сумматора 8 — значение (С(Хо) + ЬХ + D(Xo))/(Е(Хо) + ), образуемое путем сложения на последнем значении приращения ЬХ, передаваемого через первый вход третьего коммутатора

11, и поступающего через третий вход первого коммутатора с первого буферного регистра 12 значения Р; Результат деления

V = В(Х,)/((C(Xo) + ЬХ + D(X,))/

Цифровое устройство для воспроизведения функций, содержащее регистры старших и младших разрядов аргумента, два коммутатора, первый буферный регистр, сумматор, регистр результата и три блока памяти, адресные входы которых подключены к выходу регистра старших разрядов аргумента, а выходы первого и второго блоков памяти и первого буферного регистра соединены соответственно с первым, вторым, и третьим входами первого коммутатора, выход которого подключен к первому входу сумматора, выход которого подключен ко входам регистра результата и первого буферного регистра, выход третьего блока памяти соединен с первым входом второго коммутатора, а управляющие входы первого и второго коммутаторов подключены соответственно к первому и второму выходам блока управления, отличающаеся тем, что, с целью расширения класса решаемых задач за счет возможности применения с

ЦВМ средней и большой разрядности, в него дополнительно введены четвертый и пятый блоки памяти, второй буферный регистр, третий коммутатор и блок деления, вход делимого которого соединен с выходом второго коммутатора, а выход делителя подключен к выходу сумматора, выход блока деления через второй буферный регистр соединен с первым входом третьего коммутатора, второй вход которого соединен с выходом регистра младших разрядов аргумента, выход третьего ком мутатора подключен ко второму входу сумматора, адресные входы четвертого и пятого блоков памяти соединены с выходом регистра старших разрядов аргумента, а их выходы соответственно с четвертым входом первого и вторым входом второго ком мутаторов, управляющий вход третьего коммутатора подключен ко второму выходу блока управления.

709126

Редактор Н. Кузнецова

Заказ 8/56

Составители Д. Карасов

Техред А. Бойкас Корректор Ю. Макаренко

Тираж 745 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», r. Ужгород, ул. Проектная, 4