Устройство для синхронизации обменамежду коммуникационным процессороми каналами связи

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕ Н ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советски к

Социалистических

Республик

G 06 F 3/04

G 06 F 1/04

Геоударстеенный комнтет

СССР (53) УДК 681.325 (088.8) Опубликовано 28.02.81. Бюллетень ¹ 8

Дата опубликования описания 05.03.81 по делам изобретений и открытий (72) Авторы изобретения

С. Г. Андросенко, М. В. Динович, A. A. Морозов и В (7! ) Заявитель

Ордена Ленина институт кибернетики АН Украине (54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ОБМЕНА

МЕЖДУ КОММУНИКАЦИОННЫМ ПРОЦЕССОРОМ

И КАНАЛАМИ СВЯЗИ

Изобретение относится к вычислительной технике и может быть использовано в узлах коммутации сообщений сетей связи.

Известны устройства для многоканального сопряжения телеграфных каналов с

ЭВМ, содержащие блок согласования с каналом, два приемных блока, блоки измерения общей загрузки низкоскоростных каналов, элемент ИЛИ, группу разделителей передач по типу, включающих буферный запоминающий блок, блок определения вида кода, блок определения скорости передачи (!).

Недостатком этих устройств являются большие аппаратурные затраты.

Наиболее близким по технической сущности к предложенному является устройство для синхронизации ввода информации изканала связи, содержащее узел управления, включающий распределитель и счетчик состояний, дешифратор времени, шесть регистров, схему сравнения и сумматор (2).

Недостаток устройства заключается в больших аппаратурных затратах при подключении к коммуникационному процессору разноскоростных каналов связи.

Цель изобретения — сокращение аппаратурных затрат.

Поставленная цель достигается тем, что в устройство, содержа гцае два регистра, узел управления, включающий распределитель сигналов, и счетчик состояний и регистр адреса, причем первые входы распределителя сигналов и счетчика состояний подключены к первому входу устройства, выход и второй вход распределителя сигналов соединены соответственно со вторым входом и выхоt0 дом счетчика состояний, введены шифратор, три распределителя импульсов, делитель частоты и генератор тактовой частоты, причем выход. генератора тактовой частоты через делитель частоты соединен с третьим входом счетчика состояний, первые входы распределителей импульсов подключены к выходу распределителя сигналов и первому выходу устройства, второй вход первого распределителя импульсов соединен со вторым входом устройства, а выход — с первым входом первого регистра, второй вход которого подключен к выходу второго распределителя импульсов и четвертому входу счетчика состояний, а выход — ко второму входу второго распределителя импульсов и

809142 первому входу шифратора, выходом соединенным со вторым выходом устройства, а вгорым входом — с выходом регистра адреса и вторым входом третьего распределителя импульсов, выходы подключены к первому входу регистра адреса, второй вход которого соединен с выходом второго регистра, первый и второй входы которого подключены соответственно к выходу распределителя сигналов и третьему входу устройства.

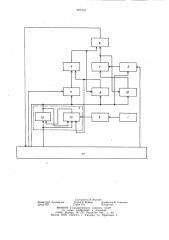

На чертеже представлена блок-схема устройства. 10

Устройство содержит генератор 1, задающий тактовую частоту устройства, делитель 2 частоты, вырабатывающий синхронизирующие импульсы с частотами обмена коммуникационного процессора с каналами

15 связи, узел 3 у.правления, распределитель

4 импульсов, осуществляющий нахождение старшего единичного потенциала кода и запись информации из оперативной памяти процессора в первый регистр 5. осуществляющий хранение кодов групповых ячеек, 20 второй регистр 6, инициирующий вывод в каналы связи, регистр 7 адреса, осуществляющий хранение кодов каналов выдачи, шифратор 8, который формирует номер канала, осуществляющего передачу, второй распределитель 9 импульсов, осуществляющий сброс соответствующего разряда регистра 5 после выдачи очередного бита информации в канал связи, третий распределитель 10 импульсов, который осуществляет сброс соответствующего разряда регистра 6 после окончания передачи всеми каналами, которые взаимодействуют с терминалами на данной частоте обмена, коммуникационный процессор 11, осуществляющий прием, обработку и передачу информации, поступающей по каналам связи. 35

Узел 3 управления включает счетчик 12 состояний, осуществляющий хранение кода текущего состояния устройства, и распределитель 13 сигналов, вырабатывающий си налы управления.

Устройство работает следующим обра- 40 зом.

Информация, поступающая по каналам связи на различных скоростях из множества терминальных пультов в коммуникационный процессор обработки и передачи данных, об- 45 рабатывается программами коммуникационного процессора и законченными сообщениями вводится в центральную ЭВМ телекоммуникационной системы. В случае, если центральная ЭВМ системы осуществляет вывод в канал связи, выводимый документ записы- 50 вается в оперативную память коммуникационного процессора, где формируется канальный массив вывода. Каждому каналу в фиксированной области оперативной памяти коммуникационного процессора 11 соответствуют управляющие слова вывода канала, в которые при первоначальной загрузке, осуществляемой от центральной ЭВМ системы, заносится код константы скорости передачи по каналу, код вида обмена (матричный или циклический), код типа канала связи (дуплексный или полудуплексный), код конфигурации терминалов удаленного пуль та и код длины передаваемого блока. В другой фиксированной области оперативной памяти коммуникационного процессора 11 выделяется определенное поле групповых ячеек вывода в регистре 5, число которых кратно количеству возможных градаций скоростей обмена коммуникационного процессора

11 с каналами связи, так как разрядность групповых ячеек для каждой скорости равна максимальному количеству каналов связи, которые обслуживает коммуникационный процессор 11.

Г1осле сформирования канального массива в соответствии со скоростью обмена по данному каналу и его порядковым номером в соответствующий разряд групповой ячейки регистра 5 программы коммуникационного процессора 11 заносят код «1», кроме того код «1» заносится в соответствующий триггер регистра 6 (каждый триггер скорости групп соответствует определенной скорости обмена по каналу связи).

По синхронизирующим импульсам, вырабатываемым делителем 2 по сигналам генератора I и соответствующим частотам передачи по каналам связи, в регистр 7 заносится код «1» скорости обмена. Кроме того в регистр 5 из оперативной памяти коммуникационного процессора 11 через распределитель 4 заносится код первой групповой ячейки данной скорости, в соответствии с которым шифратор 8 на своем выходе задает код номера выбранного канала и передает его в коммуникационный процессор 11.

Коммуникационный процессор 11 в соответствии с кодом канала выбирает управляющее слово выдачи и отправляет очередной бит передаваемого сообщения в канал. После этого коммуникационный процессор 1 выдает сигнал, который через узел 3 передается в распределитель 9.

Распределитель 9 вырабатывает сигнал, по которому устанавливается в «О» состояние триггер старшего разряда регистра 5 и шифратор 8 задает номер следующего канала, осуществляющего передачу. По сигналам регистра 5 распределитель 9 анализирует состояние триггеров регистра 5. В случае, когда все триггеры регистра 5 сброшены в «О» состояние, выдается сигнал, по которому распределитель 10 устанавливает в «О» состояние старший триггер регистра

7, т.е. выбирается следующая группа каналов, на которых осуществляется передача на другой скорости. Триггера регистра 6 устанавливаются в «О» состояние по сигналам коммутационного процессора 1! после полной выдачи очередного блока по каналу связи.

В процессе реальной работы может возчикнуть необходимость изменения скорости обмена (уменьшить или увеличить) 809142

Формула изобретения по данному каналу, в связи с чем в управляющее слово вывода коммуникационного процессора 11 по команде центрального процессора системы вносится необходимая константа скорости, в результате чего в соответствующую данной скорости и номеру канала групповую ячейку скорости автоматически заносится код «1» и устанавливается в «1» состоя ние соответствующий триггер регистра 6. Следовательно, передача очередного блока для данного канала происходит на другой скорости, которую задал центральный процессор системы.

Таким образом, предлагаемое устройство по сравнению с известными устройствами позволяет выполнять автоматическое изменение скорости обмена в широком диапазоне частот по каналам связи коммуникационного процессора, осуществляющего прием, обработку и передачу информации в режиме реального времени. При этом устройство позволяет значительно сократить аппаратурные затраты за счет исключения необходимости использования для каналов индивидуального оборудования, например, для хранения констант скорости передачи по каналу.

Устройство для синхронизации обмена между коммуникационным процессором и каналами связи, содержащее два регистра, узел управления, включающий распределитель сигналов, и счетчик состояний и регистр адреса, причем первые входы распределителя сигналов и счетчика состояний подключены к первому входу устройства, выход и второй вход распределителя сигналов соединен соответственно со вторым входом и выходом счетчика состояний, отличающееся тем, что, с целью сокращения аппаратурных затрат, в устройство введены шифратор, три распределителя импульсов, делитель частоты и генератор тактовой частоты, причем выход генератора тактовой частоты через делитель частоты соединен с третьим входом счетчика состояний, первые входы распределителей импульсов подключены к выходу распределителя сигналов и первому выходу устройства, второй вход первого распределителя импульсов соединен со вторым входом устройства, а выход — с первым входом первого регистра, второй вход которого подключен к выходу второго распределителя импульсов и четвертому входу счетчика состояний, а выход — ко второму входу второго распределителя импульсов и первому входу шифратора, выходом соединенным со вторым выходом устройства, а вторым входом — с выходом регистра адреса и вторым входом третьего распределителя импульсов, выходы подключены к первому входу регистра адреса, второй вход которого соединен с выходом второго регистра, первый и второй входы которого подключены соответственно к выходу распределителя сигналов и третьему входу устройства.

Источники информации, принятые во внимание при экспертизе

l. Авторское свидетельство СССР № 575642, кл. G 06 F 3/04, 1975.

2. Авторское свидетельство СССР по заявке № 2750253/18-24, кл. G 06 F 3/00, 15.01.79 (п рототи и ) .

Редактор Е..Лушникова

Заказ 4/57

Составитель В. Вертлиб

Техред A. Бойкае Корректор В. Синицкая

Тираж 756 Подпис ное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1 l 3035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», r. Ужгород, ул. Проектная, 4