Преобразователь двоичного кода сме-шанных чисел b двоично- десятичный код

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ, К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик ()809149 (61) Дополнительное к авт. свид-ву № 577524 (22) Заявлено 18.04.78 (21) 2606497/18-24 с присоединением заявки ¹ —— (23) Приоритет—

Опубликовано 28.02.81. Ьюллетснь № 8

Дата опубтикопания описания 05.03.81 (51) М. Кл.з

G 06 F 5/02

Государственный комитет ло делам изооретеиий н открытий (53) УДК 681.325 (088.8) (72) Автор изобретения

В. 1. Роз гв (71) 3аявитель (54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА СМЕШАННЫХ

ЧИСЕЛ В ДВОИЧНО-ДЕСЯТИЧН ЫИ КОД

Изобретение относится к автоматике и вычислительной технике и может быть использовано в специализированных арифметических и логических устройствах, оперирующих в двоичной системе счисления и выдающих результат обработки информации для восприятия в десятичной системе.

По основному авт. св. № 577524 известен преобразователь двоичного кода смешанных чисел в двоично-десятичный код, содержащий блок управления, вход которого соединен с входной управляющей шиной, а выход — с первым входом блока формирования сигналов, первый выход которого соединен через переключатель эквивалентов с входом запоминающего блока, сумматор-вычитатель и сдвигатель, причем первый вход сумматора-вычитателя соединен с выходом запоминающего блока, второй входсо вторым выходом блока формирования сигналов, а выход соединен с первым входом сдвигателя и вторым входом блока формирования сигналов, второй вход сдвигателя соединен с входной информационной шиной, а третий вход — с третьим выходом блока формирования сигналов, четвертый выход которого сослппен с вь;копной информационной t2 >i.,",."ià .

1- с.—,:,:c : ;ем известного преобразователя явл;с-ся то, что для перевода смешанных чисел необходимо увеличивать разрядность су м матора-вычитателя и сдвигателя, так как операнды содержат целую и дробную часть числа. при этом также увеличивается разрядность операндов двоичных эквивалентов, поступающих из запоминающего блока. Такое увеличение длины находящих1о ся в обращении операндов приводит к увеличению вероятности появления отказов, что понижает надежность работы преобразователя.

Цель изобретения — увеличение надежности преобразователя.

Поставленная цель достигается тем, что преобразователь двоичного кода смешанных чисел в двоично-десятичный код дополнительно содержит второй запоминающий блок, управляющий вход которого соединен с последним выходом блока формирования сигналов, информационный вход соединен с входной информационной шиной преобразователя, а выход соединен с информаци809149 онным входом младших разрядов сдвигателя.

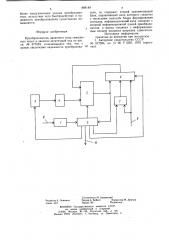

На чертеже представлена структурная схема преобразователя двоичного кода. смешанных чисел в двоично-десятичный код.

Предлагаемый преобразователь содержит блок 1 управления, блок 2 формирования сигналов, переключатель 3 эквивалентов, первый запоминающий блок 4, сумматор-вычитатель 5, сдвигатель 6, второй запоминающий блок 7, входную управляющую шину 8, входную информационную шину 9, О выходную информационную шину 10.

Преобразователь работает следующим образом.

По входной информационной шине 9 на вход сдвигателя 6 поступает двоичный код целой части переводимого смешанного числа, а на вход запоминающего блока 7 дробная часть переводимого числа. Одновременно на шину 8 подается управляющий импульс, который запускает в работу блок

1 управления, вырабатывающий импульсы, п необходимые для автономного функционирования преобразователя. Управляющие импульсы с выхода блока 2 записывают в запоминающий блок 7 дробную часть подаваемого числа и одновременно пропускают через сдвигатель 6 целую часть числа на вход сумматора-вычитателя 5 без сдвига двоичного кода. В то же время в первом такте преобразования управляющий импульс от блока 2, пройдя через переключатель эквивалентов 3, поступает в запоми- зю нающий блок 4, который содержит двоичные эквиваленты десятичных чисел вида (10

2 )э, где 8 — число десятичных разрядов целой части переводимого числа, m 1,2,3... (Ic — 1), К а 1 — общее число десятичных разрядов переводимого числа. Количество з двоичных эквивалентов определяется принятой разрядностью десятичных чисел.

Преобразование осуществляется методом деления переводимого числа (а в дальнейшем остатков) без восстановления остатка на свой двоичный эквивалент при нахождении каждой двоично-десятичной тетрады. Под действием управляющего импульса из блока 4 считывается соответствующий эквивалент (в начале преобразования старший, т.е. m = 1), двоичный параллель- 45 ный код которого поступает на вход сумматора-вычитателя 5 и служит при нахождении данной тетрады делителем. Делимым же служит поступивший на другой вход сумматора-вычитателя 5 двоичный параллельный код входной информации (в дальнейшем делимым является предыдущий остаток) . Блок 2 разрешает в первом такте преобразования вычитание делителя из делимого в сумматоре-вычитателе 5, откуда на вход сдвигателя 6 поступает код полученного частичного остатка, знаковый разряд которого поступает также в блок 2 для формирования кода двоично-десятичной тетрады и определения необходимости вычитания или сложения в следующем такте преобразования. При этом, если по анализу знакового разряда сумматора-вычитателя 5 частичный остаток отрицателен, то блок 2 выдает на выходную информационную шину 10 в виде очередной цифры двоично-десятичной тетрады «О» и подготавливает в сумматоре-вычитателе 5 цепи сложения для следующего такта преобразования, а если частичный остаток положителен, то на выходную шину 10 выдается «1», а в следующем такте производится вычитание делителя из делимого. В следующих тактах определения данной двоично-десятичной тетрады делимое, т.е. предыдущий частичный остаток, передается через сдвигатель 6 на вход сумматора-вычитателя 5 со сдвигом кода на один двоичный разряд в сторону старших разрядов, делитель остается прежним. После нахождения всех цифр двоично-десятичной тетрады, т.е. выполнения четырех тактов, в случае отрицательного остатка производится восстановление положительного остатка в дополнительном такте путем прибавления в сумматоре-вычитателе 5 того же делителя к отрицательному остатку. Для нахождения последующих двоично-десятичных тетрад переключатель 3 эквивалентов переводится под воздействием сигналов блока 2 на выборку из запоминающего блока 4 следующих по порядку (меньших по величине) эквивалентов, которые берутся новыми делителями, в качестве делимых берутся предыдущие положительные остатки и выполняется порядок вышеописанных действий определения кода каждой тетрады. При переходе к переводу дробной части числа предыдущий остаток становится равным нулю, а на вход сумматора-вычитателя 5 поступает из запоминающего блока 7 в первом такте определения данной двоично-десятичной тетрады код числа, сдвинутый в сдвигателе 6 на Зс.разряда в сторону старших разрядов, и определяются аналогично вышеописанному тетрады дробной части числа. Процесс преобразования повторяется до тех пор, пока не будут найдены все десятичные разряды числа.

Предлагаемый преобразователь при преобразовании п-разрядного двоичного кода смешанных чисел в двоично-десятичный код позволяет уменьшить разрядность узлов преобразователя и находящихся в обращении операндов до значения (п — (3 —;4) fj или (и — (3 —;4) д), где д — число десятичных разрядов дробной части переводимого числа. Сокращение длины операндов позволяет уменьшить прежде всего возможность появления ошибки в вычислениях, повысить помехоустойчивость аппаратуры, а также сократить разрядность таких узлов преобразователя, как сумматор-вычитатель и сдвигатель, работающих в непрерывном динамическом режиме в процессе производства преобразований, т.е. являющихся наи809149

Формула изобретения

5 более нагруженными узлами преобразователя, вследствие чего быстродействие и надежность преобразователя сушественно повышаются.

Преобразователь двоичного кода смешанных чисел в двоично-деСятичный код по авт. св. Мв 577524, отличающийся тем, что, с целью увеличения надежности преобразова- 10 теля, ои содержит второй запоминаюший блок, управляюший вход которого соединен с последним выходоМ блока формирования сигналов, информационный вход соединен с входной информационной шиной преобразователя, а выход соединен с информационным входом младших разрядов сдвигателя.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Ко 577524, кл. G 06 F 5)02, 1975 (прототип).

Редактор A. Лежнина

Заказ 4/57

Составитель М. Аршавский

Техред А Бойкас Корректор М. Демчик

Тираж 756 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и о1крытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4