Устройство для формирования позици-онных признаков непозиционного кода

Иллюстрации

Показать всеРеферат

О П И С А Н И Е ()809158

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву— (22) Заявлено 14.06.79 (21) 2780700/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл.з

G 06 F 5/02

Гооударственный комитет

СССР

Опубликовано 28.02.81. Бюллетень № 8

Дата опубликования описания 05.03.81 (53) УДК 681.3 (088.8) по делам изобретений н открытий (72) Автор изобретения

А. Р. Чачанаш вили (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПОЗИЦИОННЫХ

ПРИЗНАКОВ НЕПОЗИЦИОННОГО КОДА

Изобретение относится "к вычислительной технике и может быть использовано в вы (ислительных устройствах, работающих с двухступенчатыми непозиционными кодами.

Известен преобразователь кодов, содержащий счетчики, генератор, вентильные схемы (11.

Наиболее близким по технической сущности к предлагаемому является устройство для формирования позиционных признаков непозиционного кода, содержащее регистры, подключенные ко входам блока хранения констант, выходной сумматор, соединенный с выходными регистрами и со схемой анализа содержимого старших разрядов, сумматор ранга числа, последовательно соединенные двоичные сумматоры, дополнительный двоичный сумматор, схему выработки признака знака(Ц.

Недостатками известных устройств являются низкое быстродействие и структурная

СЛОЖНОСТЬ.

Цель изобретения — повышение быстродействия и упрощение устройства.

Эта цель достигается тем, что устройство для формирования позиционных признаков непозиционного кода, содержащее сумматор по модулю и одноразрядный сумматор, содержит два блока сравнения, причем входы одноразрядного сумматора подключены к шинам задания младших разрядов первого, второго и третьего вычетов, к выходу первого блока сравнения и выходу младшего разряда сумматора по модулю, входы первого блока сравнения соединены с шинами задания второго вычета и выходами сумматора по модулю, входы которого подключены к

1Ц шинам задания третьего вычета, и первой группе входов второго блока сравнения, вторая группа входов которого соединена с шинами задания константы, а выход подключен к управляющему входу сумматора по моду15

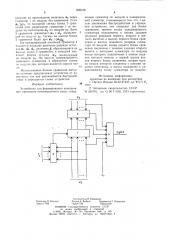

На чертеже приведена блок-схема устройства.

Устройство содержит сумматор 1 по модулю, блоки 2 и 3 сравнения, одйоразрядный двоичный сумматор 4.

20 Устройство работает следующим образом.

Остаток (хз сравнивается с константОй р на блоке 3 сравнения. Если (з (р, то выходной сигнал. блока 3 сравнения даст раз809158

Составитель В. Кайданов

Техред A. Бойкас Корректор Г. Решетник

Тираж 756 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4

Редактор Н. Кешеля

Заказ 17/58 решение на прохождение величины < з через сумматор 1 по модулю без изменения. Если

< 3 )рг, то выходной сигнал блока 3 сравнения даст разрешение сумматору 1 по модулю на вычисление с(з по модулю рг. Блок

2 сравнения сравнивает о4 с с(3, вычисленной по модулю рг. Сигнал на выходе блока

2 сравнения будет при аа )/Ыз/ .

На одноразрядный двоичный сумматор 4 подаются младшие двоичные разряды остатков 3, с(г, с(з, величинар, образуюшаяся на выходе б.гока 2 сравнения, и младший двоичный разряд, остатка о,, вычисленный по модулю рг. На выходе одноразрядного двоичного сумматора 4 образуется сумма

110 модулю два, которая является знаком числа. !5

Использование блоков сравнения выгодно отличает предлагаемое устройство от известного, так как увеличивается быстродействие и упрощается схема устройства.

Формула изобретения 20

Устройство для формирования позиционных признаков непозиционного кода, содержащее сумматор по модулю и одноразрядный сумматор, отличающееся тем, что, с целью увеличения быстродействия и упрощения устройства, оно содержит два блока сравнения, причем входы одноразрядного сумматора подключены к шинам задания младших разрядов первого, второго и третьего вычетов, к выходу первого блока сравнения и выходу младшего разряда сумматора по модулю, входы первого блока сравнения соединены с шинами задания второго вычета и выходами сумматора по модулю, входы которого подключены к шинам задания третьего вычета, и первой группе входов второго блока сравнения, вторая группа входов которого соединена с шинами задания константы, а выход подключен к управляющему входу сумматора по модулю.

Источники информации, принятые во внимание при экспертизе

1. Патент Японии № 52-21337, кл. 97(7) Е, 1977.

2. Авторское свидетельство СССР

¹ 265701, кл. G 06 F 5/02, 1973 (прототип).