Дешифратор

Иллюстрации

Показать всеРеферат

O П И С А Н И Е ()809159

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 04.05.79 (21) 2785306/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М..Кл.з

G 06 F 5/02

Государственный комитет

СССР но делам изобретений и открытий

Опубликовано 28.02.81. Бюллетень №8

Дата опубликования описания 05.03.81 (53) УДК 681.325 (088.8) (72) Авторы изобретен ля

M. А. Минасян и С. А. Мадоян (71) Заявитель (54) ДЕШИФРАТОР

Изобретение относится к вычислительной технике и может быть использовано в узлах и устройствах управления средств вычислительной техники и цифровой автоматики.

Известен дешифратор команд, содержащий регистр сдвига, элементы И, элементы

ИЛИ, входной регистр, логические блоки приема посылок, реле времени, формирователь сигнала исполнения (1).

Недостатком этого дешифратора является сложность конструкции. то

Наиболее. близким по технической сущности является дешифратор, содержащий и-разрядный входной регистр, 2" выходных элементов И вЂ” НЕ и шину стробирования, подключенную к первым входам выходных элементов И вЂ” НЕ, причем единичные и нулевые выходы входного регистра подключены к соответствующим входам выходных элементов И вЂ” НЕ через элемент ИЛИ и И (2).

Недостатком этого дешифратора являет- 2o ся сложность конструкции и относительно низкое быстродействие.

Цель изобретения — упрощение конструкции и повышение быстродействия.

11оставленная цель достигается тем, что дешифратор, содержащий п-разрядный входной регистр, 2 выходных элементов И вЂ” НЕ, причем шина стробирования устройства подключена к одному из n + 1 входов каждого

i-го (i = 1,2,...,2" ) выходного элемента И—

НЕ, он содержит формирователь импульсов, выход которого подключен к первым входам каждого из и разрядов входного регистра, а вход — к шине стробирования устройства, другие и входов i-ого выходного элемента

И вЂ” HE (1

= 1,2,...,n — 1) единичным и нулевым выходам разрядов входного (i 1) -го двоичного числа соответственно единичных и нулевых значений, входы первого выходного элемента И вЂ” НЕ подключены к нулевым выходам каждого из и разрядов входного регистра, вторые входы каждого из и разрядов входного регистра подключены к соответствующим входным шинам дешифратора.

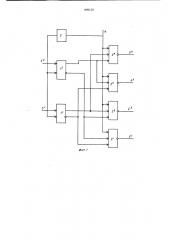

На фиг. 1 приведена блок-схема дешифратора, на примере двухразрядного; на фиг. 2 — временная диаграмма его работы.

Дешифратор содержит входной регистр на триггерах 1 — 1 ; выходные элементы

И вЂ” НЕ 2 — 24; формирователь 3 импульсов;

809159

Формула изобретения шину 4 стробирования; входные кодовые шины 5 - — 5 ; выходные шины 6 — 64, к которым подключены выходы выходных элементов И вЂ” НЕ. Шина стробирования подключена к первым входам выходных элементов

И вЂ” НЕ, а единичные и нулевые выходы вход- s ного регистра подключены к соответствующим выходным элементам И вЂ” НЕ. Вход формирователя 3 подключен к шине стробирования, а выход подключен к входам перезаписи входного регистра.

Дешифратор работает следующим образом.

В исходном состоянии триггеры входного регистра находятся в нулевом состоянии, на комбинационных входах выходного элемента И вЂ” НЕ 2 присутствуют разрешаю- щие потенциалы. При поступлении на шину

4 стробирующего импульса длительностью

tc (фиг. 2, а) на выходе элемента И вЂ” НЕ

2 появляется потенциал нулевого уровня инверсное значение строб-импульса с задержкой с, равной задержке одного вентиля, т. е. элемента И вЂ” НЕ (фиг. 2, в).

Одновременно строб-импульс поступает на вход формирователя 3, который от переднего фронта строб-импульса формирует с задержкой импульс длительностью (ь пнаи, необходимой для надежного срабатывания триггера входного регистра (фиг. 2, б). Выходной импульс формирователя 3 осуществляет перезапись информации во входном регистре.

После окончания перезаписи на вход фор- зо мирователя импульсов 3 поступает второй строб-импульс (фиг. 2, а).

Устройство проще известного как по количеству входящих в него элементов, так и по числу связей. Кроме того, число входов выходных элементов И вЂ” НЕ в известном дешифраторе равно и + 2", где и — число разрядов входного регистра, В дешифраторе число входов выходных элементов И вЂ” НЕ равно п + 1, что также упрощает конструкци Io. 1

Период Т следования строб-импульсов является временем цикла дешифрации. Максимальное быстродействие дешифратора достигается при tc — — t >

= 1с + tg, а время цикла дешифрации известного дешифратора равно Т = tc + 2f .

Ввиду того, что меньше 2t-; максимальное быстродействие дешифратора больше, чем у известного.

Дешифратор, содержащий п-разрядный входной регистр, 2" выходных элементов И—

НЕ, причем шина стробирования устройства подключена к одному из n + I входов каждого i-го (i = 1,2,...,2") выходного элемента И вЂ” HE, отличающийся тем, что, с целью упрощения конструкции и повышения быстродействия, он содержит формирователь импульсов, выход которого подключен к первым входам каждого из и разрядов входного регистра, а вход — к шине стробирования устройства, другие п входов i-ro выходного элемента И вЂ” НЕ (1 (i 2 ) подключены к

m (m = 1,2,...,n — 1) единичным и к нулевым выходам разрядов входного (i — 1) -го двоичного числа соответственно единичных и нулевых значений, входы первого выходного элемента И вЂ” НЕ подключены к нулевым выходам каждого из и разрядов входного регистра, вторые входы каждого из разрядов входного регистра подключены к соответствующим входным шинам дешифратора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 599262, кл. G 06 F 5/02, 1974.

2. Авторское свидетельство СССР № 598066, кл. G 06 F 5/02, 1976. (прототип).

809159

Рие. 2

Составитель В. Кайданов

Редактор А. Власенко Техред А. Бойкас Корректор М. Демчик

Заказ 17/58 Тираж 756 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1) 3035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4