Устройство управления памятью

Иллюстрации

Показать всеРеферат

<11 809182

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

И АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалистическик

Республик (61) Дополнительное к авт. свид-ву— (22) Заявлено 18.06.79 (21) 2784295/18-24 с присоединением заявки №вЂ” (23) Приоритет—

Опубликовано 28.02.81. Бюллетень №8

Дата опубликования описания 28.02.81 (51) М Кл з

G 06 F9/06

Гасударственный комитет по делам иэооретеиий к открытий (53) УДК 681.335 (088.8) (72) Авторы изобретения

И. А. Анучин, В. А. Пелипейко и В. О. Плокс

Институт электроники и вычислительной техникч

АН Латвийской ССР (7l ) Заявитель (54) УСТРОИСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ

Изобретение относится к запоминающим устройствам, а именно к управляющим устройствам памяти и может быть использовано в системах обработки данных.

Известно устройство программного управления, содержащее блок памяти, блок ввода данных, блок записи и считывания программы, в котором программа записывается в память в шаговой последовательности, а затем считывается по мере необходимости (11.

Недостатком такого устройства является отсутствие возможности записи данных в память при работе устройства в режиме непрерывного считывания путем прерывания считываемой программы.

Наиболее близким по техническому решению к предлагаемому изобретению является устройство управления памятью, которое обеспечивает непрерывное последовательное считывание информационных слов из памяти, а также селектчвный ввод информационного слова в ячейку памяти по заданному адресу. Устройство содержит блок ввода данных, блок памяти с произвольной выборкой, распределитель управляющих сиг налов, генератор последовательно сканирую2 щего бинарного сигнала, блок адреса, блок для сравнения адреса (21

Недостатком известного устройства управления памятью является то, что устройство в режиме непрерывного считывания информационных слов из памяти не позволяет осуществлять запись информации в память по заданному адресу путем прерывания режима негрерывного считывания и перехода в режим записи с последующим возвратом в режим считывания, а также низкое быстро1о действием в режиме записи очередного информационного слова в память.

Цель изобретения — расширение функциональных возможностей устройства управления памятью за счет осуществления прерывания процесса считывания в любой момент времени и повышение его быстродействия.

Поставленная цель достигается тем, что в устройство, содержащее блок записи и считывания, первый, второй и третий входы которого соединены соответственно с информа-

20 ционными выходами блока памяти, блока ввода данных и информационными входами устройства, первые и вторые информационные выходы блока записи и считывания сое809182

25 зо

40

se

55 динены соответственно с информационным входом блока памяти и с информационным выходом устройства, группа выходов блока адреса соединена с группой адресных входов блока памяти, йервый и второй выходы распределителя управляющих сигналов соединены соответственно с управляюшим входом блока адреса и четвертым входом блока записи и считывания, введены счетчик адреса, блок записи адреса, блок считывания адреса, регистр адреса программы, регистр адреса, группа разрядных выходов счетчика адреса соединена с группой адресных входов блока адреса и с первой группой входов блока записи адреса, вторая группа входов которого является группой адресных входов устройства, первая группа выходов блока записи адреса соединена с группой информационных входов регистра адреса программы, группа выходов которого соединена с первой группой входов блока считывания адреса, вторая группа входов которого соединена с группой выходов регистра адреса, группа информационных входов которого соединена со второй группой выходов блока записи адреса; группа выходов блока считывания адреса соединена с группой информационных входов счетчика адреса, счетный вход которого соединен с третьим выходом распределителя управляющих сигналов, четвертый и пятый выходы которого соединены соответственно с первым и вторым входами блока записи адреса, первый и второй входы блока считывания адреса соединены соответственно с шестым и седьмым выходами распределителя управляюших сигналов, первый и второй входы которого являются соответственно входами прерывания программы и продолжения программы устройства.

Такое устройство позволяет осуществлять запись информации в память по заданному адресу при работе устройства в режиме считывания информации путем прерывания последнего, и перехода в режим записи с последующим возвратом в режим считывания. Устройство позволяет также уменьшить время записи информационного слова в память по заданному адресу. путем исключения времени, необходимого для сравнения сканирующего бинарного сигнала с кодом заданного адреса.

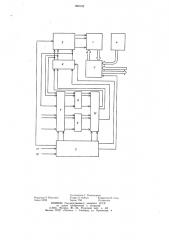

На чертеже представлена блок-схема устройства.

Устройство содержит блок 1 памяти, блок

2 адреса, блок 3 записи и считывания, блок

4 ввода данных, распределитель 5 управляющих сигналов, счетчик 6 адреса, блок 7 записи адреса, регистр 8 адреса программы, регистр 9 адреса, блок 10 считывания адреса, вход 11 прерывания программы, вход 12 продолжения программы.

На адресные входы блока 1 памяти подается код адреса из блока 2 адреса. На информационные входы блока 1 памяти через блок 3 записи и считывания подаются информационные слова, подлежащие записи

Д в память. Ввод информационных слов в блок

1 памяти может осушествлять из блока 4 ввода данных или от внешнего источника информации. Распределитель 5 управляет блоком 3 записи и считывания, устанавливая его либо в режим записи, либо в режим считывания, а также блоком 2 адреса, осуществляя подачу кода адреса, поступающеro из счетчика 6 адреса, на адресные входы блока 1 памяти. На входы блока 7 записи адреса, служащего для записи кода адреса в регистр 8 адреса программы и в регистр 9 адреса, поступают коды двух адресов — со счетчика 6 адреса и непосредственно со входов устройства. Коды адресов со счетчика 6 адреса и со входов устройства с помощью управляющих импульсов, поступающих из распределителя 5, могут быть записаны соответственно в регистр 8 адреса программы и в регистр 9 адреса. Управляющие импульсы, поступаюшие импульсы, поступающие из распределителя 5, осуществляют управление блоком 10 считывания адреса. С помощью этих импульсов в счетчик б адреса производится запись содержимого регистра 8 адреса программы, либо регистра 9 адреса.

Вход 11 прерывания программы и вход 12 продолжения программы служат для установки распределителя 5 в режим прерывания или в режим продолжения соответственно.

Сигнал прерывания по входу 11 прерывания поступает в распределитель 5,прерывает цикл считывания информации из памяти и устанавливает блок 3 записи и считывания в режим записи. Затем распределитель 5 последовательно во времени выдает два импульса, первый из которых подается на блок

7 записи адреса и переписывает содержимое счетчика б адреса в регистр 8 адреса программы, а второй подается в блок 10 считывания адреса и переписывает содержимое регистра 9 адреса в счетчик 6 адреса. В результате в регистре адреса 8 программы запоминается адрес, на котором произошло прерывание программы, а в счетчике 6 адреса устанавливается адрес, по которому следует осуществить запись информации в память.

По окончании записи информации в память в распределитель 5 по входу 12 продолжения программы подается сигнал, по которому блок 3 записи и считывания устанавливается в режим считывания и формируются два следующих друг за другом импульса, первый из которых поступает в блок 7 записи адреса и переписывает содержимое счетчика 6 адреса в регистр 9 адреса, а второй поступает в блок 10 считывания адреса и записывает содержимое регистра 8 адреса программы в счетчик 6 адреса. В результате обеспечивается запоминание в регистре 9 адреса кода адреса, на котором закончена запись информации в память, и установка в счетчике 6 адреса кода адреса, содержашегося в регистре 8 адреса программы, на кото809182 ром ранее было осуществлено прерывание программы. При поступлении очередного импульса прерывания программы описанный процесс повторяется и запись информации осуществляется по адресу, хранящемуся в регистре 9 адреса.

Таким образом, предлагаемое устройство позволяет в режиме непрерывного считывания информации в любой момент времени осуществлять прерывание процесса считывания с целью записи информации по адресу, храняющемуся в регистре 9 адреса. При- 1.О чем такое прерывание можно осуществлять многократно, каждый раз начиная запись с ячейки памяти, адрес которой после предыдущего прерывания запоминается в регистре 9 адреса и на очередном прерывании записывается в счетчик 6 адреса. !

Повышение быстродействия устройства в режиме записи информационных слов в блок

1 памяти достигается тем, что требуемый адрес ячейки памяти через блок 7 записи адреса вводится заранее со входов устройства в регистр 9 адреса. Затем содержимое регистра 9 адреса через блок 10 считывания адреса переписывается в счетчик 6 адреса, устанавливая последний в состояние, соответствующее коду заданного адреса. Такая организация установки адреса позволяет сократить время записи информационных слов в память за счет исключения времени, необходимого для сравнения заданного адреса с бинарным сканирующим сигналом, последовательно принимающим значения, 30 соответствующие адресам блока 1 памяти.

Введение новых блоков позволило в режиме непрерывного считывания программы записывать данные в память. Такой режим работы удобен в1системах обработки данных, когда информация обрабатывается по блокам и результат каждой обработки необходимо запомнить в памяти. При этом за счет исключения времени, необходимого для сравнения заданного адреса с бинарным сканирующим сигналом, уменьшается время запи- 4 си информации в память. В результате расширяются функциональные возможности устройства и повышается его быстродействие.

Формула изобретения

Устройство управления памятью, содержащее блок записи и считывания, первый, второй и третий входы которого соединены

6 соответственно с информационными выходами блока памяти, блока ввода данных и информационными входами устройства, первые и вторые информационные выходы блока записи и считывания соединены соответственно с информационным входом блока памяти и с информационным выходом устройства, группа выходов блока адреса соединена с группой адресных входов блока памяти, первый и второй выходы распределителя управляющих сигналов соединены соответственно с управляющим входом блока адреса и четвертым входом блока записи и считывания, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет осуществления прерывания процесса считывания в любой момент времени и повышения его быстродействия, в устройство введены счетчик адреса,i блок записи адреса, блок считывания адреса, регистр адреса программы, регистр адреса, причем группа разрядных выходов счетчика адреса соединена с группой адресных входов блока адреса и с первой группой входов блока записи адреса, вторая группа входов которого является группой адресных входов устройства, первая группа выходов блока записи адреса соединена с группой информационных входов регистра адреса программы, группа выходов которого соединена с первой группой входов блока считывания адреса, вторая группа входов которого соединена с группой выходов регистра адреса, группа информационных входов которого соединена со второй группой выходов бло. ка записи адреса, группа выходов блока считывания адреса соединена с группой информационных входов счетчика адреса, счетный вход которого соединен с третьим выходом распределителя управляющих сигналов, четвертый и пятый выходы которого соединены соответственно с первым и вторым входами записи блока записи адреса, первый и второй входы считывания блока считывания адреса соединены соответственно с шестым и седьмым выходами распределителя управляющих сигналов, первый и второй входы которого являются соответственно входами прерывания программы и процолжения программы устройства.

Источники информации, принятые во внимание при экспертизе

1. Патент Японии № 52 — 40827, кл. 97/7, 1976.

2. Патент США № 3962689, кл. 340 †1 R, 1977 (прототип).

809182

Редактор Л. Власенко

Заказ 8/59

Составитель Г. Г1оиомарева

Техред А. Бойкас Корректор Н. Степ

Тираж 756 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4