Устройство для функциональногоконтроля микроэлектронных узлов

Иллюстрации

Показать всеРеферат

< >809185

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ .

Союз Советскик

Социалистических

Республии

Ж ,1 (61) Дополнительное к авт. свид-ву— (22) Заявлено 27.11.79 (21) 2688081/18-24 с присоединением заявки №вЂ” (23) Приоритет—

Опубликовано 28.02.81. Бюллетень ¹8

Дата опубликования описания 28.02.81 (51) М Кл з

G 06F 11/00

Гоеударстввнный комитет (53) УДК 681.325 (088.8) до делам изобретений и открытий (72) А вторы изобретения

В. В. Кулаков, Н. В. Лось, В. Г. Рябцев и А. И. Tðàчение — ——

BCEC(1Н,"Зй ; °

ТЕХНИК 11 Ж1,".. "

Научно-исследовательский институт управляющих вычислительных машин (71) Заявитель хщн: (54) УСТРОИСТВО ДЛЯ ФУНКЦИОНАЛЬНОГО КОНТРОЛЯ

МИКРОЭЛЕКТРОННЫХ УЗЛОВ

Изобретение относится к области вычислительной техники и может быть использовано при контроле микроэлектронных узлов.

Иэвестно устройство (1) функционального контроля, содержащее тактовый генератор, блок времени, блок управления, блок хранения результатов контроля, регистр, блок сравнения и блок синхронизации.

Недостатком устройства является ограниченное быстродействие в связи с тем, что информация о результатах контроля выдается не в момент ее выявления, а по сигналу опроса, генерируемому программно.

Наиболее. близким по технической сущности к предлагаемому является устройство для функционального контроля микроэлектронных узлов (2), содержащее блок управления, первый управляющий вход которого соединен с выходом первого блока памяти, информационным входом формирователя адресов испытательных команд и первым информационнным входом формирователя команд, тактовый вход — с первым выходом генератора импульсов, вход которого подключен к выходу пульта управления и входу первого блока памяти, выход блока управления соединен с управляющим входом формирователя адресов испытательных команд и управляющим входом формирователя команд, выход формирователя адресов испытательных команд подключен к первому информационному входу согласующего блока, информационный выход которого соединен со вторым информационным входом формирователя команд, выходы которого соответственно связаны со входами блока оценки результатов контроля и вторым информационным входом согласующего блока.

К недостатку устройства относится пониженное быстродействие, обусловленное потерями времени при замене дефектных объектов контроля.

Цель изобретения — повышение быстро15 действия устройства.

Указанная цель достигается тем, что устройство содержит формирователь сигнала отключения питания объекта контроля, элемент И и второй блок памяти, информационный вход которого соединен с выходом блока оценки результатов контроля, управляющий вход — с управляющим выходом согласующего блока, выходы через элемент И вЂ” со вторым управляющим входом блока управления, а установочный

809185 вход — с выходом формирователя сигнала отключения питания объекта контроля, управляющий вход которого подключен к выходу пульта управления, а тактовый вход— ко второму выходу генератора импульсов.

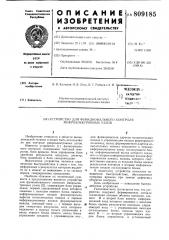

На чертеже изображена функциональная схема устройства.

Она содержит пульт 1 управления, первый блок 2 памяти, генератор 3 импульсов, блок 4 управления, формирователь 5 адресов испытательных команд, формирователь 6 команд согласующий блок 7; блок 8 а оценки результатов контроля, второй блок 9 памяти, блок 10 индикации, элемент И 11, формирователь 12 сигнала отключения питания объекта контроля.

Устройство работает следующим образом.

Программа проверки с пульта 1 заносится в память блока 2. Проверяемая микросхема устанавливается в контактирующее устройство, расположенное на плате блока 7. По командам, поступающим из блока 2, блок 5 выбирает необходимые ячейки памяти контролируемой БИС, а блок 6 заносит контрольную информацию в регистр передачи информации, которая подается через блок согласования в проверяемую микросхему.

В устройстве остановка контроля происходит только при обнаружении ошибок сравнения во всех одновременно проверяемых микросхемах, что не требует повторения контрольных тестов для восстановления информации, потерянной при замене дефектных микросхем. Это объясняется тем, что результаты сравнения запоминаются блоком 9, выходы которого соединены со входами элемента И 11, выполняющего функции оценки совпадения сигналов ошибок контроля, выход которого соединен со входом блока 4. В данном устройстве только при обнаружении ошибок в процессе выполнения контрольного теста во всех одновременно проверяемых микросхемах, т. е. при появлении единичных потенциалов на входах элемента И, с его выхода íà вход логического блока подается сигнал низкого уровня, си гнал изирующий о прекращении выполнения контрольного теста.

Блок 12 формирует сигнал на блокиров- аю ку поступающих на микросхемы входных воздействий и снятие с них питающего напряжения по сигналу «Пуск» устройства, что позволяет привести в исходное состояние блок 9 переп началом проверки и хранить контрольную информацию до начала проверки новой партии микросхем. Это дает возможность организовать процесс контроля оптимальным образом относительно временных затрат.

Формула изобретения

Устройство для функционального контроля микроэлектронных узлов, содержащее блок управления, первый управляющий вход которого соединен с выходом первого блока памяти, информационным входом формирователя адресов испытательных команд и первым информационным входом формирователя команд, тактовый вход — с первым выходом генератора импульсов, вход которого подключен к выходу пульта управления и входу первого блока памяти, выход блока управления соединен с управляющим входом формирователя адресов чспытательных команд и управляющим входом формирователя команд, выход формирователя адресов испытательных команд соединен с первым информационным входом согласующего блока, информационный выход которого соединен со вторым информационным входом формирователя команд, выходы которого соответственно соединены со входами блока оценки результатов контроля и вторым информационным входом согласующего блока, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит формирователь сигнала отключения питания объекта контроля, элемент И и второй блок питания, информационный вход которого .соединен с выходом блока оценки результатов контроля, управляющий вход — с управляющим выходом согласующего блока, выходы через элемент И вЂ” со вторым управляющим входом блока управления, а установочный вход — с выходом формирователя сигнала отключения питания объекта контроля, управляющий вход которого подключен к выходу пульта управления, а тактовый вход— ко второму выходу генератора импульсов.

Источники информации, принятые во внимание при экспертизе

1. Электроника М 23, 1973, с. 9 — 10.

2. Электронная промышленность, 1977, вып. 2, с. 20 — 24 (прототип).

809!85

Редактор И. Грузова

Заказ 18/59

Составитель И. Алексеев

Техред A. Бойкас Корректор H. Григорук

Тираж 756 Г1одписное

ВНИИПИ Государственного комитета СССР ло делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4