Вычислительная система

Иллюстрации

Показать всеРеферат

„„ 809194

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскин

Социалистических

Республик (6l) Дополнительное к авт. свид-ву № 533928 (22) Заявлено 01.06.79 (21) 2774930/18-24 с присоединением заявки №вЂ” (23) Приоритет—

Опубликовано 28.02.81. Бюллетень № 8

Дата опубликования описания 28.02.81 (51) М. Кл.

G 06 F 5/16

Гасударственный камитет

СССР (53) УДК 681 326 (088.8) на делам нзааретений и атнрытий (72) Авторы изобретения

В. A. Титов и В. М. Крикунов паты ап. тЕХН41ЧСМАМ " .п1Я !1т,, гт т... (71) Заявитель (54) ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА

Изобретение относится к вычислительной технике, может быть использовано для построения высокопроизводительных многомашинных вычислительных систем.

По основному авт. св. № 533928 известна вычислительная система, содержащая управляющую и N управляемых вычислительных магцин. М групп элементов И, дешифратор, регистр управления, коммутатор и регистр приращений, причем первый выход управляющей вычислительной машины соединен через регистр приращений с первым входом коммутатора, выход которого соединен со входом регистра управления, выход которого соединен со входом дешифратора, М выходы которого соединен соответственно с первыми входами элементов И М групп, второй и третий выходы управляющей вычислительной машины соединены соответственно с вторыми входами соответствующих элементов И каждой из М групп, выходы которых подключены соответственно к первым и вторым входам соответствующих управляемых вычислительных машин, первые выходы которых соединены со вторым выходом соответствующих элементов И М групп, выходами подключенных к первому входу управ2 ляющей вычислительной машины, четвертый выход которой соединен со вторым входом коммутатора f i ).

Недостаток этого устройства состоит в ограниченной области применения, что

5 обусловлено жесткой дисциплиной работы системы, согласно которой инициатором обмена может выступать только управляющая вычислительная машина.

Цель изобретения — расширение области применения системы.

1о Поставленная цель достигается тем, что

-в вычислительную систему введены группы элементов ИЛИ, элемент ИЛИ, дополнительная группа элементов И и М узлов формирования сигналов состояния, каждый из которых включает регистр состояния, ! триггер запроса, регистр приоритета, схему сравнения и группу элементов И, причем первый, второй и третий выходы i-той управляемой вычислительной машины соединены соответственно со входами регистра состояния, регистра приоритета и триггера запроса, выходы регистра состояний подключены к первым входам соответствующих элементов И i-го узла формирования сигналов состояния, вторые входы которых подключе809194 ны к первому выходу регистра приоритета, а третьи входы — к выходу схемы сравнения, первыЙ вход которой соединен со вторым выходом регистра приоритета, выход триггера запроса i-го узла формирования сигналов состояния соединен с i-vb> входом элемента ИЛИ, выход которого подключен ко второму входу управляющей вычислительной машины, выходы элементов И группы

i-го узла формирования сигналов состояния соединены с i-тыми входами соответствующих элементов ИЛИ группы, вторые входы схем сравнения узлов формирования сигналов состояния подключены к пятому выходу управляющей вычислительной машины, группа входов которой соединена с выходами элементов ИЛИ группы и первыми входами элементов И дополнительной группы, а шестой выход — со вторыми входами элементов

И дополнительной группы, выходы когорых подключены к группе входов регистра управления (i = 1, М).

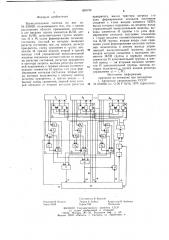

На чертеже представлена блок-схема. вычислительной системы.

Вычислительная система содержит регистра 1 прирашений, коммутатор 2, регистр

3 управления. дешифратор 4, М групп элементов 5 И (индексы обозначают номера управляемых вычислительных машин ВМ 6), узлы 7 формирования сигналов состояния, включающие регистр 8 состояния, триггер 9 запроса, регистр 10 приоритета, схему 11 сравнения и группу элементов 12 И, элемент !3 ИЛИ, группу элементов 14 ИЛИ, дополнительную группу элементов 15 И, первый 16, четвертый 17 выходы, первый вход !8, второй 19 и третий 20 выходы, второй вход 21, пятый выход 22, группу входов 23 и шестой выход 24 управляюшей вычислительной машины (УВМ) 25.

Устройство работает следующим образом.

В исходном положении триггеры 9 и триггеры регистров 8 находятся в нулевом состоянии, что свидетельствует об отсутствии запросов на обмен информацией со стороны

ВМ. На регистрах 10 находятся коды адресов ВМ. Эти коды указывают на приоритетность ВМ в системе.

Настройка управляющей ВМ вЂ” обмен информацией между УВМ 25 и ВМ 6 по инициативе управляющей ВМ вЂ” осушествляется следующим образом.

Команда настройки заносится в регистр 1 прирашений по выходу 16. Состояние регистра 1 определяет режим работы УВМ 25 с оперативной памятью ВМ системы и устанавливается управляющей ВМ по цепи 16.

Регистр 1 содержит несколько характерных участков, число которых зависит от количества различных причин (чтение операнда, запись результатов и других подобных обращений к оперативной памяти ВМ) . Информация о состоянии регистра 1 через коммутатор 2 в промежутки времени, определяюшие подачу управляющей ВМ разрешаюших сигналов по выходу 17, поступает на вход регистра 3. По состоянию регистра 3 дешифратор 4 на одном из выходов вырабатывает управляющий сигнал, по которому определяется номер ВМ. Код адреса обращения поступает на элементы 5 И по выходу 19 и далее в регистр адреса оперативной памяти только выбранной ВМ 6. Через элементы 7 по выходу 20 осуществляется передача синхронизирующих сигналов и управляюшей информации от УВМ к ВМ без нарушения процесса вычисления в них. Элементы 5 И обеспечивают обмен информацией при обращении ВМ по входу 18 управляющей ВМ 25.

Обмен информацией по инициативе одной

1О из ВМ производится следующим образом.

При окончании решения одной задачи или при другом виде запроса на обмен информацией сигнал о необходимости обмена посылается на триггер 9, который перебрасывается. в единичное состояние. З,алее сигнал о наличии запроса через элемент 13

ИЛИ поступает на вход 21 управляющеи

ВМ. Одновременно на регистр 8 от этой

ВМ поступает код операции обмена: решена го очередная задача, требования ввода — выво да информации, сигналы от системы контроля ВМ и др. На регистре !О постоянчо хранится код номера ВМ, причем этот код в процессе функционирования ВС может меняться управляющей ВМ (на чертеже цепи установки кодов от управляющей ВМ не показаны).

25 зо

Таким образом, в вычислительной системе обеспечивается параллельная работа

ВМ при гибкой организации управления, исключаются потери машинного времени, связанные С организацией двухстороннего обмена информации.

По сигналу с выхода элемента ИЛИ 13 о наличии запросов на обмен информацией от ВМ 6 управляющая ВМ опрашивает регистры 10 путем поочередной подачи по вь.ходу 22 на схемы 11 сравнения кодов

ЗS опроса, равных номерам ВМ в порядке vx приоритетности. При совпадении кода опроса, поступающего от управляющей ВМ, и номера (приоритета) ВМ с регистра 10 и при наличии требований обмена на регист40 ре 8 коды с регистров 8 и 10 через элементы 12 И и элементы 14 ИЛИ по входу 23 поступают на управляющую ВМ. которая анализирует информацию о запросе на обмен и принимает решение об изменении программы работы системы, записанной в регистре 1.

45 При этом управляюшая ВМ подает сигнал по выходу 24 на элементы 15 И, в результате чего коды с регистров 8 и 10 через элементы 12 И, элементы 14 ИЛИ и элементы 15 И поступают на регистр 3 управления. По этим кодам в дальнейшем обеспечивается обмен информацией между управляемой и управляющей ВМ по инициативе управляемой ВМ. мой ВМ.

809194

Форлцла изобретения

Составитель В. Вертлиб

Техред A. Бойкас Корректор Н. Бабинец

Тираж?56 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент>, г. Ужгород, ул. Проектная, 4

Редактор Н. Кешелг

Заказ 18/59

Вычислительная система по авт. св.

No 533928, отличающаяся тем, что, с целью расширения области применения системы, в 1ее введены группа элементов ИЛИ, элемент ИЛИ, дополнительная группа элементов И и М узлов формирования сигналов состояния, ка;::дый из которых включает регистр состояния, три;ер запроса, регистр приоритета, схему сравнения и группу элементов И, причем первый, второй и третий выходы i-той управляемой вычислительной машины соединены соответственно со входами регистра состояния, регистра приоритета и триггера запроса, выходы регистра состояний подключены к первым входам соответствующих элементов И группы i-ro узла формирования сигналов состояния, вторые входы которых подключены к первому выходу регистра приоритета, а третьи входы -- к выходу схемы сравнения, первый вход ксторой соединен со вторым выходом регистра приоритета, выход триггера запроса 1 ãî узла формирования сигналов состояния ссединен с г-тым входом элемента ИЛИ, выход которого подключе. ко второму входу управляющей вычислительной машины, выходы элементов И группы i-ro узла формирования сигналов состояния соединены с i-тыми входами соответствующих элементов ИЛИ группы, вторые входы схем сравнения узлов формирования сигналов состояния подключены к пятому выходу управляющей вычислительной машины, группа входов которой соединена с выходами элементов ИЛИ группы и первыми входами элементов И дополнительной группы, а шестой выход — са вторыми входами элемен15 тов И дополнительной группы, выходы которых подключен к группе входов регистра управления (i = 1, N}, Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

2ь Мо 533928, кл. (д 06 F 15/16, 1975 (прототип}.