Устройство для записи и считыванияинформации b блоке оперативнойпамяти

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советскик

Социалистических республик

< 809348, К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 170579 (23) 2766001/18-24 (51)М. Кл. сприсоединвнием заявки М

G 11 С 7/00

Госудврствеииый комитет

СССР ио делам июбретеиий и открытий (23) Приоритет. (53) УДК 681.З27 (088. 8) Опубликовано 28,0281. Бюллетень No 8

Дата опубликования описания 280281 (72) Авторы изобретвния

В.И. Пресников, В.И. Муравьев, М.С. Беляев и ГЯ,-,Суслов (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ЗАПИСИ И СЧИТЫВАНИЯ ИНФОРМАЦИИ

-В БЛОКЕ ОПЕРАТИВНОЙ ПАМЯТИ

Изобретение относится к запоминающим устройствам.

Известно устройство, в котором в .разрядную обмотку считывания-запрета подается двойной ток запрета (11 .

Недостатком этого устройства является двойное потребление разрядно- го тока.

Наиболее близким техническим ре- 10 шением к предлагаемому изобретению является устройство для записи и считывания информации из блоков памяти на магнитных сердечниках, содержащее ключ выбора секций разрядных обмоток, ключи чтения и записи и дифференци- т5 альный усилитель считывания (23.

Недостатком этого устройства является необходимость подавать удвоенное значение тока для записи информации, .что увеличивает потребляемую 20 мощность °

Цель изобретения — снижение потребляемой устройством мощности.

Поставленная цель достигается тем, что в устройство для записи и считывания информации в блоке оперативной памяти, содержащее усилитель считывания, ключ считывания, первый ключ запрета и ключи выбора разрядов, причем входы усилителя считывания и вы- 30 ход ключа считывания соединены соот-: ветственно с входами считывания и с выходом считывания устройства, первый вход и выход первого ключа запрета соединены соответственно с шиной питания и с первым выходом запрета устройства, входы и выходы ключей выбора разрядов соединены соответственно с шиной нулевого потенциала и с управляющими выходами устрой- ства, введены второй ключ запрета, дешифратор и формирователь разрядных импульсов, причем первый вход второго ключа запрета соединен Е первым входом первого ключа запрета, а выход — с вторым выходом запрета устройства, вторые входы ключей запрета соединены соответственно с первым и вторым выходами формирователя разрядных импульсов, первый, второй и третий входы которого подключены соответственно к выходу дешифратора и к управляющим входам устройства. При этом формирователь разрядных импульсов целесообразно выполнить содержащим элемент неравнозначность, два элемента И и элемент НЕ, причем выход элемента неравнозначность подключен к первому входу первого элемента И и входу элемента НЕ, выход кото809348 рого соединен с первым входом второго элемента И, первый и второй входы элемента неравнозначность, вторые входы и выходы элементов И подключены соответственно к первому, второму и третьему входам и к выходам формирователя разрядных импульсов.

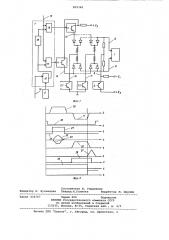

На фиг. 1 изображена принципиальная схема предлагаемого устройства, на фиг. 2 — временная диаграмма его работы. 10

Устройство содержит (фиг. 1) усилитель 1 считывания, ключ 2 считывания, первый 3 и второй 4 ключи запрета, ключи выбора разрядов 5.1 и 5.2, дешифратор 6, формирователь 7 разрядных импульсов, входы 8 и выход 9 считывания, управляющие выходы 10 и 11, первый 12 и второй 13 выходы запрета и управляющие входы 14 и 15.

Входы усилителя 1 считывания и выход ключа 2 считывания соединены 20 соответственно со входами 8 считывания и с выходом 9 считывания устройства. Первый вход и выход первого ключа 3 запрета соединены соответственно с шиной питания и. с первым выхо- 25 дом запрета 12 устройства. Входы и выходы ключей выбора разрядов 5.1 и 5.2 соединены. соответственно с шиной нулевого потенциала и с управляющими выходами 10 и 11 устройства. З0

Первый вход второго ключа 4 запрета соединен с первым входом первого ключа 3 запрета, а выход — со вторым выходом 13 запрета устройства. Вторые входы ключей запрета соединены соответственно с первым и вторым выходами формирователя 7 разрядных импульсов, первый, второй и третий входы которого подключены соответственно к выходу дешифратора б и к управляющим входам 14 и 15 устройства. 40

При этом формирователь 7 разрядных импульсов выполнен содержащим элемент 16 неравнозначность, первый 17 и второй 18 элементы И и элемент

19 НЕ. 45

Выход элемента 16 неравнозначность подключен к первому входу первого элемента 17 И и входу элемента 19 НЕ, выход которого соединен с первым входом второго элемента 18 И. 50

Первый и второй входы элемента 16 неравнозначность, вторые входы и выходы элементов И 17 и 18 подключены соответственно к первому, второму и третьему входам и к выходам формирователя 7 разрядных импульсов.

На фиг. 2 изображены временные диаграммы числового тока 20 считывания и тока 21 записи, напряжения 22 на управляющих выходах 10 и 11 устройства, низкий уровень 23 и высокий 60 уровень 24 напряжения на выходе 9 считывания устройства, временные .циаграммы считанных напряжений.25 на входах усилителя 1 считывания, тока

26 запрета, тока 27 в разрядной об- Я мотке, проходящей через невыбранные сердечники контролируемого блока оперативной памяти, напряжения 28 на управляющем входе 15 и напряжения 29 на управляющем входе 14 устройства.

Устройство работает следующим образом.

С приходом сигнала обращения к контролируемому блоку памяти в зависимости от выбираемого адреса открывается один из ключей выбора разрядов, например 5.1, который устанавливает низкий уровень напряжения 22 (фиг. 2) на объединенных концах полусекций разрядной обмотки блока памяти. Остальные ключи выбора разрядов закрыты и на объединенных .концах полусекций остальных разрядных обмоток будет высокий уровень напряжения, С выхода 9 считывания подается отрицательный потенциал 23, закрывающий диоды разрядных обмоток. После нарастания числового тока 20 считывания до номинального значения открывается ключ 2 считывания и на выходе 9 считывания устанавливается потенциал высокого уровня 24, который открывает диоды считывания избранной разрядной обмотки. При этом от источника питания через ключ 2 считывания, разрядную обмотку и ключ 5.1 выбора разряда протекает небольшой по величине ток смещения, в результате чего разрядная обмотка оказывается подключенной к входам усилителя 1 считывания, который усиливает наведенные в разрядной обмотке считанные импульсы напряжения 25 и подавляет синфазную помеху. С окончанием числового тока 20 считывания ключ 2 считывания закрывается и на выходе 9 считывания выдается отрицательный по.— тенциал 23, отключающий входы усилителя 1 считывания от помех с разрядной обмотки в такте записи информации.

При записи "1" в разрядную обмотку разрядный ток не подается. При записи "0" в первую полусекцию разрядной обмотки, проходящую через выбранный сердечник, подается ток 26 запрета (фиг. 2), а после окончания тока 21 записи во вторую полусекцию разрядной обмотки, проходящую через невыбранные сердечники, поступает импульс тока 27, который, после нарастания его до 75-1003 значения тока запрета, выключается. При записи дешифратор 6 в зависимости от адреса формирует низкий уровень напряжения, если выбранный сердечник находится в нечетной полусекции разрядной обмотки, или высокий уровень напряжения, если выбранный сердечник находится в четной полусекцни.

В первом случае с дешифратора 6 .на первый вход элемента 16 неравнозначность (фиг. 1) поступает низкий уровень напряжения, а на второй вход—

809348 высокий уровень напряжения с управляющего входа 14.

На вторые входы элементов И 17 и 18 подается высокий уровень напряжения с управляющего входа 15. Элемент 18 И формирует сигнал, открывающий первый ключ 3 запрета.

В момент выключения тока 21 записи (фиг. 2) на управляющий вход 14 поступает низкий уровень напряжения

29, в результате чего закрывается первый ключ 3 запрета (фиг. 1) и ® открывается второй ключ 4 запрета.

При этом в нечетной полусекции разрядной обмотки происходит спуд тока 26 запрета (фиг. 2), а в четной полусекции — формирование импульса 15 тока 27, после чего закрываются второй ключ 4 запрета и ключ выбора разряда 5.1.

Технико-экономическое преив4ущество предлагаемого устройства заключа- Щ ется в том, что при записи "0" ток saпрета подается только в одну полусекцию разрядной обмотки, а во. вторую— короткий импульс тока, за счет чего на 40% снижается потребляемая мощность.

Формула изобретения

1. Устройство для записи и считыва- о ния информации в блоке оперативной памяти, содержащее усилитель считывания, ключ считывания, первый ключ запрета и ключи выбора разрядов, при= чем входы усилителя считывания и выход ключа считывания соединены соответственно с входами считывания и с выходом считывания устройства, первый вход и выход первого ключа запрета соединены соответственно с шиной 4Q г питания и с первым выходом запрета устройства, входы и выходы ключей выбора разрядов соединены соответственно с шиной нулевого потенциала и с управляющими выходами устройства, о т л и ч а ю щ е е с я тем, что, с целью снижения потребляемой мощности, устройство содержит второй ключ запрета, дешифратор и формирователь разрядных импульсов, причем первый вход второго ключа запрета соединен с первым входом первого ключа запрета, а выход — с вторым выходом запрета устройства, вторые входы ключей запрета соединены -соответственно с первым и вторым выходами формирователя разрядных импульсов, первый, второй и третий входы которого подключены соответственно к выходу дешифратора и к управляющим входам устройства.

2. Устройство по п. 1, о т л и - . ч а ю щ е е с я тем, что формирователь разрядных импульсов содержит элемент неравнозначность, два элемента И и элемент НЕ, причем выход элемента неравнозначность подключен к первому входу первого элемента И и входу элемента НЕ, выход которого соединен с первым входом второго элемента И, первый и второй входы элемента неравнозначность, вторые входы и выходы элементов И подключены соответственно к первому, второму и третьЕму входам и к выходам формирователя разрядных импульсов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 337777887744, кл. G 11 C 11/02, 1973.

2. Авторское свидетельство СССР

9 523451, кл. G 11 С 7/00, 197б (прототип).

809348

Заказ 439/67

Тираж 656 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Составитель В. Гордонова

Редактор Н. Кузнецова Техред bl. oëèíêà Корректор M. Шарошн