Устройство для коммутации раз-рядных tokob b блоках памяти

Иллюстрации

Показать всеРеферат

Союз Советскнк

Социалистических

Республнк

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОИ:КОМУ СВИ ЕТЕЛЬСТВУ »809349 (61) Дополнительное к авт. саид-ау (22) Заяалено 2205.79 (?1) 2769683/18-24 с присоединением ааяеки Й9 (23)Приоритет

Опубликовано 2802.81.Бюллетень ИЯ 8

Дата опубликования описания 280231

{53)М. Кл.з

G 11 С 7/00

Гесударственяый кеинтет

СССР яо яслям из06РФТФинй я еткрытма

{53) УД К 681.327 (088. 8) 3 т г (72) Лвторы иаобретеиия

И.3. Арасланов и A.Ì. Цимерман (71) Заяеитель (54) УСТРОЙСТВО ДЛЯ КОММУТАЦИИ РАЭРЯДНЫХ ТОКОВ

В БЛОКАХ ПАМЯТИ

Изобретение относится.к запоминающим устройствам.

Известны устройства для коммутации разрядных токов в блоках памяти, одно из которых содержит формирователи разрядных токов, ключи разрядных токов, дискриминаторы сигналов считывания на каждый разряд с последующей коммутацией кодов lil.

Недостатком данного устройства.является большое количество дискриминаторов, что приводит к снижению точности измерения и удорожанию приборов.

Наиболее близким техническим решением к предлагаемому является устройствб для коммутации разрядных токов в блоках памяти, содержащее в качестве элементов коммутации ключи на биполярных и полевых транзисторах (23 .

Недостатком известного устройства является большое сопротивление открытого ключа и большая величина емкости закрытого ключа, что ставит в зависимость коэффициент передачи сигналов считывания устройством комму тации от величины и характера нагрузки на выходе устройства коммутации по цепи считывания, и, как следст- 30 вие, вызывает снижение точности измерения параметров сигналов считыва. ния с разрядной обмотки элементов магнитного запоминающего устройства, и, следовательно,.снижение надежности устройства.

Цель изобретения — повышение надежности устройства.

Поставленная цель достигается тем, что в устройство для коммутации разрядных токов в блоках памяти, содержащее формирователи-токов, блок считывания и .ключи, входы которых являются входами устройства, а выходы соединены с шиной нулевого потенциала, введены генератор импульсов тока, две, группы разделительных элементов н компенсатор; причем выходы формирователей токов подключены ко входу компенсатора н через разделительные элементы первой группы соединены с выходами устройства, которые через разделительные элементы второй группы подключены к одним из входов блока считывания, другой вход которого соединен с выходом компенсатора и выходом генератора импульсов тока, соединенного с шиной нулевого потенциала.

809349

При этом компенсатор выполнен в виде блока, содержащего диоды и параллельно соединенные резистор и конденсатор, причем одни электроды диодов подключены ко входам компенсатора, другие — к одному из выводов резистора, другой вывод которого соединен с выходом компенсатора.

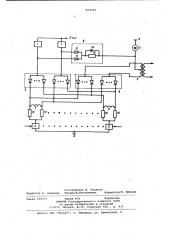

На чертеже изображена схема предлагаемого устройства.

Устройство содержит формирователи

1 токов, блок считывания, выполненный в виде трансформатора 2, ключи 3, шину 4 нулевого потенциала, первую 5 и вторую 6 группы разделительных элементов, например, выполненных в виде диодов, генератор 7 импульсов тока и компенсатор 8.

Выходы формирователей тока 1 подключены ко входу компенсатора 8 и через разделительные элементы первой группы 5 соединены с выходами устройства, которые через разделительные элементы второй группы б подклю чены к одним из входов трансформатора 2, другой вход которого соединен с выходом компенсатора 8 и выходом генератора 7, соединенного с шиной 4.

Выходы и входы устройства подключены к соответствующим разрядным обмоткам 9 и резисторам 10 блока памяти.

Компенсатор 8 содержит диоды 11 и 12 и параллельно соединенные резистор 13 и конденсатор 14, причем одни электроды диодов 11 и 12 подключены ко входам компенсатора 8, другие — к одному из выводов резис.тора 13, другой вывод которого соединен с выходом компенсатора. 8.

Устройство работает следующим образом.

При подаче сигнала управления на вход ключа 3 от генератора 7 через две половины первичной обмотки трансформатора 2, через диоды группы б и соответствующие резисторы 10 протекает ток включения пары диодов, тогда сигнал считывания с одной из разрядных обмоток 9 через малое дифференциалЬное сопротивление пары диодов группы б поступает на первичную рбмотку трансформатора 2. Разрядный ток от формирователей 1 протекае в зависимости от того, какой из двуй формирователей 1 вырабатывает импульсы разрядного тока, через диоды группы 5 и далее через Разрядиую обмотку 9, резисторы 10 и через открытый ключ 3.

Компенсатор 8 служит для компенсации изменения тока включения пары диодов группы б в момент формирования фронтов импульсов разрядных токов формирователями 1, что исключает . переходные процессы, связанные с изменением тока включения пары диодов.

Аналогично производится выбор других разрядных обмоток.

Использование изобретения позволяет повысить надежность устройства, сократить число дискриминаторов, аппаратуру измерения снгналов,и примерно на 10% увеличить выход годных из15 делий.

Формула изобретения

20 1. Устройство для коммутации разрядных токов в блоках памяти, содержащее формирователи токов, блок считывания и ключи, входы которых являются входами устройства, а выходы

25 соединены с шиной нулевого потенциала, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности устройства, оно содержит генератор импульсов тока, две группы разделительных элементов и компенсатор, причем вы ходы формирователей токов подключены ко входу компенсатора и через разделительные элементы первой группы соединены с выходами устройства, которые через разделительные элементы второй группы подключены к одним из входов блока считывания, другой вход которого соединен с выходом компенсатора и выходом генератора импульсов тока, соединенного с шиной нулевого

4О потенциала.

2. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что компенсатор содержит диоды и параллельно соединенные резистор и конденсатор, при45 чем одни электРоды диодоФ подключены ко входам компенсатора, другие— к одному из выводов резистора, другой вывод которого соединен с выходом компенсатора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 229606, кл. G 11 С 29/00, 1967.

2. Computer Oesign, 1967, 9 8, р. 49 (прототип).

809349

Тираж 656 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж 35, Раушская наб., д. 4/5

Заказ 439/67

Филиал ППП "Патент", r. ужгород, ул. Проектная, 4

Составитель В. Рудаков

Редактор A. Лежнина ТехредЖ.Костелевич Корре р екто М. Шароши