Блок выборки адресов запоминающегоустройства

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

И АВТОРСКОМУ СВ ТИЛЬСТВУ

СОюз Сеаетских

Сециалистическиз

Республик

«i509357 (61) Дааолиительное к авт. свмд-ву— (22) Заявлено 050279 (21) 2722294/18-24 с присоедмиением заявки М(23) Г1риоритет— (51)М. Кл.з

6 11 С 8/00

Государственный комитет

СССР ио аелаи изобретений и открытий

Опубликсеано 280281, Бюллетень М 8

Дата опубликования описания 280281 (53) УДК 681. 327..66(088.8) P2) Авторы изобретения

Л.В. Бучкин и Л.Г. Червякова (71) Заявитель (54) ВЛОК ВЫБОРКИ АДРЕСОВ ЗАПОМИНАЮЩЕГО

УССР ОИСТВА

Изобретение относится к вычисли- " ; тельной технике и может быть использовано в устройствах отображения алфавитно-цифровой информации на экране

ЭЛТ (дисплеях), применяющихся в каче» стве буферного эапоьвтнакщего устрой- . ства (Зу) с произвольным доступои.

Известно устройство отображения, .в которои преобразование кода адреса 1© экрана в адрес буферного ЗУ peanwseвано по классическому способу "дешифраТор — шифратор". В состав блока вы- бора адресов такого устройства входит счетчик позиций, счетчик строк, один многоступенчатый дешифратор, шифратор,И регистр адреса ЗУ (Ц .

Недостатками такого устройства являются большие затраты оборудования, необходимого для построения двшифрато«26 ра и шифратора, многоступенчатость схема преобразователя и, как следствие этого, значительные задержки адресных сигналов при прохождении через эту схему, большое число связей между элементами и связанная с ним сложность их реализации печатным монтажом, а также значительная мощность, потребляемая блоком выбора адресов от источников питания. 30

Известно также устройство содержащее счетчик позиций, счетчик строк, дешифраторы младших разрядов счетчи- ков позиций и строк, дешифраторы старших разрядов счетчиков позиций и строк н регистр адреса f2).

Наиболее близким по технической сущности к предлагаемому является блок yapaaeesss выбором адресов sanoжнашщего устройства, в состав которого входят счетчик позиций, счетчик строк и регистр адреса ЗУ t3).

Однако для адресации ЗУ требуется введение в устройство дополнительного несинхронизированного реверсивного счетчика адреса ЗУ и схем, управляющих его работой; значительная и непостоянная задержка форыерования адреса, зависящая от исходного и требуемого адреса, что создает серьезные неудобства при построении таких синхронных устройств, как дисплей.

Цель изобретения — упрощение устройства.

Поставленная цель достигается тем, что в блок выборки адресов запоминающего устройства, содержащий счетчик позиций, счетчик строк и регистр, введен преобразователь кодов, входы которого соответственно подсоединены

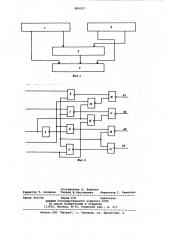

809 357 к выходам старших разрядов счетчиков позиций и строк, выходы преобразователя кодов соединены с первыми входами регистра, вторые входы которого подключены к выходам младших разрядов счетчиков позиций и строк соответственно, а также тем, что преобразователь кодов содержит элементы И-НЕ

1и элемент НЕ, вход которого соединен с первым входом преобразователя кодов, выход элемента НЕ соединен с одними из входов первого, второго, третьего 1 ,и четвертого элементов И-НЕ, другие входы которых соединены со вторыми входами преобразователя кодов, выходы первого, второго, третьего и четвертого элементов И-НЕ соответственно подклю- 15 чены к одним из входов пятого, шестого, седьмого и восьмого элементов ,:И-НЕ, выходы которых соединены с выхо дами преобразователя кодов, другие входы пятого и шестого элементов И-НЕ щ соединены с выходами девятого и де сятого элементов И-НЕ соответственно, другие входы седьмого и восьмого элементов И-НЕ подключены к выходу элемента НЕ, вход которого соединен с одними из входов девятого и десятого .элементов И-НЕ, другие входы которых подсоединены соответственно к другим входам третьего и четвертого элементов И-НЕ °

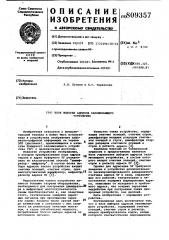

На фиг. 1 изображена функциональ30 ная схема блока выборки адресов запоминающего устройства," на фиг. 2функциональная схема преобразователя кодов.

Блок выборки адресов запоминающего устройства содержит счетчик 1 позиций, счетчик 2 строк, преобразователь 3 кодов, регистр 4 °

Преобразователь кодов содержит элемент 5 НЕ и элементы 6-15 И-HE. 4()

Блок работает следующим образом.

Обозначим количество позиций сим-. волов в строка алфавитно-цифрового дисплея через М, а количество строк на экране через Н. Предположим, что 45 числа М и N состоят из двух сомножителей, один из которых является степенью числа 2, а второй соответственно равен 5 и 3; т. е.

М 2а 5 5О

N 2 3, где а и Ь вЂ” любые числа натурального ряда, кроме нуля, т. е. а, Ь =1, 2,.

3, Очевидно, что число разрядов в счетчике 1 позиций равно (4+3) . Соответственно число разрядов в счетчике

2 строк равно (Ь+2). Общее количество разрядов в коде позиции экрана равно а+3+Ь+2 = а+Ь+5.

Количество знакомест на экране, à 40 соответственно и емкость буферной памяти, необходимой для хранения отоб ражаемой на экране информации равно

H -М. Поскольку числа и и M не являются степенью числа 2, то и их произве- 45 дение также не является степенью числа 2, т.е. 2"

2 415 ° 2О"J 2 . Отсюда Х=а+Ь+4.

Поскольку формат адреса экрана (а+Ь+5) не соответствует формату адреса буферной памяти (а+Ь+4), требуется преобразовать код адреса экрана в код адреса буферной памяти. Так

Мак входной код является избыточным, то при преобразовании его можно минимизировать. Так как а и Ь вЂ” степени числа 2, то в этих разрядах входного кода избыточности нет. СЛедовательно, минимизировать преобразователь 3 за счет этих разрядов невозможно.

Значит младшие разряды а счетчика 1 позиций и падшие разряды b счетчика 2 строк можно подать в регистр 4 буферной памяти без преобразования, т.е. разряды а и Ь входного кода являются составной частью разрядов х выходного кода. Остается преобразовать пять разрядов в четыре разряда. Для. этого. старшие три разряда счетчика 1 позиций и старшие два разряда счетчика 2 строк подаются на вход преобразователя 3, с выхода которого четыре преобразованных разряда поступают в регистр 4 адреса буферной памяти.

ПреобразователЬ работает следующим образом.

Так как разряды (а+1)-(а+3) принимают пять состояний (от 0 до 4), а разряды (b+1) и (Ь+2) - три состояния (от 0 до 2), то можно записать таблицу состояний для данного преобразователя:

Входные коды

Выходные коды

a+7 (а+2 (а+з) ь+Г ь+2 я, я,(я, "я

Поскольку распределение адресов в памяти может быть произвольным, то таблица строится по принципу максиMansioN похожести кодов. Если во входномраэряде (a+3) логический "0" то разряды (а+1), (а+2), (Ь+1) н (Ь+2) повторяются в выходных разрядах 4х, . 4 и А . На элементе 5 осущегтнч ется

0 0 0

1 0 0

0 10 0

1 1 0

0 0 1

0 0 0

1 0 0

0 1 0

1 1 0

0 0 1

0 0 0

1 0 0

0 1 0

1 1 0

0 . 0 1

0

0

1

1

1

0

0

0 0

0 1

0 о0

0 1

0 0

0 0

0 г

0 0

0 1

0 1

1 0

1 1

1 0

1 1

1 0

0 0 0

0 0 0

1 0 0

1 0 0

0 1 1

0 1 0

0 1 0

1 1 0

1 1 0

0 1 1

0 0 1

0 0 1

1 0 1

1 0 1

1 1 1

809357

Формула изобретения

1. Блок выборки адресов запоминающего устройства, содержащий счетчик позиций, счетчик строк.и регистр, отличающийся тем, что, с целью упрсщения устройства, в него введен преобразователь кодов, входы которого соответственно подсоединены к выходам старших разрядов счетчиков позиций и строк, выходы преобразователя кодов соединены с первыми входами регистра, вторые входы которого подключены к выходам младших разрядов счетчиков позиций и строк соответственно.

2. Блок по и. 1, отличаюшийся тем, что преобразователь кодов содержит элементы И-НЕ и элемент НЕ, вход которого соединен с первым входом преобразователя кодов, вы ход элемента НЕ соединен с одними из входов первого, второго, третьего и четвертого элементов И-НЕ, другие входы которых соединены со вторыми входами преобразователя кодов, выМоды первого, второго, третьего и четвертого элементов И-НЕ соответственно подключены к одним иэ входов

;пятого, шестбго, седьмого и восьмого элементов И-НЕ, выходы которых соеди» иены с выходами преобразователя кодов, другие входы пятого и шестого элементов И-НЕ соединены с выходами девятого и десятого элементов И-НЕ соответственно, другие входы седьмого и восУмого элементов И-НЕ подключены к выходу элемента НЕ, вход которого соединен с одними иэ входов девятого и десятого элементов И-НЕ, другие входы которых подсоединены соответственно к другим входам третьего и четверI того элементов И-НЕ. инвертирование разряда (а+3), и если в нем логический "О.", то он разрешает прохождение разрядов (а+!), (а+2), (Ь+1) и (Ь+2) через элементы

6-9, выходы которых соединены со входами элементов 10-13 И-НЕ, осуществлякших функцию НЕ-ИЛИ. Йэ таблицы видно, что после этого остается преобразовать только те коды (3 кода), в разряде (a+3) которых содержится

"1". В выходных разрядах А и А4 этих кодов всегда логическая "1". Для ® реализации этого выходы элемента 5

HE соединены со входами элементов 12 . и 13 И-НЕ, осуществляющих функцию

НЕ-ИЛИ для разрядов АЗ и А . Разря; ды же А и А»повторяют состояние раз- »5 рядов (Ь+1) и (Ь+2). Для этого вход разряда (а+3) соединен со входами элементов 14 и 15 И-НЕ, реализующих функцию И-НЕ, на другие входы которых поданы разряды (Ь+1) и (Ь+2). Выходы ;щ элементов 14 и 15 И-НЕ соединены со входами элементов 10 и 11 И-НЕ, осуществлякщих функцию НЕ-ИЛИ для разрядов Aq и А2.

При таком преобразовании распреде- ление адресов в памяти получается произвольным, но выполняется основное условие, необходимое для работы алфавитно-цифрового дисплея! каждой позиции экрана однозначно соответствует вполне определенный адрес буферной памяти.

Предлагаемый блок применен в устрой,стве Отображения алфавитно-цифровой информации на ЭЛТ EC-7927 с форматом экрана 24 строки по 80 символов. Ем- ;З кость экрана 24 ° 80=1920 символов.

Разрядность счетчика позиций 1-7, раз-, рядность счетчика строк 1-5. Таким образом, разрядность кода позиции экрана (входного кода преобразовате- 49 ля) равна 12. Разрядность регистра 4 адреса буферной памяти на 1920 символов (выходного кода преобразователя ) равна 11 (2 o c 1920с 2 " ) .

Так как 80 16 5, а 24=8 3, то четыре младших разряда кода позиции и три младших разряда кода строки, осуществляющих пересчет соответственно до 16 и до 8, можно не преобразовывать. Остается преобразовать три старших разряда счетчика позиций и два старших разряда счетчика 2 строк.

То есть вместо преобразования 12-разрядного кода в 11-разрядный, что при использовании элементов серии К155 требует примерно 35-40 микросхем, преобразуется 5-разрядный код в 4-разрядный, что на элементах той же серии требует для осевой реализации примерно 3 микросхе»и.

Использование предлагаемого блока д@ в составе дисплея EC-7927, внедряемо

ro в настоящее время в серийное производство, позволяет уменьшить его стоимость и повысить надежность благодаря существенному уменьшению объема оборудования. Кроме того, он по-. требляет меньшую мсщность от источника питания по сравнению с известным.

При преобразовании кода адресов по выаеуказанному принципу уменьшается формирование адреса памяти, что облегчает построение таких синхронных устройств, как дисплей.

Источники информации, принятые во внимание при экспертизе

1. Т3атейт C0IA В 3440646, кл. 340347, опублик. 1969.

2. Патент США В 3540031, кл. 340324, опублик. 1970.

3. Патент США 9 3514761, кл. 340172,5, опублик. 1970.(прототип).

809357

Рис. 1

Pgr. 2

СостаВИтель A. Воронин

Редактор Т. Алякина Техред Ж.Кастелевич Корректор Г. Реиетник

Заказ 440/68 Тираж 656 Подписное

ВНИИПК Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4