Буферное запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОИ:КОМУ Св ОИЛЬСТВУ

«i509358 (61) Дополнительное к авт. саид-ву (22) Заявлено 310579 (21) 2773641/18-24

{51)М. Кл.

6 11 С 9/00 с присоединением заявки ¹â€”

Государстмнный комнтет

СССР яо делам нзобретеннй н открытн Й (23) Приоритет

Опубликовано 280281, бюллетень Н9 8

{53) УДК 681. 327 (088.8) Дата опубликования описания 280281 (72) Авторы изобретения

В. В. Дементьев, Г.М. Ефимов, Л.Я. Новосельцев и В. Г. Чернолесскнй

Ленинградский ордена Ленина электротехнический институт нм. В.И. Ульянова (Ленина) . .—.... (71) Заявмтель (54 ) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к запоминающим устройствам.

Известно устройство, которое содержит блок памяти, информационнйй вход которого соединен с источником информации, информационный выход соединен с приемником информации, счетчик адреса, выход которого соединен с адресным входом блока памяти и уст- ройство управления, первый выход которого соединен с управлякххнм входом блока памяти, а второй, третий и четвертый выходы соединены соответственно с первым, вторым и третьим входами счетчика адреса Pg.

Недостатком этого устройства является то, что порядок выдачи информации из устройства обратен порядку по- ступления информации на его вход.

Наиболее близким по техническому решению к предлагаемому является буферное запоминающее устройство, содержащее блок памяти, первый регистр адреса, хранящий н указывающий номер ячейки блока памяти, из которой извлекается информация, второй регистр адреса, хранящий и указывающий номер ячейки блока памяти, в которую помещается инФормация (21. 30

Недостатком этого устройства является низкое быстродействие при больших скоростях поступления информации на его вход, так как в этом устройстве операции записи информации, модиФикации адреса и сравнения адресов выполняются последовательно.

Цель изобретения - повьааение быстродействия буферного запоминающего устройства.

Поставленная цель достигается тем, что в буферное запоминающее устройство, содержащее первый накопитель, блок управления и два счетчика, при- . чем информационные вход и выход первого накопителя соединены с информационными входом и выходом устройства соответственно, а первые и вторые входы и выходы блока управлениясоответственно с первая и вторыми аходамн и выходами устройства, первый и второй адресные входы и первый адресный и третий выходы блока управления подключены соответственно к выходу первого счетчика, к выходу второго счетчика, к адресному н к управляющему входам первого накопителя, первые входы первого и второго счетчиков соединены с четвертым выходом ,блока управления, а вторые входы пер809358 вого и второго счетчиков — соответственно с пятым и шестым выходами блока управления, введены второй нако-. питель, третий, четвертый и пятый счетчики, дешифратор и два элемента

ИЛИ, причем первые входы третьего, четвертого и пятого счетчиков подключены к четвертому выходу блока управления, а вторые входы третьего и четвертого. счетчиков - соответственно к седьмому и восьмому входам блока управления, первые входы первого и второго элементов ИЛИ соединены соответственно со вторыми входами первого и второго счетчиков, а вторые входы — соответственно со вторыми входами. третьего и четвертого счетчиков, выходы первого и второго элементов

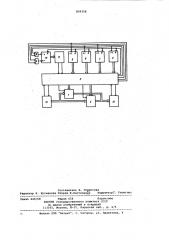

ИЛИ подключены соответственно ко второму и третьему входам пятого счетчика, выход. которого подключен ко входу дешифратора, первый и второй вы- Щ ходы которого и выходы третьего и четвертого счетчиков соединены соответственно с третьим и четвертым входами и с третьим и четвертым адресными входами блока управления, адресный 5 и управляющий входы второго накопителя подключены соответственно ко второму адресному и девятому выходам блока управления,-а информационные вход и выход второго накопителя — соответственно к информационным входу и выходу первого накопителя, На чертеже приведена структурная схема предлагаемого устройства.

Устройство содержит первый 1 и второй 2 накопители, первый 3 и второй 4 элементы ИЛИ, блок 5 Управле-. ния, первый б, второй 7, третий 8, четвертый 9 и пятый 10 счетчики и дешифратор 11., Информационные вход и выход перво- 40 го накопителя -1 соединены .с информационными входом и выходом устройства соответственно. Первые и вторые входи и и выходы блока 5 управления подключены соответственно к первым и вторым 45 входам и выходам устройства.

Первый и второй адресные входи и первый адресный и третий выходы блока 5 управления соединены соответст-. венно с выходом первого счетчика 6, с выходом второго счетчика 7, с адресным и с управлянхцим входами первого накопителя 1. Первые входы первого

6 щ второго 7 счетчиков соединены с четвертым выходом блока 5 управления, а вторые входы первого 6 и второго 7 счетчиков — соответственно с пятым и шестым выходами блока 5 управления.

Первые входы третьего 8„четвертого 9 и пятого 10 счетчиков подключены к четвертому выходу блока 5 управления, 40 а вторые входы третьего 8 и четвертого 9 счетчиков — соответственно к седьмому и восьмому входам блока 5 управления. Первые входы первого 3 н второго 4 элементов ИЛИ соединены 5 соответственно со вторыми входами первого б и второго 7 счетчиков, а вторые входы — соответственно со вторыми входами третьего 8 и четвертого 9 счетчиков, выходы первого 3 и второго 4 элементов ИЛИ подключены соответственно ко второму и третьему входам пятого счетчика 10. Выход которого подключен ко входу дешифратора 11. Первый и второй выходы дешифратора 11 и выходы третьего 8 и четвертого 9 счетчиков соединены соответственно с третьим и четвертым входами и с третьим и с четвертым адресными входами блока 5 управления. Адресный и управляющий входы второго накопителя 2 подключены соответственно ко второму адресному и девятому выходам блока управления 5, а информационные вход и выход второго накопителя 2 соответственно к информационным входу. и выходу первого накопителя 1. Первые вход и выход и информационный вход устройства соединяются с соответствующими выходами и входом источника ин-. формации 12. Вторые вход и выход и информационный выход устройства подключаются к соответствующим входам и выходу приемника информации 13.

Устройство работает следующим образом.

В исходном состоянии блок 5 управления вырабатывает ситнал на четвертом выходе и устанавливает в нулевое состояние все пять счетчиков 6-10.

Дешифратор 11 дешифрирует нулевое со-.. стояние пятого счетчика 10 и формирует на четвертом входе блока 5 управления осведомительный сигнал "Буферное запоминающее устройство свободно". Устройство будет оставаться в этом состоянии до тех пор, пока на входе не появится информация. В этом случае источник информации 12 возбудит первый вход блока 5 управления.

Блок 5 управления подключит выход второго счетчика 7 к адресному вх<щу первого накопителя 1, а выход четвертого счетчика 9 .- ко входу второго накопителя 2 и таким образом подготовит устройство к приему информации.

Первое слово входной информации будет помещено в первый накопитель 1, в ячейку с адресом "0" путем подачи на его управляющий вход импульса

"Запись", одновременно содержимое четвертого счетчика 9 и пятого счетчика 10 будет увеличено на "1". Второе слово информации будет помещено во второй накопитель 2, в ячейку с адресом "1" путем подачи на его управляющий вход импульса "Запись", одно.— временно содержимое второго счетчи ка 7 и пятого счетчика 10 будет увеличено на "1". Третье слово информации будет помещено в первый накопитель

1, в ячейку с адресом "1", четвертое - во второй накопитель 2, в ячейку с адресом "3" и т.д. Входной про809358

Формула изобретения

55 цесс будет продолжаться до тех пор, пока источник информации 12 не прекратит выдачу информации, либо пока не будут заполнены накопители 1 и 2.

В последнем случае на втором выходе дешифратора будет сформирован сиг- 5 нал "Занято". После окончания входного процесса через блок 5 управления подключен к адресному входу накопителя 1 выход первого счетчика б, а к адресному входу второго накопителя - . о выход третьего .счетчика 8. Затем бу- дет происходить считывание информации из устройства и выдача ее потребителю. Сначала блок 5 управления сформирует сигнал считывания на входе первого накопителя 1 и одновременно выдаст сигнал увеличения содержимого третьего счетчика 8 и уменьшения содержимого пятого счетчика 10 на "1".

При этом первое слово информации из первого накопителя 1 из ячейки памя- 20 ти "0" будет выдано потребителю. Затем будет сформирован сигнал считывания на входе второго накопителя и одновременно сигнал увеличения содержимого первого счетчика б и уменьше- 25 ния содержимого пятого счетчика 10 на " 1". В результате будет считано второе слово информации из второго накопителя 2 иэ ячейки-памяти "1".

Таким образом, выходной процесс бу- З дет продолжаться до тех пор, пока не будет выдана вся информация иэ накопителей 1 и 2, и на первом выходе дешифратора 11 не будет сформирован осведомительный сигнал ""Свободно", либо пока источник информации 12 не выдаст очередной массив информации.

Во втором случае выходной процесс будет прерван и устройство перейдет в состояние приема информации.

Технико-экономическое преимущество 40 предлагаемого устройства заключается в том, что в нем длительность цикла записи информации уменьшена в три раза по сравнению с известным устрой-. ством, что существенно повышает быстродействие буферного запоминающего устройства.

Буферное запоминающее устройство, содержащее первый накопитель, блок управления и два счетчика, причем информационные вход и выход первого накопителя соединены с информационными входом и выходом устройстна соответственно, а первые и вторые входы и выходы блока управления — соответственно с первыми и вторыми входами и выходами устройства, первый и второй адресные входы и первый адресный и третий выходы блока управления подключены соответственно к выходу первого счетчика, к выходу второго счетчика, к адресному и к управляющему входам первого накопителя, первые входы первого и второго счетчиков соединены с четвертым выходом блока управления, а вторые входы первого и второго счетчиков — соответственно с пятым и шестым выходами блока управления, отличающееся тем, что; с целью повыаения быстродействия устройства, оно содержит второй накопитель, третий, четвертый и пятый счетчики, дешифратор и два элемента

ИЛИ, причем первые входы третьего, четвертого и пятого счетчиков подключены к четвертому выходу блока управления, а вторые входы третьего и четвертого счетчиков - соответственно к седьмому и восьмому входам блока управления, первые входы первого и второго элементов ИЛИ соединены соответственно со вторыми входами первого и второго счетчиков, а вторые входы — соответственно со вторыми входами третьего и четвертого счетчиков, выходы первого и -второго элементов

ИЛИ подключены соответственно ко второму и третьему входам пятого счетчика, выход которого подключен ко входу дешифратора, первый и второй выходы которого и выходы третьего и четвертого счетчиков соединены соответственно с третьим и четвертым входами и с третьим и четвертым адресными входами блока управления, адресный и управляющий входы второго накопителя подключены соответственно ко второму адресному и девятому выходам блока управления, а информационные вход и выход второго накопителя — соответственно к информационным входу и выходу первого накопителя.

Источники информации, принятые во внимание при экспертизе

1. Майоров С.A. и Новиков Г.И.

Принципы органиэации цифровых машин.

Л., Машиностроение, l974, с.388.

2. Патент Японии Р 30982, кл. 97/7/С, опублик. 1976 (прототип).

809358

Составитель В..Гордонова

Редактор Н. Кузнецова Техред Ж. Кастелевич КорректорГ. Реыетник

Заказ 440/68 Тираж 656 П од пи с кое

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4