Запоминающее устройство

Иллюстрации

Показать всеРеферат

Сазов Советских

Сов иалмстмческик

Ресеублик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОИ:КОНУ ИЛЬСТВУ

<щ809364 (6т ) Дополнительное к авт. саид-ву— . (22) Заявлено 040679 (23) 2765654/18-24 с присоединением заявки М— (23) Приоритет(51)М. Кл З

G 11 С 11/00

Гесударственный квинтет

СССР нв дмаи изобретений и открытий (3) 4К 681. 327. .-6(088.8) Опубликовано 28p 281 бюллетень Н9 8

Ф

Датаопубликования описания 280281 (7! ) Заявитель (54 ) ЗАПОНКИ)ф)Щ :) уСурОеСу8О

Изобретение относится к запоминающим устройствам.

Одно нз известных запоминающих устройств содержит числовой блох, координатные ключи Х и Ч для выборки требуемой числовой линейки, общий формирователь адресного тока, выходные усилители сигналов считывания со стробированием. Все блоки управляются и синхронизируются от общего блока местного управления.

8 этом устройстве считанные с числового блока сигналы "1" и "0" отличаются только по амплитуде, но ие ло фазе. Выходные сигналы "1" представляют собой импульсы определенной амплитуды и полярности. Запоминаюв ее устройство этого типа имеет значительные преимущества перед другими типами по количеству используемого оберу- ® дования и потребляемой мощности Я .

Однако устройство менее помехоустойчиво и надежно из-за наличия по-. мех в фазе с полезными сигналами из-за усложнения схем числового блока и выходных усилителей. Для различения сигналов "0" и "1" приходится применять амплитудные селекторы, пороговые .схеме и специальные сиесты стробирования, однако это не всегда приводит к желаемем резальтатам. Особенно усложняются схемы для устройств, работающих в широком диапазоне механических и климатических воздействий, и при ,изменении напряжений источников пита.ния.

Наиболее близким техническим решением к предлагаемому изобретению является устройство, которое содержит числовой блок, усилители считывания, блок управления, ключи Х и Ч и адресные форьмрователи, а также разрядные формирователи, регистры адреса и чис à Г2).

Однако в этом устройстве в результате наличия паразитных индуктивностей, емкостей и полувыбранных сердечников сигнал "0" представляет собой не отсутствие импульса, а импульс в фазе с полезным сигналам "1", что может привести к искажению считываемой информации-фиксации сигнала "1" вместо сигнала "0".

Это уменьшает помехоустойчивость и снижает надежность устройства.

Цель изобретения — повышение надежности устройства.

Поставленная цель достигается тем, что в запоькнающее устройство, содержащее накопитель, соединенный с ключа809364 ми, формирователь адресного тока, усилителн считывания и блок управления, одни из выходов которого подключены к управляющим входам ключей, формирователя адресного тока и усилителей. считывания, введены селектор, форми- рователь сигналов компенсации помех, блок местного управления, элемент задержки, блок сопряжения, усилитель сигналов компенсации помех, элемент . памяти сигналов компенсации помех, сумматоры, элементы связи и элементы

И и ИЛИ, причем первый вход блока местного управления подключен к первому выходу формирователя адресного тока, второй выход которого соединен с входом селектора, выходы которого подключены соответственно к,первому входу первого элемента И и входам одних из ключей, выход блока местного управления соединен с первым входом элемента ИЛИ, второй вход которого подключен к выходу второго элемента

И, вход элемента задержки соединен с выходом первого элемента И, а выход — с первым входом формирователя сигналов компенсации помех, второй вход которого подключен к выходу элемента ИЛИ, а выходы соединены с входами блока сопряжения, одни из выходов которого подключены к входам усилителя сигналов компенсации помех, выход которого соединен с входом элемента памяти сигналов компенсации помех, выходы которого подключены соответственно к первому входу второго элемента И и входу блока управления, другие выходы блока сопря30

2S

35 жения через элементы связи соединены с одними из входов сумматоров, другие входы которых подключены к выходам накопителя, а выходы - к входам усилителей считывания, вторые входы блока местного управления, элементов

И и управляющий вход блока сопряже40 ния соединены с другими выходами блока управления.

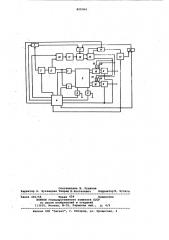

На чертеже изображена структурная схема запоминающего устройства.

Устройство содержит ключи 1 Х, 45 ключи 2 У, накопитель 3, блок. 4 управления, формирователь 5 адресного е . тока, усилители 6 считывания, блок 7 местного управления, элемент 8 ИЛИ, селектор 9, служащий для выделения сигналов компенсации помех, первый элемент 10 И, элемент 11 задержки, формирователь 12 сигналов компенсации помех, блок 13 сопряжения, усилитель 14 сигналов компенсации помех, элементы 15 связи, выполненные, например в виде резисторов, сумматоры 16, элемент 17 памяти сигналов компенсации помех и второй элемент 40

18 И.

Первый вход блока 7 подключен к первому выходу формирователя 5, вто рой выход которого соединен с входом селектора 9, выходы которого подключены соответственно к первому входу элемента 10 И и входам ключей 1. Выход блока 7 соединен с первым входом элемента 8 ИЛИ, второй вход которого подключен к выходу элемента 18 И.

Вход элемента 11 задержки соединен с выходом элемента 10 И, а выход— с первым входом формирователя 12, второй вход которого подключен к выходу элемента 8 ИЛИ, а выходы соединены с входами блока 13, одни из выходов которого подключены к входам усилителя 14, выход которого соединен с входом элемента 17 памяти, выходы которого подключены соответственно к первому входу элемента 18 И и входу блока .4, другие выходы блока 13 через резисторы 15 соединены с одними из входов сумматоров 16, другие входы которых подключены к выходам накопителя 3, а выходы - к входам усилителей 6. Вторые входы блока 7, элементов И 10 и 18 и управляющий вход блока 13 соединены с выходами блока 4.

Устройство работает следующим образом.

При считывании выбранного числа из накопителя 3 по сигналам блока 4 управления, срабатывают один ключ 1 Х и один ключ 2 Y. После этого формирователь 5 адресного тока выдает импульс тока спроса, который протекает по выбранной числовой линейке накопителя 3 и через некоторое время на выходах накопителя 3 появляются сигналы

"1" и "0" выбранного числа. С селектора 9 при наличии разрешающего сигнала с блока 4 управления импульс тока опроса передается. через первый элемент 10 И на элемент 11 задержки, с помощью которого можно регулировать время поступления сигнала компенсации на сумматоры 16. Из импульса тока опроса формирователь 12 формйрует сигнал компенсации, который через блок 13 сопряжения и резисторы 15 подается на входы сумматоров 16 (для каждого разряда). Сигнал компенсации в формирователе 12 может регулироваться по амплитуде и длительности с помощью блока 7 по сигналам с формирователя 5 адресных токов и блока 4 управления. На сумматорах 16 выбранного числа происходит алгебраическое сложение считанных из накопителя 3 сигналов "1" и "0" и сигнала компенсации, в результате чего формируются противоположные по фазе сигналы

"1" и ™О" и производится подавление .имеющихся в запоминающем устройстве помех. Эти суммарные сигналы поступают на соответствующие входы усилите.лей 6, где они усиливаются до необходимого уровня и стробнруются по сиг налам с блока 4 управления. Для осуществления замкнутой обратной связи и поддержании сигнала компенсации на необходимом уровне служит цепочка бло309364 ка 13 сопряжения, усилитель 14, элемент 17 памяти, второй элемент 18 И элеиент 8 ИЛИ, формирователь 12. Наличие сигнала компенсации. контролируется блоком 4 управления по сигналу элемента 17 памяти.

Таким образом, подбирая необходимую амплитуду, длительность и время появления сигнала компенсации, можно обеспечить заданные параметры выходных сигналов "1" и "0" на входе ycu)0 лителей воспроизведения.

Использование предлагаемого запоьынающего устройства с введенным в него селектором, блоком местного управления, элементом задержки, формирователем сигналов компенсации помех, бло-15 ком сопряжения, усилителем сигналов компенсации помех, элементом памяти, сумматорами, элементами связи, двумя элементами Й и одним элементом ИЛИ, позволяющими подавить возникающие в 2О запоминающем устройстве помехи и получить фазовое различение выходных сигналов "1" и "0", выгодно отличает его от существующих запоминающих устройств, так как значительно упрощают- 5 ся блоки усиления и выделения сигналов, упрощаются схемы их временного стробирования и расширяются пределы работоспособности устройств. Все это значительно упрощает проектирование и конструирование запоминающего устройства, уменьшение время его отладки и повышает его надежность.

Формула изобретения

Запоминающее устройство,-содержа;щее накопитель, соединенный с ключами, формирователь адресного тока, усилители считывания и блок управления, одни из выходов которого подключены к управляющим входам ключей, формирователя адресного тока и усилителей считывания, о т л и ч а ю щ е е с я тем, что, с целью повыаения надежнос-ф5 ти устройства, оно содержит селектор, формирователь сигналов компенсации помех, блок местного управления, элемент задержки, блок сопряжения, усилитель сигналов коипенсации помех, элемент памяти сигналов компенсации помех, сумматоры, элементы связи и элементы И И ИЛИ, причем первый вход блока местного управления подключен к первому выходу формирователя, адресного тока, второй выход которого соединен с входом селектора, выходы ко горого подключены соответственно к дервому входу первого элемента И и входам одних из ключей, выход блока честного управления соединен с перрым входом элемента ИЛИ, второй вход которого подключен к выходу второго .клемента И, вход элемента задержки соединен с выходом первого элемента

И, а выход — с первым входом формирователя сигналов компенсации помех, второй вход которого подключен к выходу элемента ИЛИ, а выходы соединены с входами блока сопряжения, одни из выходов которого подключены к sxoдам усилителя сигналов кс мпеисации помех, выход которого соединен с входом элемента памяти сигналов компенсации помех, выходы которого подключены соответственно к .первому входу второго элемента И и входу блока управления, другие выходы блока сопряже. ния через элементы связи соединены c одними из входов сумматоров, другие входы которых подключены к выходам накопителя, а выходы - к входам усилителей считывания, вторые входы блока местного управления, элементов И и управляющий вход блока Сопряжения соединены с другими выходами блока уп равления.

Источники информацииi принятые во внимание при экспертизе

1. Брик Е.A. Техника постояннйх запоминающих устройств. М., "Советское радио", 1973, с. 51-62.

2.шигин A.Ð. и Дерюгин A.À. Нифро. вые вычислительные машины. М., "Энер гия", 1975, с. 33-37 (прототип).

809364

Составитель В.. Рудаков

Редактор H. Кузнецова Техред Ж. Костелевнч Корректор В. Вутяга заказ 440/68 Тираж 656 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП "Патент", r. Ужгород, ул. Проектная, 4