Запоминающее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОУСКОМУ СВИ ЕТЕЛЬСТВУ (6! ) Дополнительное к авт. саид-by (51)М. Кл 3

G 11 С 11/00 (22) Заявлено 17.05,79 (2!) 2768673/18-24 с присоединением заявки HP(23) П иоритетГесуаарствениыЯ комнтет

СССР.

IIo асави нЗОбрстсииЯ я аткрытиЯ р

Опубликовано 280281.Бюллетень )49 8 (53) УДК 681, З27.

;6 (088.8) Дата опубликования описания 280281

P2) Авторы изобретения

Р

1 l

"ф

И.В. Огнев, Ю.И. Шамаев и Н.И. Дикарев

5 (Иосковский ордена Ленина энергетический:. институт .4" З" а *;;., (73) Заявитель (54) злпоиинлющее устРОЯство

Изобретение относится х запоминаю- щим устройствам.

Известны запоминакицие устройства (ЗУ), одно из которых содержит двух проводную матрицу ферритовых,сердеч.ников, блок возбуждения адресных ли. ний, дешифратор разрядных линий, формирователь разрядного тока, схему коммутации сигналов, усилитель считаю- Е вания. Разрядные линии матрицы подключаются через дешифратор разрядных линий к формирователю тока м через схему коммутации сигналов к усилителю считывания попарно по мостовой схеме f1) .

IS

Недостатком известного ЗУ является большая потребляемая мощность и .большой объем оборудования в схеме дешифратора разрядных линий, которые обусловлены необходимостью воэбужде- 20 ния одновременно двух разрядных линий.

Наиболее близким техническим решением к предлагаемому является запоми« веющее устройство, содержащее двухпроводную матрицу ферритовых сердечников, Ьлок возбуждения адресных линий, формирователь разрядного тока, усилитель считывания; причем вход усилителя считывания соединен с вы- 30 ходом фс рмирователя разрядного тока и входом деввтфратора разрядных линий f2) .

Недостатком данного устройства является малое быстродействие и невысокая надежность работы нэ-за большой амплитуды помехи на входе усклителл считываиил, которая представляет собой падение напрлмения на разрядной линии м на дешмфраторе разрядных линий кри протекании через ннх тока возбуждения. Длл подавления помехи s. качестве входного каскада усилителя считывания используется спецмалъная схема - схема подавления помехи типа

"пьедестал, пркчем для подавления помехи с большой амплитудой требуется значительное время, что приводит

К потере быстродействия Зу, и увеличивается помеха на выходе,схемы подавления помехи, что скижает .надежность работы ЗУ.

Цель иэОбретенмя - повышение быстродействил и надежности работы ЗУ за счет увелмчения отношения сигнала и помехе ка входе усилителя считывания.

Укаэанная цель достигается тем, что в запоькнакщее устройство, содержащее двухпроводную запоминающую матВ

809 365 рицу на феррнтоных сердечниках, адресные шины которой подключены к. адресному блоку, одни концы Разрядных шин соединены со входами первого дешифратора, а другиe — с выходами вто рого дешифратора, вход которого подключен к выходу формирователя тока, соединенного с шиной нулевого потенциала, И усилитель считывания, введены интегратор, дифференциальный усилитель, источник опорного напряжения и датчик напряжения, причем входы дифференциального усилителя подключены соответственно к одному из выводов датчика напряжения, соединенному с выходом первого дешифратора, и одному иэ вйводов источника опорного на- !5 пряжения, другие выводы которых соединены с шиной нулевого потенциала, выход дифференциального усилителя подключен ко входу усилителя считывания и входу интегратора,. выход которого соединен с управляющим входом формирователя тока.

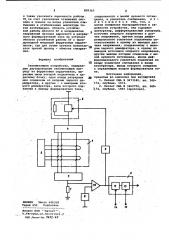

Иа чертеже изображена структурная схема запоминакщего устройства.

Устройство содержит двухпроводную запоминающую матрицу 1 на ферритоных сердечниках, адресный блок 2, служащий для возбуждения адресных шин матрицы 1, перный 3 и второй 4 дешифраторы, служащие для нозбужденид разрядных шин матрицы 1, формирователь 5 тока, выполненный в виде гене" ратора тока с малым выходным сопротивлением, усилитель б .считывания, датчик напряжения, например резистор 7, источник 8 опорного напряжения, интегратор .9, дифференциальный усилитель 10, шину 11 нулевого потенциала, Усилитель 6 считывания содержит схему 12 подавления помехи типа

"пьедестал", в качестве которой мо- 40 .жет быть использован дифференцирующий элемент с управляемой постоянной времени дифференцирования, и усилитель 13 с амплитудным дискриминато. ром с временным селектором. На вход

14 усилителя б считывания, подается сигнал управления величиной постоянной времени дифференцирования, на вход 15 - сигнал управления временным селектором.

Входы усилителя 10 подключены к О одному иэ выводов резистора 7, соединенному с выходом дешифратора 3, и одному из выводов источника 8, другие выводы которых соединены с шиной 11. Выход усилителя 10 подключен Ы ко входу усилителя 6 и входу интегратора 9,> выход которого соединен с управляющим входом формирователя 5, выход которого подключен ко входу дешифратора 4. 60

ЗУ в такте чтения работает следующим образом, В исходном состоянии блок 2 и дешифраторы 3 и 4 закрыты и тока ни в адресных, ни s разрядных, шинах неч 65

На вход .14 подают высокий уровень, что соответствует малой постоянной времени дифференцирования и схеме 12 подавления помехи, на вход 15 усилителя 13 с временным селектором подают .низкий логический уровень, блокирующий прохождение информации на выход усилителя 6 считывания.

Сначала возбуждаются дешифраторы

3 и 4 и начинается процесс нарастания тока н выбранной разрядной шине. Падение напряжения на резисторе 7 при протекании через него разрядного тока сравнивается на дифференциальном усилителе 10 с напряжением источника 8. Усиленная разность этих двух напряжений с выхода дифференциального усилителя 10 поступает на вход интегратора 9. Напряжение на выходе интегратора 9, поданное на управляющие вход формирователя 5 тока, за счет действия отрицательной обратной связи стремится к такой величине, при которой выходной ток формирователя 5 тока ранен номинальномч значению разрядного тока, а падение напряжения на измерительном резисторе 7 равно напряжению источника 8, и только тогда изменение напряжения на ныходе интегратора 9 прекращается, По окон- -. чании переходного процесса установления разрядного тока запускается блок 2. Сумма адресного и разрядного тока, действукщая на выбранный сердечник в матрице 1, приводит к изменению его индукции и на разрядной шине наводится ЭДС, величина которой зависит от хранящейся в сердечнике информации. ЭДС сердечника вызывает отклонение разрядного тока от номи» нального значения и эа счет действия обратной связи в формирователе 5 тока происходит процесс, направленный на устранение этого отклонения. При этом на выходе дифференциального усилителя 10 появляется сигнал, близкий по форме к дифференциалу от ЭДС сердечника, Резко увеличивая постоянную времени дифференцирования в схеме 12 подавления помехи путем подачи низкого логического уровня на вход 14, на выходе схемы подавления помехи получают сигнал, полярность которого определяется хранимой н опрашиваемом сердечнике информацией. Этот сигнал поступает на вход усилителя 13 с амплитудным дискриминатором и временным селектором и одновременно на вход 15 подается высокий логический уровень, разрешающий прохождение информации на выход усилителя б считывания °

Применение изобретения позволяет значительно повысить быстродействие двухпроводного ЭУ типа 2,50 за счет уменьшения. интервала времени между подачей разрядного и адресного токов возбуждения и необходнмога для подавления помехи от разрядного тока, 809365

Формула изобретения

ВНИИПИ

Тираж 656 а также увеличить надежность работы, ЗУ эа счет увеличения отношения сигнала и помехи на входе усилителя.считывания и стабилизации амплитуды токов возбуждения. Область устойчивой работы данного ЗУ в координатах напряжений питания адресного и разрядного формирователей тока не уступает области устойчивой работы ЗУ с трехпроводной матрицей ферри овых сердечников; где для съема сигнала испольэу-1 ется третий провод — обмотка считыва. ния.!

Запоминакзцее устройство, содержащее двухпроводную эапомннаишую матрицу на ферритовых сердечниках, адресные шины которой подключены к адресному блоку, одни концы разрядных Щ шин соединены со входами первого де,шифратора, а другие — с выходами вто рого дешифратора, вход которого подключен к выходу формирователя тока, Филиал ППП Патент, ! г. ужгород, ул, Проек тна я, 4 ппп,патенг эак. 2622- 65

6 соединенного с шиной нулевого потен-. циала, и усилитель, считывания, о т;л и ч а ю щ е е с я тем, что, с целью повышения быстродействия и на.дежности устройства, оно содержит интегратор, дифференциальный усилитель, источник. опорного напряжения и датчик напряжения, причем входы дифференциального усилителя псщключены соответственно к одному .из выводов датчика напряжения, соединенному с выходом первого деаифратора, и одному иэ выводов источника опорного напряжения, другие выводы которых соединены с шиной нулевого потенциала, выход дифференциального усилителя подключен ко входу усилителя считывания и входу интегратора, выход которого соединен с управляющим входом формирователя тока.

Источники информации, принятые во внимание при экспертизе

1. Патент СВ!А Ю 3673580, кл. 340;174, опублик. 1972.

2. Патент QdA 9 3462750, кл. 340 174, опублнк. 1969 (прототип).