Постоянное запоминающее устрой-ctbo c автономным контролем

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ С ТЙУ (61) Дополнительное к ввт. сеид-еу(22) Заявлено 2505.79 (23 } 2770417/18-24

Сеюз Советских

Сециелистических

Республик

< ц809366 (я)М. КЛ.3

G 11 С 11/00 с присоединением звлвки H9—

Государственный коинтет

СССР но ямам нзобретеннй н открытнй (23) Приоритет—

Опубликовано 280281, веоллетеиь l49 8

Дата опубликования описания 280281 (Щ >ДК 681. 327 (088;8) (72) Авторы изобретения

Г.A. Бородин, В.И. Константиновский, Л .A и Л.В. Лемуткин (71) Заявитель (54) ПОСТОЯННОЕ ЗАПОИИНАОЩЕЕ УСТРОЙСТВО С АВТОНОИНЫИ

КОНТРОЛЕМ

Изобретение относится к запоминаЮщим устройствам. .Известно постоянное запоминающее устройство с автономным контролем, со-е держащее блок памяти, регистры адреса и числа, распределитель имптульсов и блок регистров начальной установки $1J .

Недостатком этого устройства явля- 1,, ется низкая надежность.

Наиболее близким техническим решением к предлагаемому изобретению является устройство, содержащее основной и дополнительный блоки памяти, рЕгистры адреса и числа, распределитель 1з импульсов и регистр обмена 2(.

Недостаток этого устройства - -невозможность обеспечения контроля за количеством циклов перезаписи, что снижает надежность контроля.

26

Цель изобретения - повышение надежности устройства.

Поставленная цель достигается тем, что в постоянное запоминающее устройство с автономным контролем, содердащее блоки памяти, дешифраторы, регистр адреса, регистр циклов перезаписи, компаратор и блск управления, :причем входы устройства соединены со входами регистра адреса, один из выI ходов которого подключен ко входам первого дешифратора, а другие выходы - к адресным входам первого блока памяти, входам второго дешиф- . ратора и адресным входам второго блока памяти, числовые входы которого соединены с числовыми входами и с выходами первого блока памяти, выходы первого дешифратора подключены соответственно к управляющим входам первого блока памяти, выходы регистра циклов перезаписи соединены с первым входом компаратора, управляющие вход и выход которого, управляющие входы регистра адреса, второго блока памяти и регистра циклов перезаписи и стробирующие входы первого и второго дешифратора подключены к соответствующим выходам и входу блока управления, введены счетчик, мультиплексор и селектор, первый выход которого соединен со вторым входом компаратора и выходом счетчика, а второй вход - с выходом второго дешифратора и управлякщим входом мультиплексора, выход которого подключен к установочному входу счетчика, счетный вход которого соединен с соответствующим выходом блока управления, выход селектора подключен к контроли809366 руемому входу первого блока памяти, контрольный выход которого соединен с информационным входом мультиплексора.

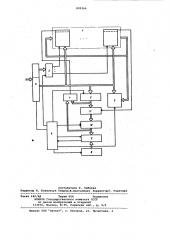

На чертеже изображена функциональная схема предлагаемого устройства.

Устройство содержит первый 1 и второй 2 блоки памяти, первый дешифратор 3, регистр 4 адреса, второй дешифратор 5, блок 6 управления, селектор 7, регистр 8 циклов перезаписи, компаратор 9, счетчик 10 и мультиплексор 11.

Входы устройства соединены со входами регистра 4 адреса, одни из выходов которого подключены ко входам первого дешифратора 3, а другие выходы - к адресным входам первого блока 1 памяти, входам второго дешифратора 5 и адресным входам второго блока 2 памяти. Числовые входы второго блока 2 памяти соединены с числовыми входами и с выходами первого блока 1 2О памяти. Выходы первого дешифратора 3 подключены соответственно. к управляющим входам первого блока 1 памяти.

Выходы регистра 8 циклов перезаписи соединены с первым входом компарато- 25 ра 9. Управляющие вход и выход которого, управляющие входы регистра 4 адреса, второго блока 2 памяти, регистра 8 циклов перезаписи и стробирующне входы первого 3 и второго 5 дешифра- ® тора подключены к соответствующим выходам и входу блока 6 управления. Пер-. вый выход селектора 7 соединен со вторым входом компаратора 9 и выходами счетчика 10, а второй вход — с выходом второго дешифратора 5 и управляющим входом мультиплексора 11, выходом подключенный к установочному входу счетчика 10, счетный вход которого соединен с соответствующим выходом блока 6 управления. Выход селектора 40

7 подключен к контрольному входу первого блока 1 памяти, контрольный выход которого соединен с информацион« ным входом мультиплексора 11.

Первый блок 1 памяти построен на 4 интегральных запоминающих микросхемах, объединенных в сегменты. Каждый сегмент содержит определенное количество ячеек памяти, минимальный объем памяти сегмента определяется сте- О пенью интеграции микросхемы. Каждый сегмент имеет дополнительный информационный разряд, который используется как контрольный.

Устройство работает следующим образом.

При изменении информации в устройстве в каком-либо из сегментов блока 1 памяти информации иэ этого сегмента переписывается во второй блок 2 памяти, изменяется в нем и затем переза- ЬО писывается в тот же сегмент блока 1 памяти. Таким образом выполняется цикл перезаписи информации в устройстве.

Для безотказной работы устройства количество циклов перезаписи информа- Я ции в одной запоминающей микросхеме не должно превышать максимально допустимого значения. Поскольку смена информации в различных сегментах блока 1 памяти происходит хаотически, необходимо контролировать количество перезаписи информации для каждого сегмента, чтобы заранее определить

Момент возможного выхода его из строя.

Контроль количеством циклов перезаписи выполняется следующим образом.

При поступлении команды изменения информации в устройстве на вход старших разрядов регистра 4 адреса поступает код адреса сегмента первого блока 1 памяти, который дешифрируется в первом дешифраторе 3 и поступает на управляющий вход первого блока 1 памяти, в котором выбирается сегмент по этому адресу. Путем перебора адресов., поступающих с младших разрядов регистра 4 адреса, происходит одновременно выбор адресов ячеек в выбранном сегменте первого блока 1 памяти, во втором блоке 2 памяти и втором дешифраторе 5. Информация иэ выбранных ячеек первого блока 1 памяти поступает на числовой вход второго блока 2 памяти и записывается в него по соответствующим адресам. При этом одновременно с контрольного выхода первого блока 1 памяти на вход мультиплексора 11 поступает контрольный код, содержащий информацию о количестве циклов перезаписи. Из мультиплексора 11, управляемого вторым дешифратором 5, контрольный код записывается в счетчик 10 и затем, по команде из блока 6 управления, сравнивается компаратором 9 с контрольным числом, хранящимся в регистре 8 циклов перезаписи. Если количество циклов перезаписи не превышает максимально допустимого значения, то по сигналу из блока управления 6 в счетчике 10 к контрольному коду добавляется единица.

Во втором блоке 2 памяти происходит смена информации, после чего новая информация и контрольный код, увеличенный на единицу, одновременно перезаписываются в выбранный ранее сегмент первого блока 1 памяти.

Информация записывается в ячейки сегмента, определяете путем перебора адресов в младших разрядах регистра 4 адреса. Контрольный код из счетчика

10 через селектор 12 под управлением второго дешифратора передается на контрольный вход первого блока 1 памяти и записывается контрольный разряд этого же сегмента. На этом цикл изменения информации в устройстве эаканчивается. При каждом следующем цикле смены информации в сегменте информация о количестве циклов переэаписИ, хранящаяся в его контрольном разряде, увеличивается на единицу. Когда количество циклов перезаписи в этом сегменте достигает максимально допусти809366 мого значения, контрольный код, считываемый иэ этого сегмента, равен контрольному числу, хранящемуся в регистре 8 циклов перезаписи, после чего необходимо заменить сегмент в первом блоке 1 памяти, так как его дальнейшая надежная работа не гарантирована.

Адрес этого сегмента определяется значением старших разрядов регистра 4 адреса.

Технико-экономическое преимущество предлагаемого устройства заключается в том, что в нем выполняется автономный контроль эа количеством циклов перезаписи информации в каждом иэ сегментов постоянного блока памяти и указывается адрес сегмента, отрабо- 13 тавшего свой ресурс, что позволяет оперативно определять место возможного отказа в постоянном блоке памяти и предотвратить отказ, эа счет чего повышается надежность устройства. ;р

Формула изобретения

Постоянное запоминающее устройство с автономным контролем, содержащее блоки памяти, дешифраторы, регистр адреса, регистр циклов. перезаписи, компаратор и блок управления, причем входы устройства соединены со входами регистра адреса, один из выходов 36 которого подключен ко входам первого дешифратора, а другие выходы - к адресным входам первого блока памяти, входам второго дешифратора и адресным входам второго блока памяти, чис-33 ловые входы которого соединены с числовыми входами и с выходами первого блока памяти, выходы первого дешифратора подключены соответственно к управлякищим входам первого блока памяти, выходы регистра циклов перезапи- си соединены с первым входом компаратора, управляющие вход и выход которого, управляющие входы регистра адреса, второго блока памяти и регистра циклов перезаписи и стробирующие входы первого и второго дешифраторов подключены к соответствукщим выходам и входу блока управления, о тл и ч а ю щ е е с я тем, что, с целью повышения надежности устройства, оно содержит счетчик, мультиплексор и селектор, первый вход которого соединен со вторым входом компаратора и выходом счетчика, а второй вход — с выходом второго дешифратора и управляющим-входом мультиплексора, выход которого подключен к установочному входу счетчика, счетный вход которого соединен с соответствующим выходом блока управления, выход селектора подключен к контрольному входу первого блока памяти, контрольный выход которого соединен с информационным входом мультиплексора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 489107, кл. G 06 V 11/00, 1973.

2. Авторское свидетельство СССР

М 630630 кл. G 11 С 29/00, 1976 (прототип).

8093бб

Составитель Т. Зайцева

Редактор И. Ковальчук Техред Ж.Кастелевич КорректорГ. Решетник

Закаэ 440/68 Тираж 656 Подписное

ВНИИПИ Государственного комитета СССР по делам иэооретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Уигород, ул. Проектная, 4