Запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Социаанстнческнк

Рк публик

ОПИСАНИЕ

ИЗОВРЕТЕНИЯ

К АВТОИЖОМУ С ЕТИЛЬСТВУ

«о809367 (61) Дополнительное к авт. сеид-ву(22) Заявлено 28057/ (21) 2770674/18-24 с присоединением заявки H9— (53)M. Кл.з

G 11 С 11/00

ГосударстненныЯ комитет

СССР но делаю нзобретеннй н открытнА (23) ПриоритетОпубликовано 280281 Бюллетень Й9 8 (53) УДК 681. З27. .66 (088.8) Дата опубликования описания 280281 (72) Авторы изобретения

О.A. Григорьев и A Ã. Фролов (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к устройствам для записи информации в электрических цифровых накопителях к может быть использовано в вычислительнОй технике и системах обработки и хранЕ-. ния информации.

Известно запоминающее устройство с линейной выборкой информации, с разрядными шинами, включенными по симметричной мостовой схеме,и содержащее дкодный адресный коммутатор, управляеьий двумя дешифраторами, при этом половина адресных обмоток и соответствующих им диодов, подключенных к любому ключу дешифратора связана с разрядными обмотками, включенными в одно плечо мостовой схема, а вторая половина адресных обмоток и диодов, подключенных к этому ключу, связана с разрядными обмотками, включенными в противоположное плечо мостовой схемы p) .

В устройстве компенсируются помеобусловленные паразитными емкостями запертых диодов адресного коммутатора и емкостями между адресными и разрядными обмотками.

Однако в этом устройстве не устраняются выбросы на переднем фронте н спад вершины адресных импульсов, вызванные реактивностями адресных обмоток, что препятствует повыценкю быстродействия и информационного объема известного устройства.

Наиболее близким к изобретению по технической сущности является запоминающее устройство, которое содержит накопитель с линейной выборкой информации с разрядными обмотками, включенными. по симметричной балансной схеме и диодный адресный коммутатор, выходы которого соединены с соответствующими выходами управляемого дешифратора, содержащего две группы ключей, при этом один из адресных,об,моток накопителя и соответствующие им диоды коммутатора, подключенные к одному из ключей дешифратора связаны индуктнвно с одними иэ плеч разрядных обмоток, а другие адресные обмотки и соответствуккцие им диоды коммутатора, подключенные к этому же ключу дешифратора связаны индуктивно с другими плечами разрядных обмоток (27 .

В известном устройстве также компенсируются помехи, обусловленные паразитными емкостями запертых диодов адресного коммутатора и емкостями между адресными и разрядными обмотками.

809367

Но в известном устройстве, использующем единый формировате.|ь импульсов тока, который прерывает работу в со-. ответствии с обращением к запоминаю-. ,щему устройству, не устраняются выбросы на переднем фронте и спад вершины импульсов адресного тока, свя,занные с режимом насыцения транзисторов формирователя и ключей, а также с возникновением противо-ЭДС индукции адресных обмоток, что снижает быстродействие устройства, так как для устранения выбросов необходимо формировать импульсы с пологими фронтами, что приводит к увеличению времени обращения. Но и в этом случае фронт импульса тока должен оставаться дьс-, 15 таточно крутым (например, при использовании в качестве запоминающего элемента цилиндрических магнитных пленок, длительность фронта должна быть ь, а30-60 нс). Спад вершины непосред- 20 ственно связан с увеличением времени перемагничивания, что также приводит к увеличению времени обращения. Низкое быстродействие, в свою очередь, является преградой к увеличению ин- 25 формационной емкости накопителя. В известном устройстве для устранения указанных недостатков не используется энергия питания формирователя и ключей, так как нет возможности пере- ЗО распределения тока, например из адресных цепей в разрядные во время формирования импульсов адресного тока.

Цель изобретения - повышение быст- З5 .родействия,устройства. Поставленная цель достигается тем, что в запоминающее устройство, содержащее накопитель, одним из выводов адресныХ обмолвок которого соединены через диады адресного коммутатора с 40 выходами первых ключей, другие выводы адресных обмоток подсоединены к выходам вторых ключей, разрядные обмотки накопителя, включенные совместно с первичными обмотками развязываю- 45 щих трансформаторов и блоком форми,рования разрядного тока по балансной схеме, блок управления, первые выходы которого соединены с одним иэ входов первых и вторых ключей, второй выход блока управления подключен к ому иэ входов блока формирования р зрядного тока, третий выход блока у авления соединен с одним из входов блока считывания, и основной источник питания, выходы которого соедииены с другими входами блока формирования разрядного тока, блока считывания и накопителя, введен стабилизатор тока, дополнительный источник питания .и блок распределения тока, выход ко- 40 торого соединен с другими входами первых ключей, выход стабилизатора то. ка подсоединен к другим входам вторых ключей и к первому входу блока распределения тока, второй и третий входы которых соответственно соединены с шинами основного источника питания, вход стабилизатора тока подключен к первому выходу дополнительного источника питания, второй выход которого соединен с одним из выходов основного источника питания, а также тем, что блок распределения тока содержит корректирующий кондейсатор, два стабилитрона, токозадающий резистор и согласовывающий конденсатор, одна из обкладок которого подсоедине-. на к катоду первого стабилитрона и выходу блока распределения тока, а через токозадающий резистор,к катоду второго стабилитрона, к одйой из обкладок корректирующего конденсатора и к первому входу блока распределения тока, аноды стабилитронов подключены ко второму входу блока распределения тока, третий вход которого соединен с другими обкладками конденсаторов.

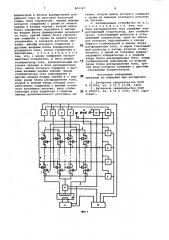

На фиг. 1 изображена функциональная схема устройства; на фиг. 2 электрическая схема блока распределения тока и стабилизатора тока.

Запоминающее устройство содержит адресные обмотки 1, диоды 2, адресные шины 3 и 4, ключи 5 и 6, разрядные обмотки 7 и 8, блок 9 формирования разрядного тока, развязывающие трансформаторы 10, блок 11 считывания, блок 12 управления, шины 13 и

14 основного источника питания, выходы 15 и 16 дополнительного источника питания, стабилизатор 17 тока и блок 18 распределения тока, состоящий иэ корректирующего конденсатора

19, стабилитронов 20 и 21 и сглаживающего конденсатора 22.

Стабилизатор тока содержит транзистор 23, резистор 24 обратной связи, стабилитрон 25 и резистор 26 смещения, Устройство работает следующим образом.

Когда ключи 6 и 5 разомкнуты, ток из шины 15 дополнительного источника питания (например 0 6 =+27В) протекает через транзистор 23 и резистор 24 обратной связи стабилизатора 17 тока (фиг. 2), образуя напряжение обратной связи, которое (при изменении напряжения дополнительного ксточника питания либо нагрузки на выходе стабилизатора 17 тока) воздействует на .транзистор 23 и величина тока, протекающего через него, практически не изменяется. Далее ток протекает через стабилитроны 21 и 20 блока 18 и утилизируется в цепях питания блоков 9, 11.

Стабилитрон 20, эашунтированный конденсатором 22, образует источник стабилизированного напряжения. Это на-. пряжение подается к ключам 5 и является напряжением смещения. Таким образом, в случае, когда адрес не выбран, транзистор 23 стабилизатора то809367 ка 17 находится в активном режиме, рабочая точка его поддерживается постоянной и стабилизированный ток используется для питания блоков разрядного управления.

При выборе адреса блок 12 управления подает на входы ключей 6 и 5 импульсы управления, открывается один из ключей 6 и один иэ ключей 5, последний фронт импульса адресного тока формируется в момент включения ключа 5, заданный фронт — ключа 6. При включении ключа 5, напряжение на адресной обмотке 1 ниже напряжения на стабилнтроне 21 блока 18 (фиг. 2), но выше напряжения основного источника постоянного тока например 0, =

=+5В). Стабилитрон 21 закрыт. К адресной обмотке 1 прикладывается напряжение U>Ug)+U(g и быстро нарастает ток с крутым фронтом (например

t+ 40нс) . амплитуда импульса адрес- 20 ного тока обеспечивается стабильной, благодаря каскаду с общей базой на транзисторе 23 и нелинейной обратной связью стабилизатора 17 тока. Выбросы на переднем фронте импульса отсут- Я5 ствуют, так как до включения ключа 5 транзистор 23 стабилизатора 17 тока находился в активном режиме и рабочая точка транзистора на выходной характеристике поддерживается постоянной. Конденсатор 19 блока 18 служит для коррекции частотной характеристи-. ки и также устраняет спад вершины импульса адреоного тока. В момент времени, когда ключ 6 закрывается, иапря- 5 жение на адресной обмотке 1 снижается, но оно будет больше напряжения на шине 13 основного источника постоянного тока, т.е. 0 >0 3 и ток иэ шины 13 не сможет затекать через стабилитрон 21 в адресную обмотку 1, ®

Сформированный таисии образом импульс адресного тока замыкается через диод 2 (фиг. 1), который расположен на пересечении адресных шин 3 и 4, связанных с выбранными ключами 6 4 и 5. При этом все остальные диоды 2 заперты. Ток помехи при открывании ключей б и 5 и возбуждении адресной обмотки 1, обусловленный паразитными емкост"ии диодов 2 " емкостями $0 между адресными обмотками 1 и разрядными 7, 8, растекается симметрично по плечам балансной мостовой схЕвы и компенсируется в трансформаторах 10

H блоке 11 считывания После того, как ключ 6 закроется, ток на выходе стабилизатора 17 поддерживается неизменным и вызывает резкое увеличение напряжения на стабилитроне 21 блрка 18, что приводит к его пробою и протеканию в цепи питания блоков 9, 10 60

Таким образом, в основе технического решения заложен принцип перераспределения тока, благодаря чему транзистор 23 стабилизатора 17 всегда находится в активном режиме, и его 61 рабочая точка на выходной характеристике поддерживается постоянной. Этим устраняются выбросы на переднем фронте импульса адресного тока, спад вершины н обеспечивается высокое качество стабилизации, что повышает быстро- действие устройства и исключает необходимость формировать импульсы с пологими фронтами в отличие от. известных схем, где работа стабилизатора или формирователя тока прерывается, и в начальный момент включения транзисторы этих устройств насыщаются, что приводит к появлению выбросов на переднем фронте импульсов.

После того, как ключ 6 закроется адресиая обмотка 1 стремится сохранить неизменным адресный ток, поэтому возможны броски напряженйя, для устранения которых и увеличения скорости спада заднего фронта импульса адресного тока могут быть применены известные способы, например при помощи дополнительных диодов и ключа. Ключи 5 и б, блоки 9 и 11 могут быть выполнены, в интегральном исполнении на микросхемах серии 169, трансформаторы 10на базе малогабаритных импульсных трансформаторов типа БТИ-118, транзистор 23 стабилизатора 17 — типа

2Т904. Стабилитроны 20, 21 — типа

Д815.

Использование новых элементов дополнительного источника питания, ста-. билизатора тока и блока распределения тока повышает быстродействие устройства за счет сокращения длительности переднего фронта и устранения выбросов и спада вершины импульсов адресного тока путем перераспределения тока стабилизатора при помощи устройства управления. Возможность утилизации части тока стабилизатора в цепи питания блоков разрядного управления позволяет уменьшить мощность рассеивания. Предложенное техническое решение не требует разработки специальных узлов, поэтому его применение в народном хозяйстве не вызывает необходимою. ти разработки новой элементной базы.

Предлагаемое изобретение принципиально не усложняет структурную схему запоминающего устройства и поэтому может быть использовано как при разработке новых эапоьынающих устройств, так и при модерниэации существующих. формула изобретения

1. Запоминающее устройство, содержащее накопитель, одним из выводов адресных обмоток которого соединены через адресный коммутатор с выходами первых ключей, другие выводы адресных обмоток подсоединены к выходам вторых ключей, разрядные обмотки накопителя, включенные совместно с первичными обмотками раэвяэывакщих транс809367 форматоров и блоком формирования разрядного тока по мостовой балансной схеме, блок управления, первые выходы которого соединены с одним из входов первых и вторых ключей, второй выход блока управления подключен к одному ия входов блока формирования разрядного тока, третий выход блока управления соединен с одним из входов блока считывания, и основной источник питания, выходы которого соединены с другими входами блока формирования разрядного тока, блока считывания и йакопителя, о т л и ч а ю щ е е с я тем, чтб, с целью повышения быстродействия устройства, в него введен стабилизатор тока, дополнительный источник питания и блок распределения тока, выход которого соединен с другими входами первых ключей, выход стабилизатора тока подсоединен к другим входам вторых ключей и к пер- 20 вому входу блока распределения тока, второй и третий входы которых соответственно соединены с шинами основного источника питания, вход стабилизатора тока подключен к первому 5 выходу дополнительного источника пи1. Авторское

Р 251004, кл. G

2. Авторское

9 460577, кл. G тотип). свидетельство СССР

11 С 11/00, 1969 ° свидетельство СССР

11 С 7/00, 1975 (про" тания, второй выход которого соединен с одним из выходов основного источника питания.

2. Запоминающее устройство по п.1, отличающееся тем, что блок распределения тока содержит корректирующий конденсатор, два стабилитрона, токозадающий резистор и сглаживающий конденсатор, одна иэ обкладок которого подсоединена к катоду первого стабилитрона и выходу блока распределения тока, а через токозадающий резистор к катоду второго стабилитрона, к одной из обкладок корректирующего конденсатора и к первому входу блока распределения тОка, аноды стабилитронов подключены ко второму входу блока распределения тока, третий вход которого соединен с другими обкладками конденсаторов.

Источники информации, принятые во внимание при экспертизе

809367 фри. f

Составитель А. Воронин

Редактор И. Ковальчук Техреду;.И.Голинка Корректор Г. Решетник

Заказ 440/68 Тиран 656. . .Подиисное

ВНИИПИ Государственного коэастета СССР по делам изобретений и открытий

113035, Москва, X-35, Раушская наб., д. 4/5

Филиал ППП Патент", r. Уид ород, ул. Проектная, 4