Запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Севетсинх

Сецналнстнческнх

Республнк

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВ ИТЕЛЬСТВУ (ii)809368 (6t) Дополнительное к авт. сеид-ву—

{22) Заявлено 3105,79 (21) 2771908/18-24 с присоединением заявки М(23) Приоритет р )м. к.з

G 11 С 11/00

ГесударетвенныЯ комнтет

СССР яе делам нзобретеннЯ н еткрытнЯ

Опубликовано 280281,Бюллетень W 8 (>>) УДК 881. З27. .6(088.8) Дата опубликования описания 280281 (72) Авторы изобретения г

A,È. Савельев, В.И. Косов, Л.И ° Косов и Л.Ф. Соколов

1 с

1 -:

Московский ордена Трудового Красного Знаме и текстильный институт!

°, ( (71) Заявитель (54) ЗАПОМИНШЦЕЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике и предназначено для .использования в цифровых вычислительных машинах с повышенными требованиями к информационной надежности.

Известно запоминающее устройство, в котором разрядно-счнтывакщие линии блока памяти, согласованные резисто. рами и подключенные через диодные цепочки к балластным резисторам, подключены к усилителям воспроизведения, а числовой регистр соединен с усилителями воспроизведения с формирователями разрядных токов и блоком управления. Блок управления соединей с формирователями адресных и разрядных токов которые подключены к блоку памяти (11 .

В этом устройстве при использовании "ratchet" записи не предусмотрена 20 коррекция разрядного тока по последнему положительному импульсу адресного тока, так как в нем отсутствуют элементы и блоки, обеспечивающие увеличение разрядного тока при записи "0".

Наиболее близким к предлагаемому является эапоминанхцее устройство на . элементе микробиакс со считыванием беэ разрушения информации. 30

Это устройство имеет как и большинство устройств подобного рода, блок памяти, соединенный с усилителями воспроизведения, которые подключены к числовому регистру, формирователи адресных и разрядных токов, соединенные с блоком памяти и блоком управления, диодные и реэисторные цепочки.

Запись информации в данное запоминакщее устройство (ЗУ) производится с помощью "ratchet"-записи,.то есть пачкой адресных токов записи и перекрывакхцим по времени эту пачку импульсов положительным разрядным током при записи "1" и отрицательным - при записи "0" (.2 . ь

Ф адресные токи записи, — -в» разрядный ток записи "1", — у разрядный ток записи "0" °

Но данное эапоьмнакхцее устройство не предусматривает симметричное перемагничивание запоминающих ферритовых элементов прн записи "1" и "0", так как последний импульс адресного тока

809368 записи всегда при "ratchet"-записи положительный, а разрядные токи записи имеют разную полярность. Это приводит к тому, что амплитуда считанного информационного сигнала "1" и "0" имеет различное амплитудное значение,, что в значительной мере снижает информационную надежность этого запоминающего.устройства.

Цель изобретения — повышение информационной надежности Эу за счет выравнивания амплитуды считанных сигналов "1" и "0".

Поставленная цель достигается тем, что в запоминающее устройство введены два триггера, формирователь импульсов, счетчик, счетный вход которого соединен с выходом блока управления, а выход — с единичным входом первого триггера, нулевой вход которого соединен с нулевым входом счетчика, выходом блока управления и нулевым входом второго триггера, единичный вход которого соединен с выходом формирователя импульсов, дифференцирующая цепочка, вход которой подключен к выходу числового регистраД5 а выход - к входу формирователя импульсов, два ключа, элемент И, входы которого соединены с выходами триггеров, а выход — с входами первого и второго ключей, соединенных с шиной питания, дополнительные нагрузочные элементы, включенные между выходами ключей и входами усилителей воспроизведения.

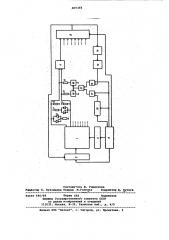

На чертеже представлена схема запоминающего устройства.

Эапоминающее устройство содержит блок 1 памяти, соединенный с формирователями 2 адресных токов, формирователями 3 разрядных токов и усилителями 4 воспроизведения. Входы 40 усилителей 4 воспроизведения подключены к согласующим элементам на резисторах 5 н диодных цепочках 6 к нагрузочным элементам на резисторах 7, а выход — к первым входам числового, 45 регистра 8, выход которого соединен с формирователями 3 разрядных токов, а второй вход подключен к выходу блока 9 управления, второй и третий выходы которого подключены к формиро- у) вателям 2 адресных токов и к формирователям 3 разрядных токов. Четверты выход блока 9 управления соединен со счетным входом счетчика 10, вы. ход которого соединен с единичным входом триггера 11, а нулевой входс нулевым входом триггера 12 и нулевыми входами счетчика 10 и пятым выходом блока 9 управления. Единичный вход триггера 12 подключен к формирователю 13 импульсов, вход которо- dO го подсоединен к выходу дифференцирующего элемента 14, подключенного к выходу числового регистра 8. Выходы триггера 11 и триггера 12 подключены соответственно к первому и второ-45 му входам элемента 15 И, выход которого соединен с входами ключей 16, соединенных с дополнительными нагрузочными элементами на резисторах 17.

Другие концы дополнительных нагрузочных.резисторов 17 соединены с входами усилителя 4 воспроизведения.

В режиме записи блок 9 управления вырабатывает на нервом выходе управляющий сигнал, по которому в соответствии с кодом числа, находящимся в числовом регистре 8 подаются соответствующие потенциалы на выходы формирователя 3 токов. В это же время иэ блока 9 управления (по третьему выходу) подается сигнал на формирователь 3 разрядных токов, который и запускает его, а в блок 1 памяти, в разрядные шины, подаются положительные и отрицательные разрядные токи, соответствующие кодам ("1" или "0" ) числа.

Эатем с некоторой задержкой по времени относительно вышеназванных управляющих сигналов на втором выходе блока 9 управления вырабатывается сиг« нал для запуска формирователей 2 адресных токов. По этому сигналу запускаются формирователи 2 адресных токов, вырабатывающие по соответствующему адресу заданное количество положительных и отрицательных импульсов тока, то есть импульсов ".ratchet"записи.

В этом режиме амплитуда разрядного тока при записи "1", то есть положительного разрядного тока, определяется нагрузочными резисторами 7, а диодные цепочки создают большое омическое сопротивление сигналу считывания эа счет нелинейности вольтамперной характеристики диодов. Амплитуда разрядного тока при записи

"1" остается постоянной, а формирователи 2 адресных токов всегда выдают последний импульс положительной .полярности.

При записи "0" для исключения асимметрии считанных сигналов, то есть для того, чтобы исключить уменьшение считанного сигнала "0", должен воз расти разрядный ток записи при приходе последнего импульса в пачке адресных токов при "ratchet"-записи. Поэтому при записи по каждому разряду происходит дифференцирование разрядного тока на дифференцирующем элементе 14. Этот импульс поступает на формирователь 13 импульсов. Продиффереицированный импульс по переднему фронту разрядного тока восстанавливает триггер 12 в единицу только при записи "0". Блок 9 управления всегда при записи "0" и "1" подает на счетчик 10 текущее значение количества положительных импульсов и по последнему расчетному импульсу со счетчика 10 триггер 11 восстанавливается в единицу (перед циклом записи триг809368 геры 11 и 12 всегда по сигналу с пятого выхода блока 9 управления восстанавливаются в нулевое положение).

В этом случае с выхода элемента 15 И поступает управляющий потенциал, который открывает ключи 16 и дополнительные нагрузочные резисторы 17 подключаются к шине питания и становятся подключенными параллельно к нагрузочным резисторам 7, что увеличивает разрядный ток в момент прихода оследнего положительного адресного ока "ratchet"-записи, то есть — адресные токи

1 записи, -в- разрядный ток записи "1", =Л- записи "0".

Такая запись "0" обеспечивает рав- . ные условия записи "1" и "0", то есть 39 одинаковые выходные считанные сигналы как информационной "1", так к "0".

В режиме считывания дополнительные нагрузочные резисторы отключены и работают только резисторы 5 как согласу-д ющие резисторы.

Поэтому использование предлагаемого запоминающего устройства в цифровой вычислительной машине может удовлетворить повышенные требования к информационной надежности при использовании в ней эапоминакицих устройств с "ratchet"-записью к повысить общую эффективность использования ЦВИ.

Формула изобретения

Запоминающее устройство, содержащее блок памяти, выход которого соеди +) нен с входами усилителей воспроизведения, формирователи адресных и раэрядных токов, соединенные выходами с входаьы блока памяти, согласующие элементы, соединенные с вход:1ми усилителей воспроизведения, нагрузочные элементы, подключенные к выходам блока памяти, блок управления, числовой регистр, соединенный с выходами усилителей воспроизведения, с входами формирователей разрядных токов и с первым выходом блока управления, второй и третий выход которого подключен к формирователям адресных и разрядных токов, о т л и ч а ю щ ее с я тем, что, с целью повыаения информационной надежности, в него введены два триггера, формирователь импульсов, счетчик, счетный вход которого соединен с четвертым выходом блока управления, а выход — с единичным входом первого триггера, нулевой вход которого соединен с нулевюж входами счетчика, пятым выходом блока управления к с нулевым входом второго триггера, единичный вход которого соединен с выходом формирователя импульсов, дифференцирующий элемент, вход которого подключен к выходу числового регистра, а выход — к входу формирователя импульсов, два ключа, элемент И, входы которого соединены с выходами триггеров, а выход — с входамк первого и второго ключей, соединенных с шиной питания, дополнительные нагруз очные элементы, включенные между выходами ключей и входами усилителей воспроизведения.

Источники информации, принятые во внимание при экспертизе

1.Шигин А.Г. и дерюгин А A.цкфро вые вычислительные машины. И., "Энергия", 1975, с. 221.

2. Петерсен М. Бортовая память на элементе микробиакс со считыванием беэ разрушения информации. ИРП, СССР, перевод 9 2433, 1977. 809368

Составитель В. Гордонова

Редактор Н. Кузнецова Техред M.Голинка Корректор В. Вутяга: л . АЮ

Ю ° вЪЮЬю аю

Заказ 440/68 Тираж 656 Поднио нов

ВНИИПИ Государственного комитета CCCP по делам изобретений и открытий

113035, Москва, Ж»35, Раушская иаб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4