Ассоциативный запоминающийэлемент

Иллюстрации

Показать всеРеферат

(72) Авторы изобретения

А. А. Князев, В. И. Тарасенко и Ф. А. Тютрин (7I) Заявитель (54) АССОБИАТИВНЫЙ ЗАПОМИНАЮШИЙ ЭЛЕМЕНТ

Изобретение относится к запоминающим устройствам.

Известен ассоциативный запоминающий элемент, содержащий триггер, адресную шину, элементы управления записью, разрядные шины нуля и единицы, элементы управления считыванием, логический вход и выход ячейки, шину нулевого потенциала, инвертор, восстанавливающий вентиль, ключевой вентиль, логический элемент е

ИЛИ-НЕ и параллельно соединенные передающие вентили j1l

Недостатком этого ассоциативного asпоминаюшего элемента является большое число логических элементов и связей, что IS усложняет ячейку и матрицу ассоциативной памяти.

Наиболее близким техническим решением к предлагаемому изобретению является запоминающий элемент ассоциативной матрицы, содержащий триггер с двумя входными схемами И, две схемы И счйтывания информации, схему ИЛИ, схему НЕ, две выходных схемы И, две вы ходных схемы ИЛИ, пять входных и пять вьк одних шин 2).

Недостатком этого элемента ассоциативной матрицы является большое число логических Рлементов и связей, что уеложняет ячейку и матрицу ассоциативной памяти и снижает быстродействие ассоциативного процессора при выполнении операций чтения и ассоциативного поиска.

Бель изобретения — повышение быстродействия ассоциативного запоминающего элемента.

Поставленная цель достигается тем, что в ассоциативный запоминающий элемент, содержащий триггер, четыре элемента И и первый элемент ИЛИ, причем выходы первого и втсрого элементов И подключены соответственно к едиййчному и нулевому входам триггера, единичный и нулевой выходы котсрого соединены со; ответственно с первыми входами третье го и четвертого элементов И, выходы которых подключены соответственно к первому и второму входом первого эле809370 мента ИЛИ, первые входы первого и второ1 о элементов И и третий вход первого элемента ИЛИ соединены соответстВЕйНО С ПЕРВЫМИ ВХОДОМ И ВЫХОДОМ,ОО втopbIMH входом и выходом и третьими входом и выходом ассоциативного запо. м ин аю щего элемента, введены вт Орой .элемент ИЛИ и пятый элемент И, первый и второй входы которого подключены соответственно к выходу первого элемен та ИЛИ и четвертому выходу и к четвертому входу ассоциативного запоминающего элемента, выход второго элемента

ИЛИ соединен со вторым входом третьего элемента И, а первый и второй входы подключены соответственно к пятым входу и выходу и к первым входу и выходу ассоциативного запоминающего элемента, второй, третий и четвертый входы первого элемента И и второй вход sroporo элемента И соединены соответственно с шестым входом и выходом, со вторыми входом и выходом, с седьмыми входом и выходом и с восьмыми входом и выходом ассоциативного запоминающего элемента, а выход пятого элемента И и единичный выход триггера— соответственно с девятым и с десятым выходами ассоциативного запоминающего элемента.

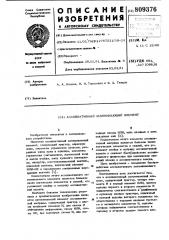

На фиг. 1 изображена структурная схема предлагаемого ассоциативного запоминающего элемента, на фиг. 2 — функциональная схема ассоциативного процессора, в котором применяется предлагаемый элемент.

Предлагаемый элемент содержит (фиг, 1 и фиг. 2) входы 1-8, выходы

9-18, триггер 19, первый 20, второй

21, третий 22, четвертый 23 и пятый

24 элементы И, первый 25 и второй 26 элементы ИЛИ.

Выходы первого 20 и второго 21 элементов И подключены соответственно к единичному и нулевому входам триггера 19, единичный и нулевой выходы êoторого соединены соответственно с первыми входами третьего 22 и четвертого 23 элементов И, выходы которых подключены соответственно к первому и второму входам первого элемента

25 ИЛИ. Первые входы первого 20 и второго 21 элементов И и третий вход первого элемента 25 ИЛИ соединены соответственно с первыми входом 1 и выходом 9, со вторыми входом 2 и выходом 10 и третьими входом 3 и выходом

11 ассоциативного запоминающего элемента. Первый и второй входы пятого

4 элемента 24 И подключены соответственно к.выходу первого элемента 25 ИЛИ и четвертому выходу 12 и к четвертому входу 4 ассоциативного запоминающего элемента. Выход второго элемента

26 ИЛИ соединен со вторым входом третьего элемента 22 И, а первый и второй входы подключены соответственно к пятым входу 5 и выходу 13 и к первым входу 1 и выходу 9 ассоциативного запоминающего элемента. Второй, третий и четвертый входы первого элемента 20 И и второй вход второго элемента 21 И соединен соответственно с шестыми входом 6 и BbKogoM 14, сО BtopbIMH ВходОм

2 и выходом 10, с седьмыми входом 7 и выходом 15 и с восьмыми входом 8 и выходом 16 ассоциативного запоминающего элемента. Выход пятого элемента

24 И и единичный выход триггера 19 соединен соответственно с девятым 17 и с десятым 18 выходами ассоциативного запоминающего элемента.

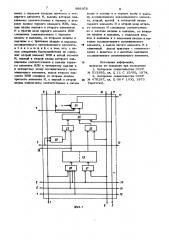

Ассоциативный процессор содержит (фиг. 2) ассоциативные запоминающие элементы 27, накопитель 28, представляющий собой матрицу, блок 29 местного управления, третий 30, четвертый 31 и пятый 32 элементы ИЛИ, элемент зо

33 НЕ и шестой 34 элемент ИЛИ вЂ” по числу строк матрицы накопителя, входящие в блок местного управления, шину 35 записи, блоки 36 ввода и выводы 37 информации. Первый 9, третий 11 и восьмой 16 выходы каждого предыдущего

35 ассоциативного запоминающего элемента

27, кроме первого, соединены соответственно с первым 1, с третьим 3 и восьмым 8 входами последующего в столбце матрицы накопителя 28 ассоциативного

4О запоминающего элемента 27, кроме последнего. Второй 10, пятый 13, шестой

14, седьмой 15 и девятый 17 выходы каждого предыдущего ассоциативного запоминающего элемента 27 подключены соответственно ко второму 2, к пятому

5, к шестому 6, к седьмому 7 и к четвертому 4 входам последующего в строке накопителя 28 ассоциативного запоминающего элемента 27, кроме входящих в

5О первый столбец накопителя 28. Второй 2, шестой 6, и седьмой 7 входы и десятый

18 выход каждого ассоциативного запоминающего элемента 27 первого столбца накопителя 28 соединен соответственно

55 с выходами третьего 30, четвертого 31 и пятого 32 и со входом шестого 34 элементов ИЛИ. Первые 1, третьи 3 и восьмые 8 BxoAbI ассоциативных запоми80М76 нающих элементов 27 первой строки накопителя 28 подключены к выходам блока 36 ввода. Первый вход третьего элемента 30 ИЛИ соединен с выходом элемента 33, вход которого подключен к выходу шестого элемента 34 ИЛИ своей

; строки накопителя 28 и к первому входу пятого элемента 32 ИЛИ следующей строки накопителя 28.

Один из входов четвертого элемента

31 ИЛИ соединен со вторыми входами третьего 30 и пятого 32 элементов ИЛИ.

Элемент .работает следующим образом.

Предлагаемый ассоциативный запоминающий элемент позволяет реализовать ассоциативный процессор (фиг.2), имеющий пять режимов работы, запись с опросом, запись беэ опроса, чтение, ассоциативный поиск и поиск максимума.

Работу ассоциативного запоминающего элемента рассмотрим на примерах выполнения записи беэ предварительного опроса и ассоциативного поиска. Записываемое слово подается на входы первой

2$ строки матрицы 28 таким образом, что прямой код каждого разряда слова поступает на первый вход 1, а обратный код этого же разряда — на восьмой вход 8 ассоциативного запоминающего элемента

27 соответствующего столбца накопителя 28.

Запись беэ предварительного опроса матрицы накопителя 28 производится при поступлении новой информации, которая

3S должна быть записана в любую свободную строку матрицы накопителя 28.

B каждой из занятых информацией строк MBrpHllbl накопителя 28 единичный сигнал триггера 19 какого-либо иэ ассоциативных запоминающих элементов 27, пройдя с выхода 18 через шестой эле.мент 34 ИЛИ, проинвертируется элементом 33 НЕ. При этом через третий элемент 30 ИЛИ на вход 2 каждого из ас4$ социативных запоминающих элементов 27 данной строки будет подан нулевой сигнал, который закроет для записи информации первый 20 и второй 21 элемент И всех ассоциативных запоминающих элементов

$0

27 этой строки. Одновременно этот же сигнал " 1 поступает на седьмые входы

7 ассоциативных запоминающих элементов

27 следующей строки, разрешая запись в нее информации. Если эта строка накопителя 28 свободна or информации,. ro

$$ нулевые сигналы с выходов триггеров

19 через выходы 18 ее ассоциативных элементов пройдут как сигналы обратной связи 1 на вторые 2 входы своей Lrpoки, разрешая запись информации в нее.

Эти же нулевые сигналы с входов триггеров 19 через шестые 34 и пятые 32 элементы ИЛИ пройдут на седьмые 7 входы ассоциативных запоминающих элементов 27 следующей строки и закроют ее для записи информации. Одновременно с шины записи 35 на вход четвертого элемента 3. ИЛИ подается единичный сигнал Запись, проходящий на входы 6 всех ассоциативных запоминающих элементов 27. При этом открыта для записи только первая после занятой свободная строка накопителя 28, в которую и будет записана информация без предварительного опроса накопителя 28.

При ассоциативном поиске разряды признака опроса подаются с блока 36 ввода на входы нижней строки накопителя

28 таким образом, что прямой код каждого разряда признака опроса подается на вход 1, а обратный код- этого же разряда — на вход 8 соответствующего сгопбца накопителя 28.

Маскирование опроса производится путем подачи сигнала 1 на входы 3 соответствующих столбцов матрицы 28.

На все входы 4 левого столбца накопителя 28 подается сигнал "1 . При этом сигнал 1 появится на выходах 3 7 правого столбца матрицы в тех и только тех строках, в которых содержимое всех незамаскированных разрядов совпадает с кодами соответствующих разрядов признака опроса.

Техникоэкономическое преимушество предлагаемого ассоциативного запоминающего элемента заключается в том, что он позволяет реализовать режим записи информации в свободную строку накопителя без предварительного опроса всего накопителя, е также в сокрашении числа логических элементов по сравнению с известным элементом, за счет чего повышается быстродействие при выполнении операций записи и ассоциативного поиска в накопителе.

Формула изобретения

Ассоциативный запоминающий элемент, содержащий триггер, четыре элемента И и первый элемент ИЛИ, причем выходы первого и второго элементов И подключены соответственно к единичному и нулевому входам триггера, единичный и нулевой выходы которого соединены соответст7 80

Ф венно с первыми входами третьего и четвертого 9JxeMeHTa И, выходы которых подключены соответственно к первому и второму входам первого элемента ИЛИ, первые входы первого и второго элементов

И и третий вход первого элемента ИЛИ соединены соответственно с первыми входом и выходом, со втарымн входом и выходом и с трегьимн входом и выходом ассоциативного запоминающего элемента, о г л и ч а ю m и и с я тем, что, с целью повышения быстродействия он содержит второй элемент ИЛИ и пятый элемент

И, первый и второй входы которого подключены соответственно к выходу первого элемента ИЛИ и четвертому выходу и к четвертому входу ассоциативного запо- минаккцего элемента, выход второго эле. мента ИЛИ соединен со вторым входом третьего элемента И, а первый и второй входы подключены соответственно к пятым

9376 входу и выходу н к первым входу и выходу ассоциативного запоминающего элемента, второй, третий и четвертый входы первого элемента И и втсрой вход втарого элемента И соединены соответственI но с шестым входом и выходом, со вторымн входом и выходом, с седьмыми входом и выходом и с восьмыми входом и выходам ассоциативного запоминающего

1О элемента, а выход пятого элемента И и единичный .выход триггера - соответственно с девятым и с десятым выходами ассоциативного запоминающего элемента.

f 5 . Источники информации, принятые во внимание прн экспертизе

1. Авторское свидетельство СССР

No. 513393, кл. Q ll С 15/00, 1974.

2. Авторское свидетельство СССР

l4 478297, кл. С» Об C 1/ОО, 1973 (прототип).