Программируемое постоянное за-поминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советски к

Социвлнстмческмк республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

<111509378 (61) ???????????????????????????? ?? ??????. ????????-???? (22) ????????????????01.03.78 (21) 2586371>

Опубликовано 28.02.8 1. Бюллетень М 8

Дата опубликования описания 03.03.81 (5I )A%. Кл.

Я 11 С 17/00

Гевударствекнвй кемктет

СССР вв делам взебретекий к вткрмткй (53) УДК 681,, .327.28 (088.8) А. И. Мальцев, А. П. Нагни, B. А. Кульбашньй, В. 3» Глушков, В. А. Милошевский и А. А. Яковйев» -11* .»..

ПЛ. ;-, ::

»

1 ф

»

А".;: ., : ) -,,;д

1 (72) Авторы изобретения (71) Заявитель (54) ПРОГРАММИРУЕМОЕ ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ

УСТРОЙСТВО

Изобретение относится к вычислительной технике и может быть использовано при построении систем памяти ЭВМ.

Известны программируемые постоянные запоминающие устройства Н8 МДП-транзисторах с изменяемым порогом включе5 ния 11 и 52).

Основным их недостатком является

-невозможность избирательного стирания информации, в связи с чем при частичном

1О перепрограммировании возникает необходимость в буферном запоминающем устройстве.

Известно другое запоминающее устройство, содержащее дешифраторы строк

15 и столбцов и матричный накопитель, каждый запоминающий элемент которого со. держит. МЙП-транзистор с изменяемым порогом включения, затворы которых по строкам соединены с числовой шиной, под20 ключенной к одному из выходов дешифратора строк, а истоки и стоки их соединены с истоковыми и стоковыми разрядными шинами, соединенными с соот ветствующими выходами дешифратора столбцов (3) .

Недостатком этой конструкции является невозможность стирания информации в одном запоминающем элементе, так как затворы транзисторов обьединены и поэтому необходимо запоминать содержимое слова во внешнем регистре.

Наиболее близким техническим решением к предлагаемому является прог раммируемое постоянное запоминающее устройство, содержащее дешифраторы строк и столбцов, выходы которых подключены к словарным, первым и вторым разрядным шинам, соединенным соответственно с затворами, стоками и истоками запоминающих МИП-транзисторов с изменяемым псрогом включения, подложки которых подключены к шине общего стирания, нагруэочные транзисторы, затворы и истоки которых подключены к шине питания, стоки — к первым разрядным шинам, а подложки — к шине нулевого потенциала, первые и вторые коммутирующие транзитовЂ

809378 торы, истоки и подложки которых подключены к шине нулевого потенциала, затворы — к соответствующим шинам перезаписи, стоки вторых коммутирующих транзисторов подключены ко вторым раз- 5 рядным шинам (4).

Недостатком этого запоминающего устройства также является невозможность избирательного стирания и регенерации информации непосредственно внутри устройства, Цель изобретения — расширение области применения программируемого постоянного запоминающего устройства за счет избирательного стирания и регенерации >5 информации, Поставленная цель достигается тем, что в устройство введена шина избирательного стирания и управляющие MLlllтранзисторы с изменяемым порогом вклю- 20 чения, стоки которых соединены с первыми разрядными шинами, истоки — со стоками первых коммутирующих транзисторов, затворы — с шиной избирательного стирания, а подложки с шинойобщего стира- ?5 ния.

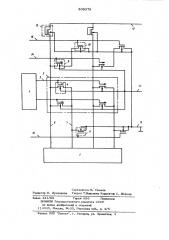

На чертеже приведена электрическая схема запоминающего устройства, Устройство содержит дешифратор 1 строк и дешифратор 2 столбцов, матрич- з0 ный накопитель 3 с запоминающими MQIlтранзисторами 4 с изменяемым порогом включения, словарные 5, первые 6 и вторые 7 разрядные шины, нагрузочные транзисторы 8, управляющие транзисторы 9 с изменяемым порогом включения, первые 10 и вторые 11 коммутирующие транзисторы, шину 12 питания и шину

13 нулевого потенциала, шину 14 избирательного стирания, шины 15 и 16 пе- 40

1 резаписи, шину 17 общего стирания.

50

ss Формула изобретения

В такой конструкции имеется воэможность производить запись иэ запоминающих транзисторов 4 в управляющие транзисторы 9, при которой происходит инверсия информации, а именно: запись логического нуля в управляющий транзистор

9 происходит лишь при единичном состоянии запоминающего транзистора, а логическйй нуль в управляющем транзисторе 9 преобразуется в логическую единицу в запоминающем транзисторе 4.

Стирание информации в выбранном слове или во всех управляющих транэисто рах 9 происходит при подаче высокого уровня на шину 17 и низкого уровня на выбранную словарную шину 5 или на шину 14 избирательного стирания, а на остальные шины 5 подается высокий уровень, что переводит выбранные транзисторы 4 или 9 в открытое состояние (логическая единица).

Запись информации в транзисторы 4 или 9 производится при подаче высокого уровня на выбранную словарную шину 5 или шину 14 и низкого уровня на первую разрядную шину 6, в результате чего,,высокое напряжение оказывается приложенным к затворному диэлектрику только одного транзистора 4 или 9 и переводит его в закрытое состояние (логический нуль). Йля этого высокое напряжение подается на шину 12 питания и через нагрузочные транзисторы 8 попадает на первые разрядные шины 6, а на вторые разрядные шины 7, через коммутирующий транзистор 11, подается низкий уровень.

Избирательное стирание информации осуществляется в несколько этапов. Сначала стирается информация во всех управляющих транзисторах 9, затем информация иэ выбранного слова переносится в управляющие транзисторы подачей высокого уровня на шину 14 и 12 и отпирающего напряжения на шину 16. После этого производится дозапись логических нулей в соответствующие управляющие транзисторы 9 указанным выше способом, стирание информации в выбранном слове и перенос информации из управляющих транзисторов в это выбранное слово (транзисторы 4) подачей высокого уровня на шину 12 и шину 5 и отпирающего напряжения на шину 15. Такой перенос также происходит с инверсией информации.

Считывание осуществляется. по величине тока между первой и второй разрядными шинами 6 и 7 обычным способом.

Кроме того, в такой конструкции можно вводить информацию через управляющие транзисторы 9 в инверсном коде с последующим переносом ее в слово накопителя 3, что уменьшает напряжение, необходимое на шине 12 питания, так BBK в этом случае время воздействия на запоминающий транзистор 4, в который не производится запись логического нуля, уменьшается по сравнению с поочередной записью логических нулей в запоминающие транзисторы 4 выбранного слова.

Программируемое постоянное запоминающее устройство, содержащее дешифра800378 торы строк и столбцов, выходы которых подключены к словарным, первым и вторым разрядным шинам, соединенным соответственно с затворами стоками и ис- токами запоминающих Milli-транзисторов л с изменяемым псрогом. включения, подложки которых подключены к шине общего стирания, нагруэочные транзисторы, эатвсры и истоки которых подключены к шине питания, стоки — к первым разряд- 10 ным шинам, а подложки — к шине нулевого потенциала, первые и вторые коммутирующие транзисторы, истоки и подложки которых подключены к шине нулевого потенциала, затворы — к соответст- И вующим шинам перезаписи, стоки втсрых, коммутирующих транзисторов подключены ко вторым разрядным шинам, о т л и ч аю щ е е с я тем, что, с целью расширения области применения устройства эа счет избирательного стирания и регенерации инфсрмации, в него введены шина избирательного стирания и управляющие

МЙП-транзисторы с изменяемым псрогом включения, стоки которых соединены с первыми разрядными шинами, истоки - со стоками первых коммутирующих транзисторов, затворы — с шиной избирательного стирания, а подложки с шиной обще го стирания.

Источники информации, принятые во внимание цри экспертизе

1. Патент США N 3909806, кл. 340-173, опублик. 1975.

2. Авторское свидетельство СССР

Мо 458036, кл. 5 11 С 11/40, 1973.

3. Патент США N.o 3846768, кл. 340-173, опублик. 1975.

4. Прангишвили И. В. и др. Элементы

ЗУ íà MLlll структурах, М., 1978, с.168169 (nporeraa).

Составитель В. Ушаков

Редактор Е. Лушникова Техред Т.Власенко Корректор С. Шекмар

Закаэ 441/69 Тираж 656 Подписное

ВНИИПИ Государственного комитета СССР

1 по делам изобретений и открытий

11ЗОЗ5, Москва, Ж-Э5, Раушская наб., д. 4/5

Филиал ППП "Патент, г. Ужгород, ул, Проектная, 4