Ячейка памяти для сдвиговогорегистра

Иллюстрации

Показать всеРеферат

Союз Советск нк

Соцналнстнчесинв

Ресттубпнк

ОП ИСАНИ Е

ИЗОБРЕТЕН ИЯ

К. АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (1809382 (61) Дополнительное к авт. свид-ву— (22) Заявлено 26.03.76 (2! ) 2344029/18-24 с присоединением заявки М— (23) Приоритет

Опубликовано 28 02.81 Бюллетень М 8 (S3)M. Кл.

Я 11 С 19/00 тваударстввввнв квкктет

СССР яв лвввн кзвбретвкик и вткрнтий (.53) УДК681. .327.66 (088.8) Дата опубликования описания 03.03.81

Г. С. Брайловский, И. М. Лазер, Ю. С. Кр и Л. M. Лиогонькая (72) Авторы изобретения (71) Заявитель (54) ЯЧЕЙКА ПАМЯТИ ДЛЯ СДВИГОВОГО

РЕГИСТРА

И $2).

Изобретение относится к построению структур вычислительной техники и дискретной автоматики на логических элементах, преимущественно . в интегральном исполнении.

Известен регистр сдвига, ячейка памя- S ти которого содержит два триггера, выполненные на элементах И-ИЛИ-НЕ, и элементы И 11.

Однако наличие значительного количества элементов. усложняет структуру ячейки памяти, что в конечном счете, при проектировании регистров сдвига приводит к увеличению мошности генератора тактовых импульсов.

Наиболее близким к предлагаемому является регистр сдвига, ячейка памяти которого содержит два RS -триггера, один из которых триггер памяти, другойкоммутационный триггер. В каждом триггере выход элемента И-ИЛИ-НЕ соединен с одним из входов всех элементов

Разряд этого реверсивного регистра является самым экономичным с точки зрения количества элементов И-ИЛИ HE при максимально достижимом быстродействии.

Недостатком известного регистра является повышенная нагрузка на генератор тактовых импульсов, так как вход тактовых импульсов регистра в каждой ячейке нагружен на шесть входов логических элементов. Поэтому при проектировании многоразрядных реверсивных регистров сдвига приходится на 50% увеличивать необходимую мощность генератора тактовых импульсов.

Цель изобретения — повышение надежности ячейки памяти за счет снижения коэффициента разветвления тактовой шины.

Поставленная цель достигается тем, что в ячейку памяти для сдвигового регистра, содержащую триггер памяти, выполненный на первом, втором элементах

И и первом и втором элементах ИЛИ-HE

80МЙ2

30 го г5

З0

50 коммутационный триггер, выполненный на третьем, четвертом, пятом и шестом элементах И и третьем и четвертом элементах ИЛИ-НЕ, причем первые входы первого и второго элементов И триггера памяти соединены с выходами элементов ИЛИНЕ и первыми входами элементов И коммутационного триггера соответственно, втсрые входы первого и второго элементов И триггера памяти и третьего и четвертого элементов И коммутационного триггера соединены с тактовой шиной, вторые входы пятого и шестого элементов И коммутационного триггера соединены со входами ячейки памяти, выходы элементов ИЛИ-НЕ триггера памяти соединены с первыми выходами ячейки памяти и шины сдвига, введены в коммутационный триггер седьмой и восьмой элементы И, первые входы которых подключены к первым входам пятого и шестого элементов И коммутационного триггера, вторые входы — к первой шине сдвига, третьи входы — ко вторым выходам ячей1. кн памяти, а третьи входы пятого и шестого элементов И коммутационного триггера соединены со второй шиной сдвига.

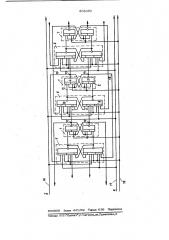

На чертеже -представлена схема ячейки памяти для сдвигового регистра.

Ячейка памяти содержит триггер памяти 1, выполненный на элементах И 2 и 3 и элементах ИЛИ-НЕ 4 и 5, коммутационный триггер 6, выполненный на элементах И 7 — 10. причем вторые входы элементов 9 и 10 соединены со входами 11 и 12 ячейки памяти, выходы а элементов ИЛИ-НЕ 4 и 5 соединены с первыми выходами 13 и 14 ячейки памяти, а третьи входы элементов И 9 и 10 соединены со вторыми выходами 15 и

16 ячейки памяти, вторые входы элементов И 9 и 10 соединены с первой шиной сдвига 17, третьи входы элементов И 9 и 10 — со второй шиной сдвига 18, вторые входы элементов И 2 и 3 и элементов И 7 и 8 соединены с тактовой шиной 19.

Функция реверсивной обработки информацни в разряде регистра, построенного на предлагаемой ячейке памяти, реализуется на элементах коммутационного триггера 6.

Сдвиг вправо осуществляется при значениях входов реверса и инверсии реверса соответственно Р = 0 и R = 1 по шинам

17 и 18 соответственно. Б этом режиме элементы И 9 и 10 закрыты и воспринимают информацию от предыдущего разряда.

Сдвиг влево осуществляется прн значениях входов реверса и инверсии реверса соответственно R = 1 и R = О. В этом режиме элементы И 9 и 10 также закрыты и воспринимают информацию от предыдущего разряда. Вход тактовых импульсов в каждом разряде нагружен на четыре входа логических элементов.

Применение регистра, построенного на предлагаемой ячейке памяти, позволяет при заданной нагрузочной способности генератора тактовых импульсов либо увеличить число разрядов регистра, подключаемых к выходу генератора, на 50%,. либо при заданном количестве разрядов регистра уменьшить нагрузку генератора также н а 3 3%.

Формула изобретения

Ячейка памяти для сдвигового регистра, содержащая триггер памяти, выполненный на первом, втором элементах И и первом и втором элементах ИЛИ-НЕ, коммутационный триггер, выполненный на третьем, четвертом, пятом и шестом элементах И и третьем и четвертбм элементах ИЛИ-НЕ, причем первые входы первого и второго элементов И триггера памяти соединены с выходами элементов ИЛИНЕ и первыми входами элементов И коммутационного триггера соответственно, вторые входы первого и второго элементов И триггера памяти и третьего и четвертого элементов И коммутационного триггера соединены с тактовой шиной, вторые входы пятого и шестого элементов

И коммутационного триггера соединены со входами ячейки памяти, выходы элементов ИЛИ-НЕ триггера памяти соединены с первыми выходами ячейки памяти и шины сдвига, о т л и ч а ю щ а я— с я тем, что, с целью повышения надежности ячейки памяти за счет снижения коэффициента разветвления тактовой шины, в коммутационный триггер ячейки памяти введены седьмой и восьмой элементы И, первые входы которых подключены к первым входам пятого и шестого элементов И коммутационного триггера, вторые входы - к первой шине сдвига, третьи входы - ко вторым выходам ячейки памяти, а третьи входы пятого и шестого элементов И коммутационного триггера соединены со второй шиной сдвига.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

% 427387, кл. С, 11 С 19/00, 1971.

2. Филиппов А. Г. и др. Проектирование логических узлов ЭВМ М., Сов, радио", 1974, с, 137 (прототип).