Устройство для сдвига со встро-енным контролем

Иллюстрации

Показать всеРеферат

Союз Советски н

Соцналнстнческик

Рес1тублнк

ОП ИСАНИЕ

ИЗОБРЕТЕН Ия

Х АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (ii>809386 (6 I ) Дополнительное к авт. синд-ву (22) Заявлено 11.06.79 (21)2778125/18-24 с присоединением заявки РЙ— (23 ) П рнорнтет .— (51)М. Кл.

11 С 19/00

G 11 С 29/00

Гееударетеенный кемнтет

CCCP не лелем нзебретеннй н еткрмтнй

Опубликовано 28.02.81 Бюллетень М 8

{gg) УДК 681.З27..66(088.8) Дата опубликования описания ОЗ.ОЗ.81 (72) Авторы изобретения

Ю. Я. Берсон, А. И. Буртов и E. Я. Марголин (7!) Заявитель (54) УСТРОЙСТВО ДЛЯ СДВИГА СО ВСТРОЕННЫМ

КОНТРОЛЕМ

Изобретение относится к вычислитель, ной технике и дискретной автоматике и может быть использовано в качестве устройства сдвига (хранения) со встроенным контролем.

Известны регистры сдвига со схемами контроля, обеспечивающими контроль рабоTbl регистра HB основе анализа свертки по модулю два разрядов регистра в данном такте работы и значения этой свертки Т11 и f2).

I0

Иэ известных устройств наиболее близким по технической сущности является устройство для проверки четности двоичного регистра, которое содержит сдви1% говый регистр, два одноразрядных счетчика, схему свертки по модулю два, три двухвходовых сумматора по Модулю два, регистр памяти. Выходы регистра сдвига соединены со входами схемы свертки и одноразрядных счетчиков, выходы которых соединены со входами первого сумматора. Выход схемы свертки соединен со входом регистра памяти и входом гретьего сумматора, выход которого является BbIxolloM устройства, а второй ВхоА соединен с выходом второго сумматора, входы которого соединены с выходом регистра и выходом первого сумматора (31.

Недостатками указанных устройств являются сложность схемы контроля, снижение достоверности контропя, а также отсутствие контроля записи и хранения информации в регистре.

Цель изобретения состоит в упрощении устройства и расширении области применения за счет осуществления воэможности контроля в режиме записи и хранения информации.

Поставленная цель достигается тем, что в устройство для сдвига со встроенным контролем, содержащее блок свергки по модупю два, первые выходы которого соединены с выходами регистра сдвига, триггер контропьного разряда, первый вход которого соединен с первым входом регистра сдвига и шиной синхронизации, вторые входы регистра сдвига

80"..О М

45 подключены соответственно к первой шине управления и к первой информационной шине, третий вход регистра сдвига подсоединен ко второй информационной шине, введены коммутатор и блок управления режимом свертки, выходы которого соединены со вторыми входами блока свертки по модулю два, выход коммутатора подключен ко второму входу триггера контрольного разряда, выход которого соединен с первым входом блока управления режимом свертки, первый вход коммутатора подключен ко второй информационной шине, второй вход коммутатора соединен с одним иэ выходов регистра сдвига и вторым входом блока управления режимом свертки, третий вход которого подсоединен к первой информационной шине, выход блока свертки по модулю два соединен с третьим входом коммутатора и выходом устройства.

Сущность изобретения заключается в построении устройства на указанных блоках таким образом, нто блок управления переключает режим работы свертки в положительные и отрицательные полупериоды такта, а также в зависимости от сигналов управления регистра, причем в положительный полупериод блок свертки формирует признак четности разрядов регистра для следующего такта, запоминаемый в триггере контрольного разряда, а в отрицательный полупериод блок свертки сравнивает запомненное значение признака четности, либо записанное в триггер при приеме или хранении значение контроль35

Ного разряда кода, введенного в регистр, с текущей четностью разрядов регистра, определяя таким образом исправность работы регистра как в режиме сдвига, так и в режиме приема и хранения информации.

Таким образом, блок свертки несет двойную функциональную нагрузку: формирование будущего значения четности и определение исправности работы регистра. йостижение цели изобретения способствует выполнению блока управления режимом свертки в виде грех 3-входовых логических элементов И-НЕ, первые входы которых являются информационными входа- 50 ми блока, вторые и третьи входы объелинены и служат первым и вторым управляюкими входами блока, а входами блока являются выходы элементов И-НЕ.

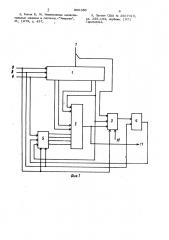

На фиг. 1 изображено устройство, функциональная схема; на фиг. 2 приведен вариант выполнения его электрической схемы.

Предлагаемое устройство (фиг. 1 ) cone æèã регистр 1 сдвига, блок ". свертки по модулю, коммутатор 3, триггер 4 контрольного разряда, блок 5 управления режимом свертки, информационные шины

6 и 7, шина 8 синхронизации, шины 9 и

10 управления и выход 11 устройства.

На принципиальной схеме (фиг.2) приведен 12-разрядный регистр 1 на 3-х элементах 133 НР1, блок 2 свертки на

2-х элементах 133 ИП2, коммутатор 3 (элемент И-ИЛИ-НЕ 133 ЛРЗ), триггера 4 контрольного разряда (ХК -триггер 133 ТВ1), блока 5 управления три элемента ЗИ-НЕ 133 ЛА4.

Запись информации в регистр. и триггер производится по отрицательному перепаду на входах синхронизации.

Принцип работы устройства заключает ся в следующем.

В режиме сдвига на шине 9 управления присутствует уровень логической 1 а на шине 10 управления — уровень логического «О, На шине 8 синхронизации положительный полупериод такта будет также ур овен ь 1 . Высокие потенциалы на управляющих входах блока 5 разрешают прохождение инвертированных значений сигнала старшего разряда регистра 1 сигнала последовательного входа регистра и контрольного разряда на входы блока:

2 свертки, на другие входы которого поступают текущие значения сигналов всех разрядов регистра .1. При сложении по модулю два пр ям ые и ин ве рси ые эн а чен ия сигналов старшего разряда регистра 1 и контрольного разряда дают логические

" 1, а . в сумме — логический 0". Посколькуу на вход блока 2 свертки с шины 6 поступает будущее значение младшего разряда регистра 1, то тем самым в положительный полупериод такта на выходе блока 2 свертки формируется значение четности будущего такта, которое через коммутатор 3, открытый управляющим сигналом, поступает на вход триггера 4 контрольного разряда. По окончанию положительного полупериода такта (отрицательному фронту) происходит запоминание значения четности будущего такта в триггере 4 и изменение информации в регистре 1 сдвига, В отрицательный полупериод такта на входы блока 2 свертки поступают новые значения сигналов разрядов регистра 1 сдвига. В отрица ельный полупериод такта на входы блока 2 свертки поступают новые значения сигналов разрядов регистра 1 сдвига. На шине 8 синхронизации и, соответствлп о, 8 09."-1 86 нв входе блока 5 управления присутствует уровень логического О, тем самым обеспечивая прохождение на вход блока

2 свертки некомпенсированного значения сигнала контрольного разряда с выхода триггера 4. Таким образом на выходе блока 2 формируется свертка по модулю, свертка разрядов регистра 1 и контрольного разряда, которая определяет правильность работы регистра 1 в режиме сдвига.

В режиме параллельного приема информации на шине 10 — уровень логического

О, а на шине 9 и управляющих входах блока 5 и коммутатора 3 присутствует уровень логического О, тем самым разрешая по отрицательному перепаду на шине 8 синхронизации запись значения контрольного разряда с шины 7 через коммутатор 3 и триггер 4 и прохождение значения контрольного разряда через блок 5 на вход блока 2 свертки. На другие входы блока 2 свертки поступают значения разрядов регистра 1, поэтому блок 2 формирует свертку по модулю два раз- рядов регистра 1 и контрольного разряда тем самым характеризуя прввильt ность работы регистра 1 в режиме параллельного приема или хранения информации

В режиме последовательного приема информации пнв шину 9 и на шину 10 коммутатора 3 поступает уровень логической

1, разрешая тем самым прохождение на вход триггера 4 значения старшего разряда регистра 1 сдвига, из которого (й +1)-м импульсом синхронизации выталкивается контрольный разряд последо- . вательного кода. В отрицательный полупериод (n +1)-ro импульса происходит формирование свертки разрядов принятого последовательного кода и его контрольного разряда, обеспечивая тем самым контроль при последовательном приеме информации.

Эффективность приложенного устройства сдвига с контролем заключается в упрощении контрольного оборудования (один триггер, три логических элемента

И-НЕ, элемент И-ИЛИ-НЕ по сравнению с двумя одноразрядными счетчиками, тремя двухвходовыми суммвторамк по модулю два и регистром памяти в прототипе) и в расширении области применения устройства, т.е. возможен контроль при параллельном и последовательном приеме и хранении информации, что достигается за чет переключения режимов работы блока свертки в положительный и отрицательный полупериоды такта и переключений каналов коммутатора. Блок свертки при этом несет двойную функциональную нагрузку: формирует значение свертки будущего такта и определяет исправность работы регистра.

Упрощение контрольного оборудования одновременно повышает достоверность контроля устройства в целом.

Предложе ие построения устройства помимо того способствуег повышению оперативности контроля, поскольку задер.жка в формировании сигнала на контрольном выходе определяется только блоком

10 свертки, а не четырьмя устройствами, как это происходит в прототипе.

Формула изобретения

Устройство для сдвига со встроенным контролем, содержащее блок свертки по модулю два, первые входы которого соединены с выходами регистра сдвига, триггер контрольного разряда, первый вход которого соединен с первым входом регистра сдвига и шиной синхронкэации, вторые входы регистра слзигв подключены соответственно к первой шине управ30 ления и к первой информационной шине, третий вход регистра сдвига подсоедин Л ко второй информационной шине, î r л ич а ю щ е е с я тем, что, с целью упро= щения устройства и расширения области

3$ его применения за счет осуществления возможности контроля в режиме записи и хранения информации; в него введены коммутатор и блок управления режимом свертки, выходы которого соединены со

40 вторыми входами блока свертки по модулю два, выход коммутатора подключен ко второму входу триггера контрольного разряда, выход которого соединен с первым входом блока упрввленкя режимом свертки, первый вход коммутатсра подключен

4$ ко второй информационной шине, второй вход коммутатора соединен с одним из выходов регистра сдвига и вторым входом блока управления режимом свертки, третий вход которого подсоединен к первой информационной шине, выход блока свертки по модулю два соединен с третьим. входом коммутатора и выходом устройства.

Источники информации, принятые во внимание прк экспертизе

1. Авторское свидетельство СССР

No 630631, кл. С 06 F 11/10, опублик

1 978.

809386.7

2. Каган Б. М. Электронные аьиислительные машины и системы,- Энергии .

М., 1979, с. 437.

3. Патент США М 35679l 6, кл. 235-153, опублик. 1971 (нрототип).

Ôèñ.1

809386

Составитель А. Воронин

Редактор А. Власенко Техред H.Êoâàëåâà Корректор Е. Рошко

Заказ .14 1/69 Тираж 65G Подписное

ПНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

<филиал ППП "Патент", г. Ужгород, ул, Проектная„4