Запоминающее устройство

Иллюстрации

Показать всеРеферат

< 809394

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (6l ) Дополнительное к авт. свид-ву (22)Заявлено 23.08.78(2l) 2659112/18-24 с ттесоединеннем заявки Ж (23) Приоритет— (5! )М. Кл.

G ll.С 29/00

Гасударственный кемнтет

СССР

Опубликовано 28,02.81. Бюллетень Рй 8

llo делам изобретений и етнрытнй (53) УДК 681.327..6 (088.8) Дата опубликования описания 03.03.81 с »= ». :

Р. В. Акопов, О. А. Терзян и Л. М. Чахоян Ж.4Й" 1 (72) Авторы изобретения ь 4 7 V f т3 т!»

",", (д м;p,, -,, : >Qji .- :- s, ° „ (7l) Заявятель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике и может использоваться в системах обработки информации.

Йля повышения надежности запоминающих устройств (ЗУ) применяют замену отказавших ячеек памяти резервными, расположенными в дополнительном ЗУ малой емкости t 1).

Известно ЗУ с преобразованием кодов адресов неисправных ячеек памяти, содержащее три накопителя, счетчик, М-разрядто ный входной регистр, Я выходов которого соединены с адресными входами первого накопителя, а (М-N ) его выходовс адресными входами второго накопителя.

Выходы первого и второго накопителей

l$ соединены с адресными входами третьего накопителя. На вход счетчика поступает сигнал ошибки, а его выходы подключены к информационным входам всех грех

?о накопителей, Выходы третьего накопителя являются выходами устройства (2).

Однако это устройство является относительно сложным, что определяется нали2 чнем трех накопителей, причем емкость последнего резко возрастает с увеличением числа преобразуемых адресов.

Бель изобретения — упрощение устройства.

Указанная цель достигается тем, что в запоминающем устройстве, содержащем входной регистр, входы которого подклю- чены к соответствующим входным шинам кода адресов, накопитель, входы когарогст подключены к входной шине обнаружения ошибки и соответствующим выходам вхсеного регистра, блок сравнения, счетчик, первый вход которого подключен к входной шине сигнала обращения, элемент И и входные шины, входы блока сравнения подключены к первым выходам входного регистра и соответствующим выходам накопителя, выход блока сравнения подключен к первому входу элемента И и второму входу счетчика, третий вход которого подключен к соответствующему выходу нако, пителя и второму входу элемента И, вы ходы счетчика подключены к соотвегст809394 вующим адресным входам накопителя,,, причем другие выходы входного регистра, выход элемента И и выходы счетчика соединены с соответствующими выходными шинами устройства.

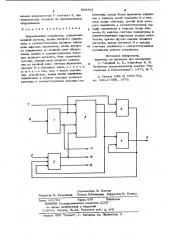

На чертеже представлена блок-схема запоминающего устройства с преобразованием кода адреса.

Устройство содержит входной регистр 1, накопитель 2, блок 3 сравнения, элемент И 4, счетчик 5. Вход 6 устройства, являющийся первым входом счетчика, подключен к шине сигнала обращения, а вход 7 устройства, являющийся вторым информационным входом накопителя 2, подключен к выходу блока для обнаружения ошибки (на чертеже не по мазано). М входов 8 регистра 1 подключены к шинам преобразуемого кода адреса. Д выходов регистра 1 подключены к первым адресным входам накопителя 2 и к выходам 11 устройства. Остальные (М -й ) выходов регистра 1 подключены к первым информационным входам накопителя 2 и к первым входам блока 3, вторые входы которого подключены к первым выходам накопителя 2. Выход блока 3 подключен к первому входу элемента И 4 и ко второму входу счетчика 5, третий вход которого подключен ко второму входу элемента

И 4 и ко второму выходу накопителя 2, а выход элемента И 4 подключен к выходу 9 устройства. Первые P выходов счетчика 5 подключены ко вторым адресным входам накопителя 2 и к выходам 10 устр ойства.

Выходы 10 и 11 являются выходами преобразованного кода адреса, а выход 12 является выходом сигнала переполненн ия.

Устройство работает следующим образом.

Предполагается, что имеется блок для обнаружения ошибок и что в исходном состоянии во всехраэрядных счетчиках 5 и ячейкахнакопителя 2 записаны нули.При обращении к ЗУ его М разрядов кода адреса подеются на регистр 1 через входы 8, а сигнал обращения к ЗУ поступает на вход 6 устройства. Счетчик 5 каждый раз при поступлении сигнала обращения на

Р вход 6 начинает перебор всех своих 2 состояний, начиная с нулевого. Причем после установки каждого нового состояния счетчика 5 происходит считывание информации из накопителя 2. Счетчик

5 прекращает свою работу либо при появлении сигнала совпадения на выходе блока 3, либо при отсутствии единицы на втором выходе накопителя 2, либо после окончания перебора.

При возникновении ошибки в считанном из ЗУ слове блок для обнаружения ошиб-, ки посылает на вход 7 устройства сигнал ошибки (логическая единица), К этому времени на всех первых P выходах счетчика 5 устанавливаются нули, так как на его третий вход со второго информацион10 ного выхода накопителя 2 поступает нулевой сигнал. Это нулевое состояние счетчика 5 (все нули на первых P выходах) передается на вторые адресные входы, а Я разрядов кода адреса через регистр 1 — на первые адресные входы накопителя 2 и в ячейку накопителя 2, адресуемую (+Р) разрядами, записываются (М вЂ” М ) состояний выходов регистра 1 и единица (сигнал ошибки) на входе 7.

20 Если в той же группе слов, определяемой состоянием Я разрядов кода адреса, при возникновении первой ошибки возникает другое неисправное слово, то блок для обнаружения ошибки опять вы25 дает на вход 7 сигнал ошибки. При пос,туплении на вход 6 сигнала обращения к

ЗУ на выходе блока 3, как и в предыдущем случае, не будет сигнала совпадения, однако на третьем входе счетчика 5 со

3о второго выхода накопителя 2 будет уста новлена единица. Поэтому счетчик 5 перейдет в единичное состояние. При этом происходит считывание информации из ячейки накопителя 2, в которой ничего не записано, и на третий вход счетчика

5 поступает нулевой сигнал, который и остановит его работу. Лалее повторяется процесс записи (М-Й ) разрядов регистра 1 в данную свободную ячейку на40 копителя 2.

При повторном обращении к ЗУ по неисправному адресу счетчик . 5, начав перебор,остановится по сигналу совпадения на выходе блока 3. При этом на втором

15 выходе накопителя 2 будет установлена единица, и элемент И 4 выдаст на выход

9 сигнал обнаружения неисправного преобразуемого кода адреса, а на выходах

10 и 11 устройства установится преобразованный код адреса.

Если число преобразуемых адресов в какой-либо группе станет больше 28, то счетчик 5 выдает на выход 12 сигнал пер еполнения.

Таким образом, предлагаемое устройство позволяет автоматически преобразо-. вывать любое заданное количество адресов в каждой группе на 2 адресов, опрецеи

809394

Составитель В. Костин

Редактор Н. Безродная Техред Н.Koaanesa Корректор В. Бутяга

Заказ 441/64 Тирад 656 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д» 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 ляемое разрядностью Р счетчика 5, при минимальных затратах на дополнительное оборудование.

Формула изобретения

Запоминающее устройство, содержащее. входной регистр, входы которого подключены к соответствуюшим входным шинам кода адресов, накопитель, входы котарого подключены ко входной шине обнаружения ошибки и соответствующим выходам входного регистра, блок сравнения, счетчик, первый вход которого подключен ко входной шине сигнала обращения, элемент И и выходные шины, о т л и ч аю ш е е с я тем, что, с целью упрощения устройства, входы блока сравнения подключены к первым выходам входного регистра и соответствующим выходам накопителя, выход блока сравнения подключен к первому входу элемента И и второму входу счетчика, третий вход которого подключен к соответствующему выходу-. накопителя и второму входу элемента И, выходы счетчика подключены к соответствующим - адресным входам накопителя, причем другие выходы входного регистра, выход элемента И и выходы счетчика соединены с соответствующими выходными шинами устройства.

Источники информации принятые во внимание при экспертизе

1. Городний А. А., Корнейчук В. И, Проблемы высоконадежной памяти.—. Автоматика и телемеханика", 1977, N 7.

2. Патент США N 3992702, кл. 340-173ВВ, 1976;