Устройство для контроля блокапостоянной памяти

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 030579 (21) 2761510/18-24 (51) М. КЛ.

G 11 С 29/00 с присоединением заявки М (23) Приоритет

Государственный комитет

СССР по делам изобретений и открытий

Опубликовано 28.0281 Бюллетень No 8

Дата опубликования описания 08. 03. 81 (53) УДК 681.327 (088.8) И.В.Огнев, Г.A.Бородин, Ю.М.Шамаев, Н.И.Егорова и A.Ê.Ñòîëÿðoâ (72) Авторы изобретения

Московский ордена Ленина энергетический йнститут (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКА ПОСТОЯННОЙ

ПАМЯТИ

Изобретение относится к запоминающим устройствам и может быть применено для контроля блоков постоянной памяти, выполненных на интегральных запоминающих микросхемах словарного типа.

Известно устройство для контроля блока постоянной памяти, в котором выполняется вычисление контрольной суммы вместе с вычислением поразрядных сумм по модулю два 311.

Недостатком этого устройства является то, что оно не обеспечивает обнаружения многократных четных ошибок. 15

Из известных устройств наиболее близким к предлагаемому является устройство, которое реализует проверку на четность Хемминга, для чего информация из блока постоянной памя- 20 ти считывается поразрядно, и свертка по Хеммингу осуществляется для каждого из разрядов информационного содержимого блока постоянной памяти.

Устройство позволяет определять адрес и разряд одиночной ошибки и обнаруживать нечетные многократные ошибки 12).

Недостаток известного устройства — невысокая точность контроля 30 при возникновении многократных четных ошибок, появляющихся при отказах запоминающих микросхем, а также большая длительность контроля и значительный объем памяти для хранения контрольной информации, что снижает быстродействие и надежность устройства.

Цель изобретения — повышение точ" ности контроля, надежности и быстродействия устройства.

Поставленная цель достигается тем, что в устройство для контроля блока постоянной памяти, содержащее блок устаноВки контрольных чисел, схему сравнения, блок полусумматоров и блок управления, первый, второй и третий выходы которого соединены соответственно с выходом устройства, с управляющим входом схемы сравнения и с управляющим входом блока полусумматоров, выход которого подключен к первому входу схемы сравнения, второй вход которой соединен с выходом блока установки контрольных чисел, а выход — co входом блока управления, введены блок многоразрядных сумматоров, выходы которого подключены ко входам бло809396 ка полусумматоров, а входы соединены со входами устройства.

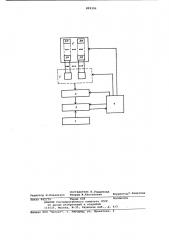

На чертеже изображена структурная схема устройства.

Устройство содержит блок 1 установки контрольных чисел, схему 2 сравнения, блок 3 полусумматоров, блок

4 управления и блок многоразрядных сумматоров 5. Первый, второй и третий выходы блока 4 управления соединены соответственно с выходом устройства, с управляющим входом схемы 2 сравнения и с управляющим входом блока 3 полусумматоров, выход которого подключен к первому входу схемы 2 сравнения. Второй вход схемы

2 сравнения соединен с выходом блока 1 установки контрольных чисел, а выход — co входом блока 4 управления. Выходы блока 5 многоразрядных сумматоров подключены ко входам блока 3 полусумматоров, а входы 2О соединены со входами устройства.

Выход и входы устройства подключены соответственно ко входу и к выходу контролируемого блока 6 постоянной памяти, выполненного на запомина- 25 ющих микросхемах (ЗМ) .

Устройство работает следующим образом.

Блок 4 управления вырабатывает и выдает на вход 6 блока — постоянной памяти импульсы обращения и последовательность кодов адреса для выборки запоминающих микросхем в соответствии с позициями систематического кода Хемминга, причем адреса слов в пределах информационной емкости запоминающей микросхемы выбираются последовательно, т.е. выбирается первый ряд микросхем и последовательно перебираются адреса слов, относящихся к первому ряду. 40

Считываемая информация суммируется методом контрольного суммирования в блоке 5 многоразрядных сумматоров.

После окончания выбора адресов из первого ряда ЗМ полученные в блоке многоразрядных сумматоров 5 суммы поразрядно складываются в блоке

3 полусумматоров. Затем выполняется считывание из всех последующих нечетных рядов запоминающих микросхем.

После определения суммы каждого ряда и поразрядного сложения этих сумм в блоке 3 полусумматоров образуется поразрядная сумма контрольных сумм нечетных рядов ЗМ. Схемой 2 сравнения выполняется сравнение полученной поразрядной суммы с первым контрольным числом, поступающим из блока 1 установки контрольных чисел.

Затем выбирается информация из второго, третьего, шестого, седьмого и ф) так далее рядов запоминающих микросхем (в соответствии со вторим признаком кода Хемминга), ее поразрядное сложение в блоках 5 и 3 и сравнение полученной поразрядной суммы с контрольным числом схемой 2 сравнения.

Аналогично выполняются циклы для получения поразрядных сумм в соответствии с третьим, четвертым и так далее признаками кода Хемминга.

При отказе какой-либо запоминающей микросхемы изменяется значение соответствующей поразрядной суммы, и определяется ряд, содержащий

ЗМ, в которой произошел отказ. Искажение одной из контрольных сумм в блоке 5 многоразрядных сумматоров указывает столбец с отказавшей ЗМ.

Таким образом определяется адрес отказавшей запоминающей микросхемы, Предлагаемое устройство обеспечивает контроль блока долговременной памяти на интегральных запоминающих микросхемах словарного типа, для которых при отказах характерны четные многократные асимметричные ошибки, и определение адреса отказавшей ЗМ, а также снижение объема памяти, необходимой для хранения контрольной информации, эа счет чего повышается точность контроля и надежность устройства. Кроме того, в предлагаемом устройстве контроль всех разрядов выполняется одновременно, что увеличивает быстродействие устройства.

Формула изобретения

Устройство для контроля блока постоянной памяти, содержащее блок установки контрольных чисел, схему сравнения, блок полусумматоров и блок управления, первый, второй и третий выходы которого соединены соответственно с выходом устройства, с управляющим входом схемы сравнения и с управляющим входом блока полусумматоров, выход которого подключен к первому входу схемы сравнения, второй вход которой соединен с выходом блока установки контрольных чисел, а выход — со входом блока управления, о т л и ч а ю щ е е с я тем, что, с целью повышения точности контроля, надежности и быстродействия устройства, оно содержит блок много— разрядных сумматоров, выходы которого подключены ко входам блока полусумматоров, а входы соединены со входами устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 413530, кл. G 11 С 29/00, 1974.

2. Авторское свидетельство СССР

9 273281, кл. G 11 С 20/00, 1969 (прототип).

809396 г

I 5

Эаказ 442 70 Тираж 656

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Филиал ППП Патент", r. Ужгород, ул. Проектная, 4

Составитель В.Гордонова

Редактор И.Ковальчук Техред Ж.Кастелевич КорректорГ. Решетник