Запоминающее устройство с само-контролем

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик р>809398

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. сеид-ву (53)М. Клз

G 11 С 29/00 (22) Заявлено 180579 (21) 2768159/18-24 с присоединением заявки ¹ (23) Приоритет

Опубликовано 280231. Бюллетень № 8

Дата опубликования описания 08. 03. 81

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 681. 327

{088.8) И.П.Дробязко, Л.С.Кениг, В.И.Корнейчук,, С.В;Кучер, N,H.Oðëîâà и В.Я.Юрчишин (72) Авторы изобретения

Киевский ордена Ленина политехнический инстйтут; им. 50-летия Великой Октябрьской социалистической революции (71) Заявитель

{54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ

Изобретение относится к запоминающим устройствам.

Известно устройство, содержащее одноступенчатые сдвиговые регистры, выходы которых подключены к входному регистру, счетчик, один из входов которого подключен к схеме управления, двухступенчатый регистр, дешифратор, группу схем .управления, входы которой подключены к выходам дешифратора, один из выходов — к другому входу счетчика, другие выходы — ко входам двухступенчатого регистра, выходы которого соединены с шинами сдвига и гашения одноступенчатых регистров, выход счетчика подсоединен ко входу дешифратора 1.1).

Недостатком этого устройства является низкая надежность его работы.

Наиболее близким техническим решением к предлагаемому является запоминающее устройство с самоконтролем, содержащее ряд сдвиговых накопителей, соединенных последовательно между собой, схему контроля, подключенную ко входу и выходу каждого накопителя, и блок управления ?3.

Недостатком этого устройства является то, что при наличии отка зов в сдвиговых накопителях значительная часть устройства не участвует в работе, что снижает надеж ность устройства.

Цель изобретения - повышение надежности устройства.

Поставленная цель достигается тем, что в запоминающее устройство с самоконтролем, содержащее накопители, блок управления и блок обнаружения отказов, входы которого подключены к выходам, а одни из

15 выходов - ко входам кода отказа соответствующих накопителей, одни из выходов блока управления соединены соответственно с управляищи" ми входами накопителей и блока об20 наружения отказов, адресный вход первого накопителя подключен ко входу устройства, введены коммутаторы, регистры сдвига и дешифраторы — по числу накопителей, и формирователь кодовых сигналов сдвига причем первый вход каждого коммутатора соединен с выходом одноименного накопителя, а выход каждого коммутатора кроме

30 последнего — co входом последу809398 ющего накопителя, выход последнего коммутатора подключен к выходной шине устройства и входу первого накопителя, вторые входы коммутаторов соединены с выходами одноименных дешифраторон, входы каждого из которых подключены к первому выходу одноименного регистра сдвига, первый вход каждого предыдущего регистра сдвига, кроме последнего, соединен со вторым выходом последующего регистра сдвига, первый вход последнего регистра сдвига подключен к выходу формирователя кодовых сигналов сдвига вход которого соединен с другим выходом блока обнаружения отказов, вторые входы регистров сдвига и управляющие входы коммутаторов, формирователя кодовых сигналов сдвига и дешифраторон подключены к другим выходам блока управления соответственно.

При этом формирователь кодовых сигналов сдвига целесообразно выполнить содержащим два регистра, вычитатель, три элемента И, дна триггера и счетчик, причем выходы регистров подключены соответственно к первому и второму входам вычитателя, первый выход которого соединен с первыми входами первого и второго элементов И, выходы которых подключены соответственно ко входам первого триггера, единичный выход которого соединен со вторым входом второго элемента И,первым входом третьего элемента И и первым входом второго триггера, единичный выход которого подключен ко второму входу первого элемента И, выход третьего элемента

И соединен с первым входом счетчика, вторые нходы третьего элемента

Ии счетчика подключены ко второму выходу нычитателя, входы регистров, вторые вход второго триггера и выход вычитателя, третий вход вычитателя и выход счетчика соединены соответственно с входом, управляющим входом и выходом фсрмирователя кодовых сигналов сдвига.

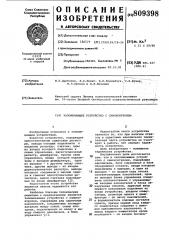

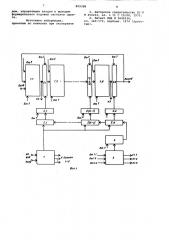

На фиг. 1 изображена функциональная схема предлагаемого устройства; на фиг. 2 — схема формирователя кодовых сигналон сдвига.

Устройство содержит (фиг. 1) накопители 1.1-1.N, коммутаторы 2.1-2.N блок 3 обнаружения отказов, формирователь 4 кодоных сигналов сдвига, регистры сдвига 5.1-5.N дешифраторы 6.1-6.N и блок 7 управления.

Входы блока 3 обнаружения отказов подключены к выходам, а одни из выходов — к входам кода отказа соответствующих накопителей 1.1-1.N.

Одни из выходов блока 7 управления соединены соответственно с управляющими входами накопителей 1.1-1.1 и блока 3 обнаружения отказов. Адресный вход первого накопителя

1.1 подключен ко входу устройства.

Пернь1й вход каждого коммутатора

2.1-2.N соединен с выходом одноименного накопителя 1.1-1.N, а выход каждого коммутатора 2.1-2.N, кроме последнего — с входом последующего накопителя 1.2-1.N. Выход последнего коммутатора 2.N подключен к выходной шине устройства и входу первого накопителя 1.1. Вторые входы коммутаторов 2.1-2.й соединены с выходами одноименных дешифраторов

6.1-6.N, входы каждого из которых подключены к первому выходу одноименного регистра сдвига 5.1-5.N.

15 Первый вход каждого предыдущего регистра сдвига 5.1-5.N, кроме последнего, соединен со вторым ныходом каждого последующего регистра сдниraN. Первый вход последнего щ регистра сдвига 5.й подключен к выходу формирователя 4 кодовых сигналов сдвига, вход которого соединен с другим выходом блока 3 обнаружения отказов. Вторые входы регистров сдвига 5.1-5.N, управляющие входы коммутаторов 2.1-2.N, формирователя 4 кодовых сигналов сдвига и дешифраторов

6.1-6.N подключены к другим выходам блока 7 управления соответственно.

При этом формирователь 4 кодовых сигналов сдвига выполнен содержащим (фиг. 2) первый 4.1 и второй 4.2 регистры, вычитатель 4.3, первый

4.4 и второй 4.5 элементы И первый триггер 4.6, третий элемент 4.7 И, второй триггер 4,8 и счетчик 4.9.

Выходы регистров 4.1 и 4.2 подключены соответственно к первому и второму входам вычитателя 4.3, 40 первый выход которого соединен с первыми входами первого 4.4 и второго 4.5 элементов И. Выходы элементов И 4.4 и 4.5 поключены соответственно к входам первого триггера 4.6, единичный выход которого соединен со вторым входом второго элемента 4.5 И, первым входом третьего элемента 4.7 И и первым входом второго триггера 4.8. Единичный выход второго триггера 4.8 подключен ко второму входу первого элемента 4.4 И. Выход третьего элемента 4.7 И соединен с первым; входом счетчика 4.9. Вторые входы третьего элемента 4.7 И и счетчика

4.9 подключены ко второму выходу вычитателя 4.3. Входы регистров 4.1 и 4.2, вторые вход второго триггера

4.8 и выход вычитателя 4.3, выход счетчика 4.9 и третий вход вычитаdG теля 4.3 соединены соответственно со входом, управляющим входом и выходом формирователя 4 кодоных сигналов сдвига.

Устройство работает следующим б5 образом.

809398

Перед началом работы проводится тестовый контроль, при котором выясняется, в каких разрядах накопителей 1.1-1.N произошли отказы.

Блок 7 управления (фиг. 1) поочередно подключает входы и выходы накопителей 1.1-1.N к блоку 3 обнаружения отказов, который вырабатывает код отказа. В этом коде отказавшие разряды накопителей 1.1-1.М отмечаются единицами, работающие разряды — нулями. Код отказа поступает в формирователь 4 кодовых сигналов сдвига, который вырабатывает код сдвига информации с учетом отказавших разрядов накопителей 1.1-1.й, Коды отказа накопителей 1.1-1.N с блока 3 обнаружения отказов поступают соответственно на регистры

4.1 и 4.2 (фиг. 2). Коды с обоих регистров поступают на вычитатель

4.3 и,после вычитания первого кода 20 из второго, знак результата, определяющий направление сдвига, поступает в старший разряд регистра сдвига 5.N (фиг. 1). Содержимое вычитателя 4.3 сдвигается вправо 25 и первая единица, поступившая на вход первого элемента 4.4 И, устананливает первый триггер 4.6 в единичное состояние, открывая третий элемент 4.7 И, и тактовые импульсы поступают на счетчик 4.9. Вторая единица, поступившая с вычитателя

4.3, через открытый второй элемент

4.5 И устанавливает второй триггер

4.6 в нулевое состояние и закрыва35 ет третий элемент 4.7 И. Затем значение счетчика 4.9 переписывается в регистр 5.N сдвига. Определяются коды сдвига для всех накопителей

1.1-1.N. .С регистров сдвига 5.1-5.N коды сдвига поступают на соответ- 40 ствующие дешифраторы 6.1-6.N. Коммутаторы 2.1-2.N в соответствии с выходными сигналами дешифраторов

6.1-6.IJ переключают выходные и входные шины накопителей 1.1-1.й та- 45 ким образом, что отказавший разряд предыдущего из накопителей

1.1-1.N подключается к отказавшему разряду последующего из накопителей 1.1-1.N. Технико-экономическое преимущество предлагаемого устройства заключается в том, что оно позволяет обнаруживать неработающие ячейки накопителей и перестраивать схему их соединения таким образом, что все единичные отказы в накопителях не влияют на работу запоминающего устройства, что повышает его надежность.

2. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что формирователь кодовых сигналов сдвига содержит два регистра, вычитатель, три элемента И, дна.триггера и счетчик, причем выходы регистров подключены соответственно к первому и нторому входам вычитателя, первый выход которого соединен с первыми входами первого и второго элементов И, выходы которых подключены соответственно ко входам первого триггера, единичный выход которого соединен со вторым входом второго элемента И, первым входом третьего элемента И и первым входом второго триггера, единичный выход которого подключен ко второму входу первого элемента И, вы ход третьего элемента И соединен с первым входом счетчика, вторые входы третьего элемента И и счетчика подключены ко второму выходу нычитателя, входы регистров, вторые вход второго триггера и выход вычитателя, третий вход вычитателя и выход счетчика соединены соответственно с вхо60

Формула изобретения

1. Запоминающее устройство с самоконтролем, содержащее накопители, блок управления и блок обнаружения отказов, входы которого подключены к выходам, а одни из выходов — ко входам кода отказа соответствующих накопителей, одни из выходов блока управления соединены соответственно с управляющими входами накопителей и блока обнаружения отказов, адресный вход первого накопителя подключен ко входу устройства, о ти и ч а ю ш е е с я тем, что, с целью повышения надежности устройства, оно содержит коммутаторы, регистры сдвига и дешифраторы — по числу накопителей, и формирователь кодовых сигналон сдвига, причем первый вход каждого коммутатора соединен с выходом одноименного накопителя, а выход каждого коммутатора, кроме последнего, — co входом последующего накопителя, выход последнего коммутатора подключен к выходной шине устройства и входу первого накопителя, вторые входы коммутаторов соединены с выходами одноименных дешифраторсв, входы каждого из которых подключены к первому выходу одноименного регистра сдвига, первый вход каждого регистра сдвига, кроме последнего, соединен со вторым выходом последующего регистра сдвига, первый вход последнего регистра сдвига подключен к выходу формирователя кодовых сигналов сдвига, вход которого соединен с другим выхо- дом блока обнаружения отказов, вторые входы регистров сднига и управляющие входы коммутаторов, формирователя кодовых сигналов сдвига и дешифраторов подключены к другим выходам блока управления соответственно. дом, управляющим входом и выходом формирователя кодовых сигналов сдвига.

Источники информации, принятые Во внимание при экспертизе

809398

1. авторское свидетельство СС< .р

9 450233, кл. G 11 С 19/00, 1975.

2. Патент СБА Р 3646536, кл. 340-173у опублик. 1974 (прототип).

809398 к н

9 è . 2

Составитель Т.Зайцева

Редактор Н.Кузнецова Техред М.Голинка Корректор Г.Назарова

Заказ 442 70 Тираж 656 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент, r. Ужгород, ул. Проектная,