Запоминающее устройство с авто-номным контролем

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик р>809403

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. саид-ву (51)М. К.з

G 11 С 29/00 (22) Заявлено 14.06. 78 (21) 2782255/18-24 с присоединением заявки ¹ (23) Приоритет

Опубликовано 280231i Бюллетень № 8

Дата опубликования описания 08 - 03 ° 81

Государственный комитет

СССР ио делам изобретений и открытий (53) УДК 681.327..6(088 ° 8) (72) Авторы изобретения

ГИ.В.Огнев, Ю.М.Шамаев, К.Ф.Сарычев и Н.И.Гарбузов

I (71) Заявитель

Московский ордена Ленина энергетическ и институт (54) ЗАПОМИНАКМЦЕЕ УСТРОЙСТВО С АВТОНОМНЫМ

K0HTP0JIEN

Изобретение относится к запоминающим устройствам.

Известно запоминающее устройство с автономным контролем, содержащее накопители, схемы формирования контрольных разрядов, схемы формирования проверочного слова, дешифратор одноразрядных ошибок и схему обнаружения двухразрядных пакетных ошибок 51).

Недостатком этого устройства является невозможность обнаружения многоразрядных ошибок.

Наиболее близким к предлагаемому является запоминающее .Устройство с автономным контролем, содержащее накопители, формирователь контрольных разрядов кода Хзмминга, формирователи проверочного слова, дешифратор одноразрядных ошибок, блок обнаружения двухкратных ошибок, входные и выходные формирователи четности, сумматор и элемент ИЛИ. Информационные входы накопителей соединены с входными, а выходы - с выходными шинами, одни входы формирователей контрольных разрядов кода Хэмминга подключены к входным шинам, другие входы — к выходам входных формирователей четности и к одним контрольным входам, а выходы — к другим контрольным входам накопителей, входы формирователей проверочного

5 слова соединены с выходами накопителей, а выходы — с одними входами дешифратора одноразрядных ошибок и схемы обнаружения двухкратных ошибок, другие входы которых подключены к выходам выходных формирователей четности, входы сумматора соединены с выходами первой группы выходных формирователей четности, один из входов элемента ИЛИ подключен к выходу схемы обнаружения двойных ошибок (23.

К недостаткам известного устройства следует отнести большое число контрольных разрядов при обнаружении многоразрядных пакетных ошибок, которые могут возникнуть при использовании многоразрядных блоков памяти с разрядностью Ьсг/2 - 1, где г - число контрольных разрядов, необходимых для исправления одноразрядных ошибок.

Цель изобретения — упрощение устройства за счет уменьшения числа контрольных разрядов накопителя.

Поставленная цель достигается тем, что в запоминающее устройство

809403 с автономным контролем, содержащее накопитель, информационные входы и выходы которого являются информационными входами и выходами устройства, первый формирователь, выходы которого подключены к первым входам накопителя, а первые входы — к информационным входам устройства, второй формирователь, входы которого подключены к инАормационным входам устройства, а выходы-ко вторым входам первого Аормирователя и ко вторым входам накопителя, третий формирователь, входы которого подключены к первым выходам накопителя, а выходы — к первым входам дешифратора, четвертый формирователь, входы которого подключены ко вторым выходам накопителя, а выходы — ко вторым входам дешиАратора и ко входам первого сумматора, блок контроля, первые входы которого подключены к выходам третьего формирователя, вторые входы — к выходам четвертого формирователя, а выход блока контроля подключен к первому входу элемента ИЛИ, введены второй сумматор, входы которого подключены к выходам четвертого формирователя, и элемент

И, первый и второй входы которого подключены соответственно к выходам первого и второго сумматоров, а его выход подключен ко второму входу элемента ИЛИ.

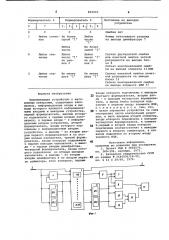

На фиг. 1 изображена схема устройства; на фиг. 2 — Н-матрица используемого корректирующего кода.

Устройство содержит накопитель

1, в данном случае состоящий из

24-х 4-х разрядных блоков памяти, входные и выходные шины 2 и 3 соответственно, первый формирователь

4, второй формирователь 5, третий формирователь 6, дешифратор 7, блок

8 контроля, четвертый Аормнрова тель 9, первый сумматор 10, элемент

11 ИЛИ, второй сумматор 12, элемент

13 И.

Схема подключения числовых входных шин 2 к первому формирователю

4 контрольных разрядов кода Хэмминга, ко вторым формирователям 5 четности, а также выходов формирователей 4 и 5 к входам накопителя 1 и выходов накопителя 1 к входам третьего 6 и четвертого 9 формирователей показана посредством Н-матрицы кода (фиг. 2). Цифрами 1...88 обозначены информациннные разряды числа

СО, С7, разряды кода Хэмминга, С1 ... С6 — контрольные разряды, образуемые формирователями четности, О, 7 — разряды проверочного слова, образуемые Аормирователем

6 проверочного слова, 1 — 6 — разряды проверочного слова, образуемые выходными Аормирователями 9 четности

Устройство работает следующим образом.

При записи число с входных шин

)g 2 поступает на информационные входы накопителя 1, на входы первого формирователя 4, формирующего контрольные разряды Хэмминга, и на входы второго формирователя 5, формирую щего разряда четности. Формирование контрольных разрядов происходит в соответствии с Н-матрицей (фиг. 2).

Контрольные разряды с формирователей 4 и 5 поступают на контроль () ные входы накопителей 1. При считывании разряды числа из накопителей

1 поступают на третий формирователь

6, формирующий проверочное слово, и на четвертый формирователь 9, фор 5 мирующий выходные разряды четности.

Формирование происходит в соответствии с Н-матрицей (фиг. 2). Формирователь 6 проверочного слова и выходные формирователи 9 четности образуют разряды Π— 6 проверочного слова, которые поступают на дешифратор 7, блок 8 контроля, обнаруживающий двухкратные ошибки, первый и второй сумматоры 10 и 12.

Разряд О проверочного слова с выхо35 да формирователя 6 поступает на дешифратор 7, а разряды О, 7 - на блок 8 контроля. В зависимости от значения разрядов проверочного слова возможны следующие случаи (табли40 ца 1).

Преимущество предлагаемого устройства заключается в том, что оно позволяет уменьшить число контрольных разрядов по сравнению с известным.В ЗУ, разрядность которого кратна четному числу байтов .(8, 16, 32, 64, 128....), предлагаемое изобретение позволяет при минимально возможном количестве контрольных разрядов, равном количеству контрольных разрядов

Хэмминга, обнаруживать пакетные ошибки разрядностью до 4 для 32, 64 и 128 разрядных слов и т.д.,в то время, как известное устройство требует для обнаружения пакетных ошибок с разрядностью 4 для

32, 64, 128 разрядных слов введения одного дополнительного контрольного разряда.

809403

Формирователь 6

Формирователь 9

1, 2, 3 4, 5, 6

Ошибки нет

Любое число

"1"

Любое число

Не более одной "1"

Любое число "1" не равное О

Любое значение

Любое число "1" не равное 0

Не менее двух "1" входы которого подключены к выходам

25 третьего формирователя, вторые входы — к выходам четвертого формирователя, а выход блока контроля подключен к первому входу элемента ИЛИ, о т л и ч а ю щ е е с я тем, что, 30 с целью упрощения устройства за счет уменьшения числа контрольных разрядов, в него введены второй сумматор, входы которого подключены к выходам четвертого формирователя, и элемент

35 И,первый и второй входы которого подключены соответственно к выходам первого и второго сумматоров, а его выход подключен ко второму входу элемента ИЛИ.

Формула изобретения

Запоминающее устройство с автономным контролем, содержащее накопитель, информационные входы и вы ходы которого являются информационными входами и выходами устройства> первый формирователь, выходы которого подключены к первым входам накопителя, а первые входы — к информационным входам устройства, второй формирователь, входы которого подключены к информационным входам устройства, а выходы — ко вторым входам первого формирователя и ко вторым входам накопителя, третий формирователь, входы которого подключены к первым выходам накопителя, а выходы - к первым входам дешифратора, четвертый формирователь, входы которого подключены ко вторым выходам накопителя, а выходы — ко вторым входам дешифратора и ко входам первого суйматора, блок контроля, первые

Источники информации, принятые во внимание при экспертизе

1. Патент СшА Р 3893070, кл. 340-196, опублик. 1975.

2. Авторское свидетельство СССР

45 по заявке Р 2646830/18-24, кл. G 11 С 29/00, 1979.

1 Любое значе- Не более ние одной "1"

1 Любое зна- Не менее чение двух "1"

Состояние на выходах устройства

Номер отказавшего разряда на выходе дешифратора 7

Сигнал двухкратной ошибки или пакетной ошибки четной разрядности на выходе блока 8

Сигнал неисправляемой ошибки на выходе элемента 11 ИЛИ

Сигнал пакетной ошибки нечетной разрядности на выходе блока 13

Сигнал неисправляемой ошибки на выходе элемента ИЛИ 11

809403

Составитель В. Гордонова

Редактор Н.Кешеля Техред М.Голинка

КорректорГ.Решетник

42 70 Тираж 656

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ

Подписное

Филиал ППП "Патент", r. Ужгород, ул. Проектная,