Устройство для контроля блоковпостоянной памяти

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

<11>809404

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (51)M. Кл Э

G 11 С 29/00 (22) Заявлено 250679 (21) 2787666/18-24 с присоединением заявки ¹ (23) Приоритет

Опубликовано 2802.81, Бюллетень №

Дата опубликования описания 08 ° 0 ° 81

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 681. Ç27. . 6 (088. 8) (72) Авторы изобретения, Г.A.Áîðîäèí, Н.И.Егорова и А.К.Столяров

Московский ордена Ленина энергетический институт

1 (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ

ПОСТОЯННОЙ ПАМЯТИ

Изобретение относится к вычислительной технике, в частности к устройствам для контроля постоянных запоминающих устройств на интегральных микросхемах памяти.

Известны устройства для контроля блоков постоянной памяти (1) и (2J.

Одно из известных устройств содержит сумматор, регистр сравнения, узел установки контрольных чисел, блок памяти и осуществляет контроль массивов информации по методу контрольного суммирования с циклическим переносом с последующим суммированием единиц переполнения 711.

Устройство. способно обнаруживать однократные и многократные ошибки . с высокой точностью, однако эа счет циклического переноса быстродействие контроля снижается почти в два раза.

Наиболее близким техническим решением к предлагаемому изобретению является устройство для контроля блоков постоянной памяти, которое содержит блок управления, первый выход которого соединен со входом контролируемого блока постоянной памяти, второй выход — с первым входом сумматора-вычитателя, третий †co входом блока установки контрольных чисел, четвертый — с первым входом блока сравнения, второй вход которо5

ro подключен к первому выходу сумматора-вычитателя, вход сумматоравычитателя соединен с выходом контролируемого блока постоянной памяти, выход блока сравнения соединен с первым входом блока управления.

Для осуществления контроля в коды чисел вводится избыточность в качестве разрядов, на основании информации в которых производится переход с режима сложения на режим вычита15 ния и обратно. Последовательность кодовых комбинаций, подлежащих контролю, разбивается на группы, число элементов в которых ограничивается числом разрядов, отводимых для кон20 трольных элементов. Каждой кодовой комбинации присваивается номер, начиная с максимального значения контрольного числа в порядке убывания, и к контрольному числу попеременно прибавляют и вычитают номера всех элементов одного знака.

Полученную таким обраэом сумму вместе с информацией сравнивают с контрольной суммой, которая явля30 ется эталонной 52J.

809404

Недостатком указанного устройства является то, что при обработке информации в режиме сложения или вычитания возможно образование единиц переполнения или заема, которые никак не регистрируются и, следовательно, эта важная информация теряется. Это приводит к тому, что при возникновении многократных асимМетричных детерминированных ошибок (вероятность возникновения которых при отказе запоминающих микросхем велика) нельзя будет их обнаружить, когда они четны. Следовательно, точность контроля при возникновении многократных ошибок будет недостаточной. Кроме того, устройство 5 требует введения избыточности в качестве контрольных элементов, с помощью которых производится переход с режима на. режим, а это снижает надежность работы устройства. 20

Цель предлагаемого изобретения повышение надежности устройства.

Поставленная цель достигается тем, что в известное устройство для контроля блоков постоянной памяти введены реверсивный счетчик и дешифратор, при этом первый вход реверсивного счетчика соединен с третьим выходом блока управления, второй вход — со вторым выходом сумматоравычитателя, а выход — co входом дешифратора, выход которого подключен ко второму входу блока управления.

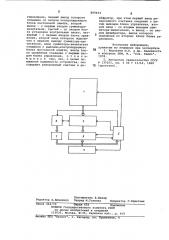

На чертеже представлена блок-схема предлагаемого устройства.

Устройство содержит блок 1 постоянной памяти, сумматор-вычитатель 2, блок 3 сравнения, блок 4 установки контрольных чисел, блок 5 управления, реверсивный "четчик 6, деши- 40 фратор 7.

Устройство работает следующим образом.

При подаче из блока 5 управления на вход блока 1 памяти кода адреса 4 и импульса запроса, числа считываются и поступают на входы сумматоравычитателя 2, где и начинают складываться. Единицы переполнения поступают при сложении в реверсивный счетчик 6, и он меняет свое состояние. Дешифратор 7 в соответствии с состояниями реверсивного счетчика 6 выдает в блок 5 управления инФормацию о его состоянии. Как только состояние счетчика станет равным

01, по сигналу из блока 5 управления сумматор-вычитатель 2 и реверсивный счетчик 6 переводятся в режим вычитания и далее считываемые из блока 1 памяти числа вычитаются. При d0 этом заем происходит из реверсивного счетчика 6. Реверсивный счетчик 6 при вычитании из состояния 01 переходит в состояние 00, а затем в состояние 11. После этого дешифратор Я вычитание

00 вычитание и так далее.

Подобная организация процесса вычисления контрольной суммы приводит к тому, что ни одна единица переполнения (или заема) не будет потеряна и контрольная сумма будет подсчитана быстрее, чем в известных устройствах. В случае построения блока постоянной памяти на интегральных запоминающих микросхемах, при отказах которых велика.вероятность возникновения многократных четных ошибок, все ошибки будут обнаружены, даже если откажет вся микросхема, ибо итоговый результат может быть получен только единственным образом, а в известных устройствах с точностью до модуля A=2 (где М вЂ” разрядность сумматора) за счет потери едийиц переполнения которые отбрасываются. Значит, точность подобного устройства выше, чем у аналогов и прототипа. К тому же устройство не требует введения контрольных элементов для управления переходом с режима на режим, им управляет значение контрольной суммы.

Применение предлагаемого изобретения позволит повысить точность контроля блоков памяти, для которых характерны при отказах запоминающих элементов многократные асимметричные детерминированные ош бкй.

Для обеспечения вероятности обнаружения, близкой к единице, в предлагаемом устройстве не требуется вводить информационную избыточность, что упрощает устройство, повышает надежность его работы и уменьшает стоимость.

Формула изобретения

Устройство для контроля блоков постоянной памяти, содержащее блок

7 выдает в блок 5 управления информацию об этом состоянии реверсивного счетчика б, по которому блок 5 управления переводит сумматор-вычитатель

2 и реверсивный счетчик 6 в режим сложения поступающих чисел. Реверсивный счетчик при сложении переходит в состояние 00, затем в состояние 01 и снова переводится вместе с сумматором-вычитателем 2 в режим вычитания и так далее. Таким образом, режимы работы сумматора-вычитателя

2 и реверсивного счетчика 6 определяются, исходя из состояний реверсивного счетчика 6 по следующему алгоритму:

Пуск-00 — сложение

01

11

00 сложение

809404

Составитель В.Вакар

Редактор A.Âëàñåíêî Техред М.Голинка Корректор Г.Решетник I

Заказ

2 70 Тираж 656 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 управления, первый выход которого соединен со входом контролируемого блока постоянной памяти, второй выход — с первым входом сумматоравычитателя, третий — со входом блока установки контрольных чисел, четвертый — с первым входом блока сравнения, второй вход которого подключен к первому выходу сумматора-вычитателя, вход сумматора-вычитателя соединен с выходом, контролируемого блока постоянной памяти, выход блока сравнения соединен с первым входом блока управления, о т л и ч аю щ е е с я тем, что, с целью повышения надежности устройства, оно содержит реверсивный счетчик и дешйфратор, при этом первый вход реверсивного счетчика соединен с пятым выходом блока управления, второй вход — со вторым выходом сумматора-вычитателя, а выход — co входом дешифратора, выход которого подключен ко второму входу блока управления.

Источники информации, принятые во внимание при экспертизе

1. Журавлев tO.Ï. и др. Надежность и контроль ЭВМ, М., "Сов. Радио", 1978.

2. Авторское свидетельство СССР

9 135105, кл. 0 06 Г 11/12, 1960

15 (прототип).