Цифровой фазовый дискриминатор

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистическик

Республик (61) Дополнительное к авт, сеид-ву— (22) Заявлено 04. 04. 79 (21) 2749247/18-21 ФМ с присоединением заявки ИУ— (23) Приоритет

Н 03 0 13/00

Государственный кеинтет

СССР яа яаиан нзобретений я отярытнй

Опубликовано 2802.81. Бюллетень ИУ 8

Ю) УДп 621. 374. 3 (088; 8) Дата опубликования описания 28. 02. 81 (72) Авторы изобретения

Б. Я. Бурдаев и А. В. Шанин

1 !

/ (71) Заявитель (54) ЦИФРОВОЙ ФАЗОВЫЙ ДИСКРИМИНАТОР

Изобретение относится к импульсной технике.

Известен цифровой фазовый дискриминатор, содержащий полосовой фильтр, триггер Шмитта, формирователь импульсов, одновибратор со сбросом, зле мент И, счетчик импульсов, детектор уровня, одновибраторы задержки, блок заряда, генератор стробирующих им пульсов 11 .

Однако этот дискриминатор не обеспечивает достаточной точности.

Наиболее близким по технической сущности к предлагаемому является фазовый дискриминатор, содержащий два формирователя, первые входы которого соединены со входными шинами, а выходы подключены к первым входам е двух вентилей, выход первого из которых соединен с одним входом первого 20

I триггера, второй вход которого соединен через первый элемент ИЛИ с выходом второго вентиля, а выхоД» которого через третий вентиль, второй вход которого подключен к перво му выходу генератора эталонных импульсов, соединен с одним входом счетчика, второй вход которого соединен с входом регистра памяти и .шиной тактовых импульсов, а выходы 30 разрядов счетчика соЕдинены со вхо дами регистра памяти, вход управления которого подключен к первому входу регистра сдвига, выходу первого элемента И и через первый элемент НЕ к первому входу второго элемента И, второй вход которого соединен с одной из входных шин, со вторым входом регистра сдвига, вторым входом первого элемента ИЛИ, первым входом второго элемента HJIH„ а выход второго логического элемента И подключен к первому входу выходного элемента ИЛИ, второй вход которого соединен с выходом регистра сдвига, причем входы первого элемен та- И соединены с выходами второго и третьего триггеров, один выход каждого Hs которых соединен со входом сброса счетного триггера и выходом второго элемента НЕ, а вторые вхо.ды второго и третьего триггеров подключены к выходам счетного триггера 2).

Недостатком этого дискриминатора является малое количество измеряемых фазовых сдвигов.

Цель изобретения — увеличение исла измеряемых фазовых сдвигов сигналов.

809485

Поставленная цель достигается тем, что в цифровой фазовый дискриминатор, содержащий два формирователя, первые входы которых соединены со входными шинами, а выходы подключены к первым входам двух вентилей, выход первого из которых соединен с одним входом первого триггера, второй вход которого соединен через первый элемент ИЛИ с выходом второго вентиля, а выход которого через третий вентиль, второй вход которого подключен к первому выходу генератора эталонных импульсов, соединен с одним входом счетчика, второй вход которого соединен с входом регистра памяти и шиной тактовых импульсов, а выходы разря- 15 дов счетчика соединены со входами регистра памяти, вход управления которого подключен к первому входу регистра сдвига, выходу первого элемента И и через первый элемент HE gp первому входу второго элемента И, второй вход которого соединен с одной из входных шин, со вторым входом регистра сдвига, вторым входом первого элемента ИЛИ, первым входом второго элемента HJiH, а выход второго логического элемента И подключен к первому входу выходного элемента ИЛИ, второй вход которого соединен с выходом регистра сдвига, причем входы первого элемента И соединены с выходами второго и третьего триггеров, один вход каждого из которых соединен со входом сброса счетного триггера и выходом второго элемента НЕ, а вторые входы второго и третьего триггеров подключены к выходам счетного триггера, введены два триггера, три вентиля, два элемента ИЛИ, шесть элементов И, счетчик и регистр памяти, первый вход которого соединен с шиной 4(j тактовых импульсов, второй вход соединен с выходом первого элемента И, входы разряд в подключены к выходам разрядов второго счетчика, один вход которого через четвертый вентиль сое- 45 динен с выходом четвертого триггера, один вход которого соединен с выходом второго элемента ИЛИ, а второй вход соединен со входом третьего элемента ИЛИ и выходом пятого вентиля, один вход которого соединен с первым входом шестого вентиля, первым входом пятого триггера и первыми входами третьего, четвертого и пятого элементов И, второй вход которого соединен с выходом первого регистра памяти, а выход подключен к третьему входу второго элемента И, четвертый вход которого соединен с выходом шестого элемента И, первый вход которого соединен с первыми Щ входами седьмого и восьмого элементов Н, вторым выходом пятого триггера и вторыми входами первого и второго вентилей, причем счетный вход пятого триггера соединен с входной Я шиной, а его сбросовый вход подключен к шине тактовых импульсов и второму входу второго счетчика, выход которого подключен к второму входу седьмого элемента И, а третий вход второго счетчика соединен с выходом восьмого элемента И, второй вход которого подключен к второму входу третьего элемента И, входу второго элемента НЕ и выходу третьего элемента ИЛИ, второй вход которого соединен с выходом первого вентиля, счетный вход счетного триггера соединен с выходом четвертого элемента ИЛИ, один вход которого соединен с выходом второго вентиля, а второй вход с вторым входом второго элемента ИЛИ с выходом шестого вентиля, второй вход которого подключен к выходу второго формирователя, при этом второй вход четвертого вентиля соединен со вторым выходом генератора эталонных иглпульсов, второй вход шестого элемента И соединен с выходом второго регистра памяти, выход седьмого элемента И соединен с третьим входом регистра сдвига, четвертый вход которого через четвертый элемент И соединен с выходом первого счетчика, а второй вход пятого вентиля соединен с выходом первого формирователя.

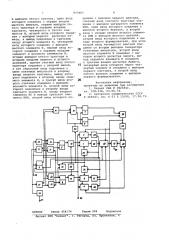

На чертеже изображена структурная электрическая схема дискриминатора.

Дискриминатор содержит счетчики

1 и 2, регистры памяти 3 и 4, триггеры 5-9, счетный триггер 10, элементы ИЛИ 11-14, выходной элемент

ИЛИ 15, вентили 16-21, регистр сдвига 22, элементы НЕ 23 и 24, элеменT6I И 25-32, формирователи 33 и 34, генератор 35 эталонных импульсов, шины 36 и 37, шин 38 тактовых импульсов. Выходной сигнал снимается с выхода 39.

Цифровой дискриминатор работает следующим образом.

Тактовый импульс соответствующий началу интервала считывания поступает на входы счетчиков 1 и. 2, регистров 3 и 4 памяти и триггер 9, устанавливая их в исходное состояние.

Сигналы опорных импульсов поступают на входы элементов ИЛИ 11 и 12, устанавливая триггеры 5 и 8 в исходное состояние, на счетный вход триггера 9, устанавливая его в единичное состояние, устанавливая разрешающие потенциалы на вентиле 16, на вентиле 17 и на элементах И 30-32.

Сигналы с измеряемой 9 и опорной фазами преобразуется в формирователя 33 и 34 соответственно в, импульсы стандартной формы и через вентиль 16 и вентиль 17 поступают на триггер 5, формирующий мерный интервал, пропорциональный фазовому

809485 сдвигу между опорным и измеряемым сигналами.

Этот интервал заполняется эталонными импульсами через вентиль

18 в счетчике 1 от генратора 35 эталонных импульсов.

С приходом сигнала на вход вентиля 17, триггер 5 через элемент

ИЛИ 11 устанавливается в состояние

"0" заканчивая формирование мерного интервала . Одновременно первый импульс P c выхода вентиля 17 через элемент ИЛИ 14, поступая на счетный вход триггера 10 ставит его в состояние "1". При этом импульс. переноса с нулевого плеча устанавливает триггер 6 в состояние "1". 35

Второй импульс 9с по счетному входу переключает триггер 10 в состояние

"0", при этом импульс переноса с единичного плеча устанавливает в состояние "1" триггер 7. 20

Появление последующих импульсов поочередно переключает триггер 10, формируя на его выходах импульсы переноса, которые подтверждают состояние триггеров 6 и 7. 25

Таким образом, к моменту появления опорного импульса, последующего прилегающего фазового сдвига, триггеры 6 и 7 будут находиться в состоянии "1", что говорит об имевшем место появлении нескольких импульсов.

В результате на выходе элемента

И 25 сформируется уровень "0", запрещающий съем информации из счетчика

1 через регистр 22 и разрешающий через элемент HE 23 съем информации предыдущего замера в соответствующем интервале корреляции и соответствующем такте считывания из регистра 3 через элемент И 26. 40

Опорный импульс последующего прилегающего фазового сдвига устанавливает триггер 9 в нулевое состояние, устанавливая запрещающие потенциалы на вентили 16 и 17 и элементы И 30-32 4 и разрешающие — на вентили 20 и 21 и элементы И 27-29.

Сигналы с измеряемой Р и опорной

Ч в фазами поступают на триггер 8, формирующий первый интервал, пропорциональный фазовому сдвигу между опорным и измеряемым сигналами.

Этот интервал заполняется эталонными импульсами через вентиль 19 в счетчике 2 от генератора 35 эталонных импульсов.

Одновременно сигналы Р0 поступают на входы регистра 22 и элемента И 26 на считывание информации, которая снимается с выхода элемента ИЛИ 15, одновременно по сигналам с выхода 40 элемента ИЛИ 13 через элемент И 27 йроизводится запись результата замера из счетчика 1 в регистр 3 (в случае отсутствия сигнала помехи). и сдвиг регистра, устанавливая состояние соответствующего предыдущего замера соответствующего последующего интервала корреляции, и через элемент НЕ 24 по переднему фронту паузы сброс в нулевое состояние триггеров 6, 7 и 10.

Аналогичным образом происходят измерении последующих фазовых сдвигов прилегающих каналов лежащих на одном интервале корреляции.

Формула изобретения

Цифровой фазовый дискриминатор, содержащий два формирователя, первые входы которых соединены со входными шинами, а выходй подключены к первым входам двух вентилей, выход первого из которых соединен с одним входом первого триггера, второй вход которого соединен через первый элемент ИЛИ с выходом второго вентиля, а выход через третий вентиль, второй вход которого подключен к первбму выходу генератора эталонных импульсов, соединен с одним входом счетчика, второй вход которого соединен, с входом регистра памяти и шиной тактовых импульсов, а выходы разрядов счетчика соединены со входами регистра памяти, вход управления которого подключен к первому входу регистра сдвига, выходу первого элемента И и через первый элемент HE к первому входу второго элемента И, второй вход которого соединен с одной из входных шин, со вторым входом регистра сдвига, вторым входом первого элемента ИЛИ, первым входом второго элемента ИЛИ, а выход второго. логического элемента И подключен к первому входу выходного элемента ИЛИ, второй вход которого соединен с выходом регистра сдвига, причем входы первого элемента И соединены с выходами второго и третьего триггеров, один вход каждого из которых соеди-. нен со входом сброса счетного триггера и выходом второго элемента НЕ, а вторые входы второго и третьего триггеров подключены к выходам счетного триггера, о т л и ч а ю щ и йс я тем, что, с целью увеличения числа измеряемых фазовых сдвигов, в него введены два триггера, три вентиля, два элемента ИЛИ, шесть элементов И, счетчик и регистр памяти, первый вход которого соединен с шиной тактовых импульсов, второй вход соединен с выходом первого элемента И, входы разрядов подключены к выходам разрядов второго счетчика, один вход которого через четвертый вентиль соединен с выходом четвертого триггера, один вход которого соединен с выходом второго элемента ИЛИ, а второй вход соединен со входом третьего элемент" ИЛИ

809485 аНИИПИ Эаказ 454/74

Тираж 999 Подписное филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 и выходом пятого вентиля, один вход которого соединен с первым входом шестого вентиля, первым выходом пятого триггера и первыми входами третьего, четвертого и пятого элементов И, второй вход которого соединен с выходом первого регистра памяти, а выход подключен к третьему входу второго элемента И, четвертый вход которого соединен с выходом шестого элемента И, первый вход которого соединен с первыми входами седьмого и восьмого элементов И, вторым выходом пятого триггера и вторыми входами первого и второго вентилей, причем счетный вход пятого триггера соединен с входной шиной, а его сбросовый вход подключен к шине тактовых импульсов и второму входу второго счетчика, выход которого подключен к второму входу седьмого элемента И, а третий вход второго счетчика соединен с выходом восьмого -элемента И, второй вход которого.подключен к второму входу третьего элемента И, входу второго элемента НЕ и выходу третьего элемента ИЛИ, второй вход которого соединен с выходом первого вентиля, счетный вход счетного триггера соединен с выходом четвертого элемента

ИЛИ, один вход которого соединен с выходом второго вертиля, а второй

5 вход с вторым входом второго элемента ИЛИ и выходом шестого вентиля, второй вход которого подключен к выходу второго формирователя, при этом второй вход четвертого вентиля соединен со вторым выходом генератора эталонных импульсов, второй вход шестого элемента И соединен с выходом второго регистра памяти, выход седьмого элемента И соединен с третьим входом регистра сдвига, четвертый вход которого через четвертый элемент И соединен с выходом первого счетчика, а второй вход пятого вентиля соединен с выходом первого формирователя.

Источники информации, принятые во. внимание при экспертизе

1. Патент США Р 3825842, кл. 328-138, 23.06.74.

75 2. Р.вторское свидетельство СССР

9 465647, кл. Н 03 0 13/00, 17.04.73.