Умножитель частоты следования импульсов

Иллюстрации

Показать всеРеферат

Союз Советскнх

Соцналнстнческнх

Республнк

ОП ИСАНИ Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

<(((809526 (5l)M. Кл. (61) Дополнительное к авт. свид-ву

Я2)Заявлено 17.04.79 (2l) 2753211/18-21 с присоединением заявки М

НО3К 5/01

Государствеиный комитат

СССР (23) Приоритет ио делам иэобретеиий и открытий

Опубликовано 28.02.81. Бюллетень .% 8

Дата опубликования описания 28.02.81 (53) УД К 62 1.374. (О 88.8) (72) Авторы изобретения

В. Н. Попов, В. A. Лазарев, Н. П. Сергеев и Г. B. Галкин

Пензенский политехнический институт (4„ ! ! (71) Заявитель (54) УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ

HM ПУЛЬСОВ

Изобретение относится к автоматике, измерительной и вычислительной технике и может найти применение в устройствах частотно-импульсной и цифровой обработки инфо р маци и.

Извес тно ус тройс тво цля умножения частоты следования импульсов, содержащее источник калиброванной частоты, источник входной частоты, цва управляемых дели теля частоты, из мери тель периода, то четыре блока сдвига. Управляемые дели- . тели частоты соцержат по два вычитающих счетчика, цва регистра памяти, два вентиля переноса, четыре элемента задержки и по два вентиля. Измеритель перио15 ца соцержит суммирующий счетчик, вентиль переноса кода, цва элемента задержки. В блоки сдвига вхоцят по четыре элемента И, цва элемента запрета, цва элемента ИЛИ P) °

Нецостатками этого устройства являются. значительные аппаратурные затраты и сложность алгоритма работы, что ограничивает область ого применения.

Известен также умножитель частоты слецования импульсов, соцержаций дели— тель опорной частоты с коэффициентом деления, равным коэффициенту умножения, счетчик импульсов опорной частоты, входной и выходной формирователи, запоминающий регистр и блок управления (2).

Недостатком этого умножителя является динамическая погрешность ограничиваю( щая область его применения.

Наиболее близким по технической сущности к предлагаемому является умножитель частоты, соцержащий делитель опорной частоты, входной формирователь, регистры сдвига, блоки переноса коца, запоминающий регистр, блок управления и выходной формирователь (31.

Недостатком этого устройства является низкая надежность работы. Так, появление ложной единицы в одном из рпзря— цов регистра сдвига полностью нарушает его работу. Циркуляция ложной оципиць( может продолжаться неограниченно (юлг(1, Вызывая пульс ацию ч Вс то ты H а вь(хо(и . умножителя. Причем начальный сброс регистра сдвига не восстанавливает работоспособность устройства.

Gemü изобретения — повышение надежностии работы умножителя.

Поставленная цель достигается тем, что в умножителе частоты следования импульсов, содержащем входной и выходной формирователи, делитель опорной частоты, запоминающий регистр, два регистра сдвига, блок управления, первый выход которого соединен с синхронизирующим входом запоминающего регистра, блок переноса кода, входы которого подключены к информационным выходам запоминающего регистра, а выходы соединены с установочными входами первого регистра сдвига, выход которого соединен со вхоцом выходного формирователя импульсов, установочный вход старшего разряда — со вторым выходом блока управления, а управляющий вхоц — с шиной опорной часто— ты и через целитель опорной частоты — с управляющим входом второго регистра . сдвига, информационный вход которого сое динен с выходом входного формирователя импульсов, а выход-с первым входом блока управления, второй вход блока управления соединен с выходом выходного формирователя импульсов, третий и четвертый выходы которого подключены соответственно к управляющему входу блока переноса кода и к шине сброса первого регистра сцви га, а информационные выходы второго .ре— гистра сдвига соединены с информационными входами запоминающего регистра.

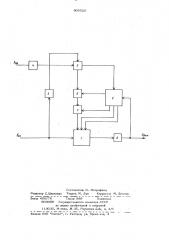

На чертеже изображена структурная электрическая схема умножителя частоты следования импульсов.

Умножитель содержит первый регистр

1 сдвига, делитель 2 опорной частоты, второй регистр 3 сдвига, входной формиро ватель 4 импульсов, блок 5 управления, запоминающий регистр 6, блок 7 переноса кода, выходной формирователь 8 импуль— сов.

К шине опорной частоты подключены управляющий вход первого регистра 1 сдвига и через делитель 2 опорной частоты — управляющий вход второго регистра 3 сдвига, информационный вход которого соединен с выходом входного формирователя 4, а выход старшего разряда ре гистра 3 сдвига подключен к первому входу блока 5 управления, информационные выходы регистра 3 сдвига соединены с информационными входами запоминающего регистра 6, информационные выходы которого подключены к блоку 7 переноса ко50

55 формирователь 8, Импульс с выхода формирователя 8 поступает в блок 5 управления. При этом блок 5 управления каждый раз формирует два следующих .друг за другом импульса, первый из которых поступает на шину сброса регистра 1 сцвига, а второй, сцви— нутый относительно первого на время, равное максимальному времени переходда. Выходы блока 7 соединены с установочными входами первого регистра 1 сдвига, выход старшего разряда которого соединен с входом выходного формирователя

8, выход которого подключен к второму входу блока 5 управления, четыре выхода кото— рого подключены соответственно к синхронизируюшему входу запоминающего регистра 6, к установочному входу старше—

10 го разряца первого регистра 1 сцвига, к управляющему вхоцу блока 7 переноса и к шине сброса регистра 1 сцвига.

Устройство работает следующим образомм.

15 Импульсы опорной частоты поступают на вхоц делителя 2, коэффициент деления которого равен эацанному коэффициенту умножения, и на управляющий вход регистра 1 сдвига. Импульсы с выхода дели- теля 2, частота следования которых равна fo К, подаются на управляющий вход регистра 3 сдвига. Каждый импульс ум— ножаемой частоты поступает через входной формирователь 4 на рабочий вход регистра 3 сдвига, записывается в первом разряде этого регистра (разряд из состояния О перевоцится в состояние 1) и последовательно переносится в послецующие со скоростью, соответствующей частоте следования тактирующих импуль —: сов. Число разрядов N регистра 3 сдвига, находящееся между цвумя возбужценными разряцами, пропорционально периоду вхоц— ного сигнала Т „и равно 1/к.Т /Т п, Таким образом, в регистре 3 сцвига

35 фиксируется каждый период Тр,у вхоцного сигнала. Импульсы с последнего разряда регистра 3 сдвига поступают на вход блока 5 управления.

Блок 5 управления формирует сигналы, 40 поступающие на синхронизируюшие вхоцы запоминающего регистра и на установочный вход послецнего разряда регистра 1 сдвига, при этом соцержимое регистра 3 сдвига переносится в запоминающий регистр, а последний разряд регистра 1 сдвига переводится в единичное состояние.

Сигнал, снимаемый с послецнего раз— ряца регистра 1 сцвига, поступает на

809 526 ного процесса в регистре 1 сдвига, пере носит содержимое запоминающего регистра. 6 через блок 7 переноса кода в регистр 1 сдвига.

Таким образом, код из запоминающего регистра 6 переносится, в регистр 1 сдвига по каждому выхоцному импульсу формирователя 8.

Частота следования этих импульсов равна

1О

Формула изобретения

Умножитель частоты следования импульсов, содержащий входной и выходной формирователи, .целитель опорной частоты, запоминающий регистр, цва регистра сдвига, блок управления, первый выход которого соединен с синхронизирующим входом запоминающего регистра, блок переноса, . 30 кода, входы которого подключены к информационным выходам запоминающего регисОбнуление регистра сдвига после каждого выходного импульса исключает влияние ложных ециниц, возникающих в какомлибо из разрядов регистра сдвига, на работу устройства и, слецовательно, приводит к повышению надежности работы устро йс тв а.

20 тра, а выходы соединены с установочными входами первого регистра сдвига, выход которого соединен со входом выходного формирователя импульсов, установочный вход старшего разряда- со вторым выходом блока управления, а управляющий вход-с шиной опорной частоты и через целитель опорной частоты — с управляющим входом второго регистра сдвига, информационный вход которого соединен с выходом входного формирователя импульсов, а выход — с первым входом блока управления, о т л и— ч а ю шийся тем, что, с целью повь шения надежности работы умножителя, второй вход блока управления соединен с выхоцом выхоцного формирователя импульсов, третий и четвертый выходы которого подключены соответственно к управляющему входу блока переноса кода и к шине сброса первого регистра сцвига, а информационные выходы второго регистра сдвига соединены с информационными вхоцами запоминающего регистра.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

М 517163, кл. НОЗК 23/00, 1974.

2. Авторское свидетельство СССР

N.o 357668, кл. НО3К 5 01, 1971.

3. Авторское свидетельство СССР

N 627572, кл. НО3К 5/01, 1975.

809526

Составитель О. Митрофанов

Редактор C.Øåâ÷åíêo Техред М. Лоя- Корректор М. Демчик

Заказ 456/76 Тираж 999 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Mrсква, Ж-35, Раушская йаб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проек ги«я, 4