Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических республик

К АВТОРСКОМУ СВ ЕТИЗЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 16.04. 79 (21) 2751679/18-21 51)м Кл с присоединением заявки Йо (23) Н 03 К 13/17

Государственнмй комитет

СССР по делам нэобретений и открытнй

Приоритет

Опубликовано 280281. бюллетень Н9 8 (53) УДК 681. 325 (088. 8) Дата опубликсвания описания 28. 02. 81 (72) Авторы изобретения

О.Г. Сморыго и В.Я. Стенин

Московский ордена Трудового Красного Эн ни инженерно-физический институт

ы (71) Заявитель (54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЭОВАТЕЛЬ

Изобретение относится к устройствам импульсной техники и предназначено для использования в цифровых измерительных приборах, устройствах автоматического управления, в системах сбора и обработки данных.

Известны- быстродействуххцие аналого-цифровые преобразователи,построен- © ные по методу непосредственного считывания и содержащие резистивный де« литель из 2" резисторов с одинаковым сопротивлением (n — число двоичных разрядов), служащий для создания

2"-1 эталонных напряжений, которые подаются на входы 2"-1 схем сравнения, на вторые входы которых задается входной сигнал, выходы схем сравг нения соединены с 2"-1 входами шифратора, с выходов которого снимается параллельный двоичный код, соответствующий входному сигналу L1).

Недостатком этих преобразователей, проявляющемся при повышении их точности (т.е. с ростом числа двоичных разрядов n),ÿâëÿåòñÿ степенное возрастание (примернд как 2") потребляемой мощности и размеров устройства, связанных со степенным ростом числа схем сравнения, резисторов делителя ЗО эталонного напряжения и элементов шифратора.

Известен аналого-цифровой преобразователь, содержащий источник входного сигнала, источник эталонного напряжения, линию задержки с и-1 выходами, где и — количество разрядов преобразователя, и-1 сдвиговых регистров, и элементов сравне-о ния, к первому входу элемента сравнения старшего разряда которого подключен выход источника входного сигнала, ко второму входу — источник эталонного напряжения, выходы элементов сравнения, кроме младшего разряда, соединены со входами и-1 сдвиговых регистров (2).

Недостатком преобразователя является ограниченная точность.

Цель изобретения — повышение точности аналого-цифрового преобразователя °

Поставленная цель достигается тем, что аналого-цифровой преобразователь, содержащий источник входного сигнала, источник эталонного напряжения, линию задержки с п-1 выходами, где и — количество разрядов преобразователя, и-1 сдвиговых регистров, и элементов сравнения, 809555 к первому входу элемента сравнения старшего разряда которого подключен выход источника входного сигнала, ко второму входу — источник эталонного .напряжения, выходы элементов сравнения, кроме младшего разряда, соединены со входами и-1 сдвиговых регистров, введены резистивная матрица R-2R на и-1 разряд, и двухнходовых устройств коммутации, и-1 двухвыходовых устройств коммутации, и-1 устройств аналогового хранения, а линия задержки содержит и-1 дополнительных входов, причем к первому входу первого двухвхо дового устройства коммутации подклю-. чен источник azодного сигнала, ко. второму входу — источник эталонного напряжения, к ныходу - первый вход линии задержки, и-1 выходов которой соединены со входами и-1 двухвыходовых устройств коммутации, у каждого из которых первый выход через соответствующее устройство аналогового хранения, а второй выход — непосредственно соединены со входами соответствующего элемента сравнения данного разряда, выходы элементов сравнения, кроме элемента сравнения младшего разряда,.соединены с первыми входами соответствующих им днухвходоных устройств коммутации, выходы которых соединены с и-1 входами линии задержки, Источник эталонного напряжения подключен ко входу резистивной матрицы R-2R, и-1 выходы которой соединены со вторыми входамй и-1 двухнходоных устройств коммутации.

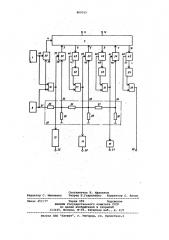

На чертеже изображена блок-схема анааого-цифрового преобразователя на четыре двоичных разряда.

Преобразователь содержит источник

1 входного сигнала,,источник 2 эталонного напряжения, линию 3 задержки, имеющую входы 4-7, выходы 8-10 и выводы для подключения двух фаз 11 и 12 импульснбго питания,.сднигоawe регистры 13-15, элементы 16-19 сравнения, резистивную матрицу 20, имеющую вход 21, выходы 22-24 и содержащую резисторы 25-30, двухвходоные устройства 31-34 коммутации со входами 35-42, днухвыходовые уст» ройатна 43-45 коммутации с выхо-.д 46-51, устройства 52-54 аналого oro хранения. Выходом преобразо.ва являются выходы 55"57 сдвиговых регистров 13-15 и выход 58 элемента 19 сравнения. В качестве линий задержки используется устройство, выполненное на приборах с saрядовой связью с двухфазным импульсным питанием и иеразрушающим считыванием передаваемых сигналов на боковых выходах.

Аналого-цифровой преобразователь работает следующим образом.

На вход 35 устройства 31 коммутации подается входной аналоговый сигнал U@ от источника 1 входного сигнала, йа вход 21 подается от источника 2 эталонного напряжения эталонное напряжение Еат, равное поло- . вине максимального входного сигнала

«1 = Еэт = 0Ъх п/2 ° При этом на выходе 22 напряжение 0>> = Е >„ /2, на выходе 23 напряжение 0 з Езт/4, на выходе 24 — 0 4 = Езт/8. От источника. 1 входного сигнала и источ® ника 2 эталонного напряжения выборка входного сигнала 0 „1 и эталонный сигнал Ед поочередно вводятся в линию 3 задержки по входу 4 с помощью двухнходового устройства 31 коммутации, образуя набор из двум анало15 говых сигналов Ug (t=0) =.Ub„„=U 6„, t 0) и 0;, (t = T) =E», где t=0 определяет начало отсчета времени с момента ввода выборки входного сигнала 0.Ь„; Т— период ввода сигнала н линию 3 задерж2О ки.

Затем н линию 3 задержки по входу

4 вводится следующий набор из двух сигналов: следующей ныборки входного ,сигнала 0 „, „=ОbÄ (t=2T) и эталонного

25 сигнала Е, т.е. 0;+, q (t=2T) =

=0.6х,;+ =0 ах (t=2T) H Ugyg ä (й=ЗТ) =Е т.

Так в линии 3 задержки формируется и перемещается набор из двух сигналов — выборки входного сигнала и эталонного сигнала. Процесс преобразования выборки входного сигнала в двоичный код рассмотрим на примере выборки входного сигнала

Ug„(t=0) U@„;. Одновременно с вводом этой выборки входного сигнала н линию 3 задержки по входу 4 н момент времени t=0, эта выборка сравнивается со значением эталонного сигнала ,Е элементом 16 сравнения. Результатом сравнения,является логический

40 сигнал на его выходе равный а„=0 или а =1, являющийся значением старшега разряда кода преобразуемой выборки нходного аналогового сигнала Ub

Логический сигнал а< поступает на вход регистра сдвига 13, выполняющего роль динамической йамяти, и одновременно на вход 37 двухвходового устройства 32 коммутации. Значение логического сигнала а на вы4 ходе элемента 16 сравнения управляет днухвходовым устройством 32 коммутации по входу 37 и обеспечивает добавление сигнала 0 Ет /2 с выхода резистивной,матрицы 20 через двухвходовое устройство 32 коммутации к меньшему из двух в наборе сигналон Ug q (t=0) =Ua и 03@ (й=Т) = Е т, перемещающихся в линии 3 задержки, например, если в результате сравнения U =0@„(t=0) Е т, то после

49 .выборки логического сигнала на вы;ходе элемента 16 сравнения а =1 бу-.

Дет осУЩествлЯтьсЯ Добавка 0 1=Е зт/2 к меньшему в наборе из двух сйгналов, т.е. будет 0 „ (t=2T)=0)q (t=T)=0ьк;, 65 а Цй (t"2T) =E»+Eýò /2. Далее, при

809555 ю

20 переносе набора из двух сравниваемых сигналов по линии З.задержки первый из них в момент времени t 2T

U;q (t2Т)=Vexed считывается неразрущающим способом с линии 3 задержки и поступает на двухвыходовое уст- ройство 43 коммутации и на устройство 52 аналогового хранения, которым и запоминается. С выхода устройства 52 аналогового хранения этот сигнал поступает на один из входов элемента 17 сравнения в момент вре(мени t=3T. В следующий такт переноса сигналов по линии 3 задержки, т.е. при ЗТ, второй из сигналов в рассматриваемом наборе Щ g (t=3T) Ui2 (=2Т)=Езт+Е т/2 считывается неразрушающим способом с выхода 8 и с выхода 46 устройства 43 коммутации и поступает на второй вход элемента 17 сравнения. В результате сравнения сигналов из рассматриваемого набора Ug< (t=2T)=04,xi и

Uq q { е=ЗТ) =E»+E эт/2 элемент 17 сравнения вырабатывает значение второго разряда двоичного кода а пре1 образуемой выборки 0.ь»; аналогового сигнала. Пусть 0 ; (Е + Ез /2, тогда а =О. Логический сигнал а =0

2 с выхода элемента 17 сравнения поступает на вход сдвигового регистра 14, имеющего на один разряд меньше, чем сдвиговый регистр 13, в котором хранится значение а . Одновременно сигнал с выхеда элемента 17 сравнения по входу 39 управляет двухвходовым устройством 33 коммутации которое осуществляет добавку уравновешиваю» щего сигнала 0 =Еэ /4 к меньшему из сигналов в перемешающемся в линии

3 задержки наборе из двух сигналов

0 э и Uig. В рассматриваемом примере

Щ (t 2T) < 0 (t=3T) и добавка

Uq Езт /4 осуществляется к первому сигналу в наборе, т.е.

044(Ф ЗТ} НИ(Ф Ят)Ф Еэт/4 .ЦВ„,+ЕЛ/4

Vip(t = 4Т)Ugg(t ЗГ) Å sT+ Е у!2.

Аналогично происходит процесс формирования более младших разрядов двои його кода аналогового сигнала

0 ; сопровождающийся уравновешиванием двух сигналов в наборе 0 4 и

Оп, перемещающихся в линии 3 задержки. Процесс преобразования завершается выработкой на выходе 58 элемекта 19 сравнения значения младщего разряда кода.а„, синхронно с выработкой которого на выходах 55-57 сдвиговых регистров появляются значения остальных разрядов кода а, а в ° ° ° э °

Одновременно в аналого-цифровом преобразователе происходит уравяо6 вешивание и (для рассматриваемого примера п4) выборок входного сигнала U ; где i = 1,2,3....

На выходах 55-58 через промежутки времени с2Т. появляются значения параллельного двоичного кода преобразуемых выборок входного сигнала.

Формула изобретения.

Аналого-цифровой преобразователь, содержащий источник входного сигнала, источник эталонного напряжения, линию задержки с а-1 выходами, где и — ко" личество разрядов преобразователя, и-1 сдвиговых регистров, и элементов сравнения, к первому входу элемента сравнения старшего разряда которого подключен выход источника входного сигнала, ко второму входу - источник эталонного напряжения, вы3соды элементов сравнения, кроме младшего раз- ряда, соединены со входами п-1 сдви,говых регистров, о т л и ч а ю щ и й«. с я тем, что, с целью повышения точности, в него введены резистивная матрица R-2R íà и-1 разряд, и двухвходовых устройств коммутации, и-1 двухвыхадовых устройств коммутации, и-1 устройств аналогового хранения, а линия задержки содержит и-1 дополнительных входов, причем к первому входу первого двухвходового устройства коммутации подключен источник входного сигнала, ко второму входу - источник эталонного напряжения, к выходу — первый вход линии задержки, и-1 выходов которой соединены с входами и-1 двухвыходовых устройств коммутации, у каждого из которых первый выход через соответствующее устройство аналогового хранения, а второй выход - непосредственно соединены со входами соответствующего элемента сравнения данного раэряда, выходы элементов сравнения, кроме элемента сравнения. младшего разряда, соединены с первыми входами соответствующих им двухвходовых устройств коммутации, выходы которых. соединены с п-1 входами линии задержки,.источник эталонного напряжения подключен ко входу резистивной матрицы R-2R, п-1 выходы которой соединены со вторыми входами и-1 двухвходовых устройств -коммутации.

° уу

Источники информации, принятые во внимание при экспертизе

1. Балакай B.Ã. и др. Интеграль- . ные схемы MQI и ЦАП. "Энергия", 1978, с. 55. ф 2."Electronic Design, 1969, Р 1, с. 101-102 (прототип).

Составитель В. Махнанов

Редактор С. Шевченко Техред Е.Гаврилешко Корректор О. Билак

Заказ 457/77 Тираж 999 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная,4