Формирователь тактовых сигналов

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДВТИЛЬСТВУ (63) Дополнительное к авт. сеид-ау— (22) Заявлено 1604.79 {2!) 2755276/18-21 (11809569. (51)м. Кл.

Н 03 К 17/04 с присоединением заявки М

ГосударствеииыА комитет

СССР оо @мам изобретениЯ и открытиЯ (23) Приоритет—

Опубликовано 280281. Бюллетень 89 8

Дата опубликования описания 280281 (53) УДК 621. 373. 4 (088.8) -"СЬ;.(;,„: 14 ц:. . г Ц гт- - .

Мад4 y рог, 4.т.а 0 ь ных (72) Авторы изобретения

H. И. Величко, В. В. Кулаков и В. Г. Рябцев.

Научно-исследовательский институт управляющих машин (71) Заявитель (54) ФОРМИРОВАТЕЛЬ ТАКТОВЫХ СИГНАЛОВ

Изобретение относится к вычислительной технике и может быть использовано для формирования тактовых сиг= налов полупроводникового запоминающего устройства, построенного на больших интегральных схемах, изготовленных по и-канальной МОП-технологии.

Известна схема составного эмиттерного повторителя, включающая в себя два транзистора п-р-п и р-п-р типов, обеспечивающая передачу положитель ного и отрицательного Фронтов входного сигнала без искажений f1j .

Известен также возбудитель для работы на емкостную Нагрузку, в качестве которой может быть запоминающее устройство, содержащий заряжающий транзистор, включенный между на-. грузкой и зажимом питания, делитель напряжения на резисторах, подключенный к зажиму питания и управляющему электроду транзистора, конденсатор, подключенный между емкостной нагрузкой и средней точкой делителя напряжения, выпрямитель, ключ и резистор, обеспечивающий критическое затухание в цепи нагрузки 121 . Недостатком известных устройств является высокий уровень логического нуля (до 1,0 В) выходного сигнала, снижающий помехоустойчивость полупроводникового запоминающего устройства.

Цель изобретения — повьажние помехоустойчивости.

Поставленная цель достигается тем, что в формирователь тактовых сигналов, содержащий первый ключ, заряжающий п-р-rr транзистор, разряжающий р-п-р транзистор, змиттеры которых через резисторы соединены с выходным зажимом, коллектор первого транзисто-, ра соединен с шиной питания, .а коллектор второго транзистора — с общей ши15 ной, база первого транзистора соединена с выходом первого ключа и через резистор с шиной питания, введены второй ключ и резистор, причем резистор подключен между базой р-и-р транзистора и выходным зажимом, выход второго ключа соединен с базой р-и-р транзистора, а вход второго «люча соединен со входом первого клвжа.

Кроме того, в формирователь введен третий р-п-р трэнэистор, эмиттер tco торого подключен к шине литания, а .база и коллектор подключены соответственно к коллектору и эмиттеру и-р-и

ЗО транзистора.

809569

Благодаря введению новых элементов, основной ток заряда емкости нагрузки протекает через дополнительный р-п-р транзистор, при этом уменьшается прямое падение напряжения перехода база-, эмиттер п-р-п транзистора, что приводит к увеличению высокого уровня напряжения выходного сигнала.

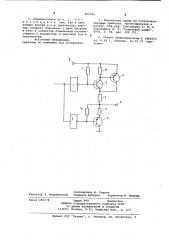

На чертеже приведена принципиаль ная электрическая схема предлагаемого устройства.

Устройство содержит первый ключ 1, заряжающий п-р-п транзистор 2, разряжающий р-п-р транзистор 3, эмиттеры которых через резисторы 4 и 5 соединены с выходным зажимом 6, база тран- 1 эистора 2 соединена с выходом первого ключа и через резистор 7 — с шиной питания 8, второй ключ 9, выход которого соединен с базой р-и-р транзистора 3 и через резистор 10 — с 20 выходным зажимом, коллектор транзистора 3 подключен к общей шине, а коллектор транзистора 2 соединен с базой дополнительного транзистора 11 и через резистор 12 — с шиной питания, э5 к которой подключен эмиттер дополнительного транзистора 11, коллектор которого соединен с эмиттером заряжающего и-р-и транзистора 2.

Устройство без транзистора 11 работает следующим образом.

В исходном состоянии на входы ключей 1 и 9 поступает сигнал напряжения высокого уровня, при этом на 6азу транзистора 2 подается запирающий потенциал, а на выходном зажиме 6 напряжение равно напряжению насыщенного ключа 9.

При подаче на входы ключей 1 и 9 импульса напряжения низкого уровня на их выходах возникает напряжение 40 высокого уровня, открывается транзистор 2 и через резистор 5 прстекает ток заряда емкости нагрузки, транзистор 3 при этом закрыт. Когда напряжение на входах ключей 1 и 9 становится 4 равнык высокому уровню, транзистор 2 закрывается, а транзистор 3 открывается, при этом основной ток разряда емкости нагрузки протекает через резистор 4 и транзистор 3. Когда напря- щ жение на емкости нагрузки равно 1,0 В, транзистор 3 закрывается и окончательный разряд емкости происходит через резистор 10 и открытый ключ 9, при этом величина резистора может быть выбрана небольшой, так как основной ток разряда емкости нагрузки протекает через него только при снижении напряжения нагрузки до 1,0 B.

Величина низкого напряжения тактового сигнала устанавливается равной 40 напряжению насыщения транзистора, ключа 9 и не превышает 0,4 В.

Устройство с дополнительным транзистором 11 работает следующим образом. 6S

В исходном состоянии на вход ключей 1 и 9 поступает сигнал напряжения высокого уровня, при этом на базу транзистора 2 подается запирающий потенциал, а на выходном зажиме 6 напряжение равно напряжению насыщения ключа 9. Падение напряжения на резисторе 10 можно не учитывать ввиду емкостного характера нагрузки.

При подаче на вход ключей 1 и 9 импульса напряжения низкого уровня открываются транзисторы 2 и. 11 и через резистор 5 протекает ток заряда емкости нагрузки, транзистор 3 и ключ

9 при этом закрыты.

Напряжение на зажиме 6 выше, чем в устройстве без транзистора 11 и резистора 12, так. как включение дополнительного транзистора приводит к увеличению суммарного коэФФициента усиления по току каскада и .уменьшению падения напряжения на резисторе 7 за счет уменьшения базового тока транзистора 2.

Когда напряжение на. входе ключей

1 и 9 снова равно высокому уровню, транзисторы 2 и 11 закрываются, а транзистор 3 открывается, при этом основной ток разряда емкости нагрузки протекает через резистор 4 и транзистор 3. Когда напряжение на емкости нагрузки становится равным 1,0 В, транзистор 3 закрывается и дальше разряд происходит через резистор 10 и открытый ключ 9, в результате потенциал на выходном зажиме 6 устанавливается равным падению напряжения на насыщенном транзисторе ключа 9.

В предлагаемом устройстве по сравнению с известными, уменьшается низкий уровень напряжения с 1,0 В до

0,4 В, что повышает помехоустойчивость полупроводникового запоминаю его устройства и увеличивает надежность ра бо гы.

Формула изобретения

1. Формирователь тактовых сигналов, содержащий первый ключ, заряжающий и-р-и транзистор, разряжающий р-п-р транзистор, эмиттеры которых через резисторы соединены с выходным зажимом, коллектор первого тра.нзистора соединен с шиной питания, а коллектор второго транзистора — с общей шиной, база первого транзистора соединена с выходом первого ключа и через резистор с шиной питания, о т л и ч а ю шийся тем, что, с целью повышения помехоустойчивости, в него введены резистор и второй ключ, причем резистор подключен между базой р-и-р транзистора и выкодным зажимом, выход второго ключа соединен базой р-п-р транзистора, а вход второго ключа соединен с входом первого ключа.

809569

Составитель И. Радько

Редактор Т. Мермелштейн Техред Н.Вабурка Корректор М. Шароши

Заказ 458/78

Тираж 999. Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, У(-35, Раушская наб., д. 4/5

Филиал ППП Патент", r. Ужгород, ул. Проектная, 4

2. Формирователь по и. 1, о т л и ч а ю шийся тем, что в него введен третий р-и-р транзистор, эмиттер которого подключен к шине питания а база и коллектор подключены соответственно к коллектору и эмиттеру п-р-и транзистора.

Источники информации, принятые во внимание при экспертизе

1. Импульсные схемы на полупроводННКоВНх IIpHOopBY.. Проектирование и расчет. Под ред. Гал перина Е. И. и

Степаненко И. П. "Советское радио", 1970, с. 66. рис. 220 (1).

2. Патент Великобритании Р 1462517, кл. Н 03 Т, опублик. 26.01.77 (прототип).