Коммутирующее устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕПЛЬСТВУ 111809570 (61) Дополнительное к авт. свид-ву (5f)aa. Кл.з

Н 03 К 17/60 (22) Заявлено 281277 (21) 2555951/ 8-21 с присоединением заявки М— (23) Приоритет—

Опубликовано 2892.81.6юллетемь Н9 8

Гесуяарствеиямй комитет

СССР яе ямам изебретеиий я еткрмтяй (53) УДК 621.382 (088.8) Дата опубликования описания 2802.81 (72) Автор изобретения

А. В. Фурман с

1 (71) Заявитель (54) КОММУТИРУЮИЕЕ УСТРОЙСТВО

Изобретение относится к коммутационной технике и может быть, в частности, использовано в многоступенчатых коммутаторах.

Извест ко,утирующие устройства, 5 содержащие операционный усилитель и коммутирующий элемент, включенный в цепь отрицательной обратной связи операционного усилителя и последовательно в коммутируемую цепь (11 .

Наиболее близким к предлагаемому по технической сущности является коммутирующее устройство, содержащее операционный усилитель, два ключевых элемента, блок управления и источник 15 питания, причем ключевые элементы последовательно включены в цепь отрицательной обратной связи операционного усилителя, точка соединения ключевых элементов непосредственно 20 связана с выходной клеммой устройства, а управляющие входы ключевых элементов подключены к выходам блока управления 2.11

Недостатком известных устройств является высокая погрешность коммутации., обусловленная явлением смещения нуля (дрейфом) операционного усилителя. 30

Цель изобретения — уменьшение погрешности коммутации.

Указанная цель достигается тем, что коммутирующее устройство, содержащее операционный усилитель, два ключевых элемента, блок управления и источник питания, причем ключевые элементы последовательно включены в цепь отрицательной обратной связи операционного усилителя, точка соединения ключевых элементов непосредственно связана с выходной клеммой устройства, а управляющие входы ключевых элементов подключены к выходам блока управления, дополнительно содержит операционный усилитель, два запоминающих конденсатора и десять ключевых элементов, причем в цепь отрицательной обратной связи операционного усилителя последовательно включены два дополнительных ключевых элемента, а точка соединения этих ключевых элементов подключена к входной клемме устройства, между инверсным входом и выходом каждого операционного усилителя включены дополнительные ключевые элементы, первые обкладки, запоминающих конденсаторов объединены и подключены к средней точке источника питания, вторая обкладка

809570 первого запоминающего конденсатора и вторая обкладка второго запоминающего конденсатора через дополнительные ключевые элементы соединены соответственно с выходом первого и неинверсным входом второго и с выходом второго и неинверсным входом первого операционных усилителей, неинверсныв ,входы операционных усилителей через дополнительные ключевые элементы связаны со средней точкой источника питания, а управляющие входы дополни- 1О тельных ключевых элементов подключены к выходам блока управления.

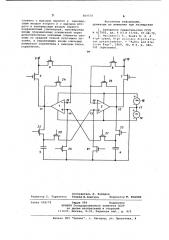

На чертеже представлена схема коммутирующего устройства.

Устройство содержит первый 1 и вто-15 рой 2 операционные усилители, первый

3 и второй 4 запоминающие конденсаторы, ключевые элементы 5-16 и источник 17 питания; точки соединения коммутирующих (ключевых) элементов 5, 6 и 7, 8,включенных в цепи отрицательных обратных связей операционных усилителей 1 и 2, подключены соответственно к входной 18 и выходной 19 клеммам устройства; ключевые элементы 20-27.

Работа коммутирующего устройства осуществляется при периодическом переводе его из активного режима коммутации в режим коррекции,,при кото- щ ром происходит запоминание уровня дрейфа нуля операционных усилителей и становится возможной компенсация этого дрейфа при работе устройства в режиме коммутации, что и приводит к увеличению точности коммутации электрического сигнала. По сигналу блока управления (не показан) в режиме запоминания уровня дрейфа замкнуты ключевые элементы 9-14, при этом неинверсные входы операционных усилителей 1 и 2 соединены сс средней точкой источника 17 питания. С помощью ключевых элементов 9 и 10 инверсные входы операционных усилителей 1 и 2 соединены с их выходами и усилители охвачены стопроцентными отрицательными обратными связями.

Напряжение с выходов операционных усилителей через зарядные ключевые элементы 11 и 12 заряжает конденса- gg торы 3 и 4 до напряжения, равного напряжению смещения нуля соответствующего операционного усилителя. В рабочем режиме комму ации по сигналу устройства управления замыкаются ключевые элементы 5-8, 15 и 21, а ключевые элементы 9-14 размжаются, Запомненные значения напряжения смещения нуля операционных усилителей

1 и 2 через ключевые элементы 15 и

16 подаются на неииверсные входы со- еО ответствующих операционных усилителей. В рабочем режиме коммутации операционные усилители 1 и 2 также охвачены стопроцентными отрицательными обратными связями с помощью клю- 65 чевых элементов 5, б и 7, 8. Ори этом на выходах операционных усилителей 1 и 2 устанавливаются напряжения, равные алгебраическим суммам собственного значения напряжения смещения нуля одного операционного усилителя и запомненного значения напряжения смещения нуля другого операционного усилителя. Напряжение смещения нуля каждого операционного усилителя входит в эти алгебраические суммы с одним и тем же знаком, так как запомненные значения напряжений смещения нуля подаются на неинверсные входы операционных усилителей 1 и 2. Поэтому между входной 18 и выходной 19 клеммами устройства устанавливается разность между алгебраическими суммами напряжений, имеющими место на выходах операционных у илителей 1 и 2. Так как составляющие этих сумм практически равны по величине и имеют одинаковые знаки, то величина и нестабильность остаточного напряжения, вызванного напряжением смещения нуля усилителя, между клеммами 18 и 19 уменьшена в большое число раз. Малое значение остаточного напряжения между входной и выходной клеммами коммутирующего устройства приводит к увеличению точности коммутации.

Формула изобретения

Кож утирующее устройство, содержащее операционный усилитель, два ключевых элемента, блок управления и источник питания, причем ключевые элементы последовательно включены в цепь отрицательной обратной связи операционного усилителя, точка соединения ключевых элементов непосредственно связана с выходной клеммой устройства, а управляющие входы ключевых элементов подключены к выходам блока управления, о т л и ч а ю щ е е с я тем

/ что, с целью уменьшения погрешности коммутации, оно дополнительно содержит операционный усилитель, два запоминающих конденсатора и десять ключевых элементов, причем s цепь отрицательной обратной связи операционного усилителя последовательно включены два дополнительных ключевых элемента, а точка соединения этих ключевых элементов подключена к входной клемме устройства, между инверсным входом и выходом каждого операционного усилителя включены дополнительные ключевые элементы, первые обкладки запоминающих конденсаторов объединены и подключены к средней точке источника питания, вторая обкладка пер вого запоминающего конденсатора и вторая обкладка второго запоминающего конденоатора через дополнительные ключевые элементы соединены соответ809570

Составитель В. Нефедов

Редактор С. Тараненко Техред М.Коштура Корректор М. Шароши

Тираж 999 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 458/78

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 ственно с выходом первОго и неинверсным входом второго и с выходом второго и неинверсным входом первого операционных усилителей, неинверсные входы операционных усилителей через дополнительные ключевые элементы связаны со средней точкой источника питания, а управляющие входы ключевых элементов подключены к выходам блока управления.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР д 417905, кл. Н 03 К 17/60, 07.08.72.

2. Marjanovic S., Noaks О. R. Л

high speed high accuracy digittaI!y.set potentiometer. — "Radio and E lectron Engr" 19б9, 38, Р б, р. 345351 (прототип).