Многоканальная система связи

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Реслублик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. саид-ву— (я)м. кл.з

Н 04 J 11/00 (22) Заявлено28. 07. 78 (21) 2652991/18-09 с присоединением заявки Нов (23) Приоритет—

Государственный комнтет

СССР ио делам нзобретеннн

N открытнй

Опубликовано 28.0281. Бюллетень М 8 (53) УДК 621.З96. 4 (088.8) Дата опубликования описания 280231

r (72) Авторы изобретения

В.А.Жилич и О.A.Лавлов (71) Заявитель (54) МНОГОКАНАЛЬНАЯ СИСТЕМА СВЯЗИ

Изобретение относится к электросвязи и может использоваться для уплотнения проводных, радио-,радиорелейных и космических линий связи.

Известна многоканальная система связи, содержащая на передающей стороне и перемножителей (где и число информационных каналов), н* первые входы которых поданы информационные сигналы вторые входы перемножителей соединены с выходами формирователя сигналов адресов передачи, а выходы подключены к входам блока логической обработки, например сумматора по модулю два, выход которого подключен к первому входу передатчика, второй вход которого соединен с синхровыходом формирователя сигналов адреса передачи через синхроблок, а на приемной стороне

2 -1 каналов обработки, каждый из которых содержит последовательно соединенные интегратор и решающий блок, а также дешифратор, входы которого подключены к выходам решающих блоков .каждого из каналов обработки, перемножители и синхроблок, вход которого соединен с первым выходом при" емника (11 .

Однако данная система связи является сложной, что делает ее неудобной в использовании.

Цель изобретения — упрощение системы связи.

Указанная цель достигается тем, что в многоканальной системе связи, содержащей на передающей, стороне и перемножителей (где и — число информационных каналов), на первые входы которых поданы информационные сигналы, вторые входы перемножителей соединены с выходами формирователя сигналов адресов передачи, а выходы

15 подключены к входам блока логической обработки, например сумматора по модулю два, выход которого подключен к первому входу передатчика, второй вход которого соединен с синхровыхо20 дом формирователя сигналов адресов передачи через синхроблок, а на приемной стороне — 2 -1 каналов обработPl ки, каждый из которых содержит последовательно соединенные интегратор

25 и решающий блок, а также дешифратор,. входы которого подключены к выходам решающих блоков каждого из каналов обработки, перемножители н синхроблок, вход которого соединен с пер30 вым выходом приемника, исключен фор809611 мирователь сигналов приема, на приемной стороне перемножители соединены в последовательные цепи, причем входы и последовательных цепей,первая из которых содержит и перемножителей, а каждая последующая — на один перемножитель меньше, объединены и соединены со вторым входом приемника,.к выходу каждого К-го (где

К .= 3, 4,...n) перемножителя каждой последовательной цепи подключено К-2 последовательных цепей, первая из которых содержит К-2 перемножителей, а каждая послецующая — на один перемножитель меньше, вторые входы всех

К-ых перемножителей соединены между собой и подключены к соответствующим выходам формирователя сигналов адресов передачи, вход которого соединен с выходом синхроблока, а выходы всех перемножителей подключены к соответствующим выходам формирователя сиг- 20 налов адресов передачи, вход которого соединен с выходом. синхроблока, а выходы всех перемножителей подключены ко входам интеграторов соответствующих каналов обработки. 25

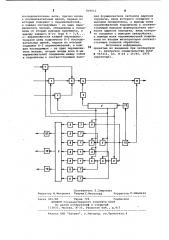

Не чертеже приведена структурная электрическая схема предлагаемой связи.

Многоканальная система связи содержит на передающей стороне и перемножителей 1, формирователь 2 сигналов адресов передачи, блок 3 логической обработки, передатчик 4 и синхроблок 5, на приемной стороне — n перемножителей б, интеграторы 7, решающие „ блоки 8,.дешифратор 9, получатели

10 сообщений, линия 11 связи приемник 12 и синхроблок 13.

Система работает следующим образом.

Двоичные .символы сообщения в каж- 46 дом из и каналов подаются на перемножитель 1, куда также поступают двоичные символы адресного кодового слова данного канала, вырабатываемые формирователем 2 сигналов адресов (генератором двоичных последовательчостей Радамахера) . В результате с выхода перемножителя 1 либо снимается двоичная последовательн6сть Радамахера (если по данному каналу передается ствол "1"), либо отсутствует (если по данному каналу передается, символ "0"). Полученные, таким обфазом, адресные кодовые слова из всех каналов попадают в блок 3 логической обработки (сумматор по модулю два), на выходе которого формируется групповой сигнал, представляющий собой одну из функций ПЭЛИ. Этот сигнал вместе с сигналами синхронизации, поступающими от синхроблока 5, передается с помощью передатчика 4 по линии 11 связи.

На приемной стороне групповой сигнал с выхода приемника 12 поступает на последовательные цепи перемножите- 6 лей 6. В перемножителях 6 групповой сигнал перемножается с сигналами адресов от формирователя 2 (генератора двоичных ортогональных последовательностей Радамахера),который синхронИзируется синхроблоком 13, вырабатывающим сигналы синхронизации из сигнала, который проходит на его вход с выхода приемника 12. С выходов перемножителей 6 сигналы поступают на другие последовательные цепи перемножителей 6 и одновременно поступают на последовательно соединенные интегратор 7 и решающий блок 8, который, сравнивая полученный сигнал с выбранным порогом, принимает решение о принятии "1" или "0". Сигналы с выходов решающих блоков 8 подаются на входы дешифратора 9. В зависимости от того, на какой вход дешифратора поступает "1", на era выходах формируются сигналы "1", которые подаются получателям 10 сообщений.

Изменение связей значительно уменьшает количество сигналов, формируемых Формирователем сигналов адресов. Так при n = 4 для известной системы требуется 15 сигналов, а для предлагаемой — необходимо только 4.

При n = 5 для предлагаемой системы уже требуется на 26 сигналов меньше.

Таким образом, с увеличением числа каналов выигрыш нарастает очень быстро. Уменьшение необходимого числа каналов позволяет сократить количество элементов„ необходимых для изготов.пения системы.

Формула изобретения

Иногоканальная система связи, содержащая на передающей стороне перемножителей (где г: — число информационных каналов), на первые входы которых поданы информационные сигналы, вторые входы перемножителей соединены с выходами формирователя сигналов адресов передачи, а выходы подключены к входам блока логической обработки, например сумматора по модулю два, выход которого подключен к первому входу передатчика, второй вход которого соединен с синхровыходом формирователя сигналов адресов передачи через синхроблок, а на приемной стороне — 2"-1 каналов обработки, каждый из которых содержит последовательно соединенные интегратор и решающий блок, а также дешифратор, входы которого подключены к выходам решающих блоков каждого из каналов обработки, перемножители и синхроблок, вход которого соединен с первым выходом приемника, о т л и ч а ю щ à яс я тем, что, с целью упрощения системы связи путем исключения формирователя сигналов приема, на приемной стороне перемножители соединены в

809611

Составитель E.Ñìèðíoâà

Редактор М.Митровка Техред С.Мигунова Корректор Н.Швыдкая

Заказ 461/80 Тираж 709 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113635, Москва, Е-35, Раушская наб., д.4/5

Филиал ППП "Патент", г.ужгород, ул.Проектная,4 последовательные цепи, причем входы и последовательных цепей, первая из которых содержит и перемножителей, а каждая последующая — на один перемножитель меньше, объединены и соединены со вторым выходом приемника, к выходу каждого К-го (где К = 3,4,... п) перемножителя каждой последова-тельной цепи подключено К-2 последовательных цепей, первая из которых содержит К-2 перемножителей, а каждая последующая — на один перемножитель меньше, вторые входы всех К-ых перемножителей соединены между собой и подключены к соответствующим выходам формирователя сигналов адресов передачи, вход которого соединен с выходом синхроблока„ а выходы всех перемножителей подключены к соответствующим выходам формирователя сигналов адресов передачи, вход которого соединен с выходом синхроблока, а выходы всех перемножителей подключены ко входам интеграторов соответствующих каналов обработки.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 567211, кл. Н 04 J ii/00, 1975 (прототип).