Устройство тактовой синхронизациии регенерации

Иллюстрации

Показать всеРеферат

Сеез Советсник

Сецналнстическмк

Реслублнк

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВ ВЯЛЬСУВУ

«i)809620

Г

Ф

ar - (61) Дополнительное к авт. санд-ау (22) Заявлено 0904.79 (2! ) 2749456/18-09 с присоединением заявки Ж (23) Приоритет

Опубликовано 2802,81 БЮллетеиь 149 8

Дата опубликования описания 280281

Р1 1М. К .3

Н 04 Ь 7/02

Государстаеииый комитет

СССР

flo делам изобретеиий и открытий (ЗЗ) ДК 621. 394. .662(088.8) (72) Автор изобретения

Н.П.Хворова (71) Заявитель (54) УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ

И РЕРЕНЕРАЦИИ

Изобретение относится к радиосвязи и может использоваться в системах передачи дискретной информации.

Известно устройство тактовой синхронизации и регенерации, содержащее последовательно соединенные задающий генератор и делитель частоты, выходы которого подключены соответственно ко входам Формирователя сигнала фа. зовых эон и к управляющим входам деЙифратора, к другим входам которого подключены выходы блока памяти, а также последовательно соединенные элемент ИЛИ, блок стробирования и формирователь выходного сигнала, при этом выходы дешифратора подключены ко входам элемента ИЛИ (1) .

Однако известное устройство имеет низкие точность н помехоустойчивость синхронизации, так как измерение величины зоны рассогласования производится на интервале одной посылки, и результат определяется мгновенным отношением сигнал/шум. Кроме того в известном устройстве невозможен прием коротких сообщений и имеют место потери информации в начале сеанса связи и после длительных перерывов связи

Цель изобретения — повышение точности и помехоустойчивости синхронизации, а также обеспечение синхронизации коротких сообщений и уменьшение потерь информации.

Поставленная цель достигается тем, что в устройство тактовой синхрониза-. ции и регенерации введены последова-

t0 тельно соединенные сумматор, регистр суммы и блок деления, а также-формирователь сигнала зон анализа, элеьеиФ задержки, регистр числа фронтов сигнала и последовательно соединенные счетчик фронтов сигнаЛа и пороговый блок, выход которого подключен к объединенным управляющим входам регистра суммы, регистра числа фронтов сигнала и блока деления и входу эле2р мента задержки, выход которого подключен к управляющему входу блока памяти, к соответствующим входам которого подключены выходы блока деления, при этом первый выхоД формирователя сигна1

25 ла эон анализа подключен к соответствующему входу сумматора и первому входу счетчика фронтов сигнала, вто-( рой вход которого объединен с управляющими входами формирователя сигнала

30.фазовых зон и сумматора, а выходы

809620 счетчика фронтов сигнала через регистр числа фронтов сигнала подключены к соответствующим входам блока деления, причем второй выход формирователя сигнала зон анализа подключен к управляющему входу порогового блока, а ко входам сумматора соответственно подключены выходы формирователя сигнала фазовых эон.

Также введена дискретная линия задержки (ДЛЗ), вход которой объединен с управляющим входом формирователя сигнала Фазовых эон, а выход подключен ко второму входу блока стробирования.

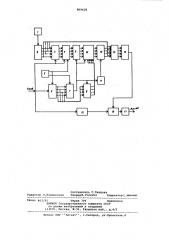

На чертеже приведена структурная электрическая схема предлагаемого 15 устройства.

Устройство тактовой синхронизации и регенерации содержит задающий генератор 1, делитель 2 частоты, формирователь 3 сигнала фазовых эон, сум- Щ матор 4, формирователь 5 сигнала зон анализа, счетчик 6 фронтов сигнала, пороговый блок 7, регистр 8 числа фронтов сигнала, регистр 9 суммы, блок 10 деления, элемент 11 задержки, блок 12 памяти, дешифратор 13, элемент

14 ИЛИ, ДЛЗ 15, блок 16 стробирования и формирователь 17 выходного сигнала, выход которого является выходом устройства, входом которого являются объединенные входы счетчика 16,ДЛЗ 15 и управляющие входы формироватеЛя 3 и сумматора 4.

Устройство работает следующим образом.

Сигнал с выхода задающего генератора 1 поступает на делитель 2 частоты, коэффициент деления которого выбран таким образом, что частота импульсов на выходе его последнего разряда равна тактовой. Запись кода 40 состояний разрядов делителя частоты

2 производится в Формирователе 3 сигнала фазовых эон в моменты появления на его управляющем входе фронтов (перепадов) входного сигнала. Число

К различных состояний делителя частоты 2 равно его коэффициенту деления, смена состояний происходит с частотой, равной частоте задающего генератора 1. Таким образом осуществляется разбиение периода тактовой частоты на К эон, ширина ьЧ каждой из которых равна

55 и запись в формирователе 3 двоичного кода номеров эон, синфазных фронтам входного сигнала. Каждый фронт сигнала, поступающий на управляющий вход сумматора 4, представляет собой 60 сигнал разрешения суммирования, хранящегося в сумматоре 4 числа с кодом зоны, синфазной данному фронту сигнала. Формирователь 5 производит разбиение сеанса связи на равные зоны. 65

С первого выхода формирователя 5 следует последовательность коротких импульсов, соответствующих началу зон а ализа, à со второго — последовательность коротких импульсов, соответствующих концу зон анализа.

Счетчик 6 осуществляет подсчет количества фронтов сигнала в зоне анализа. Установка в нулевое состояние сумматора 4 и счетчика 6 в начале эон анализа производится поступающи и на их входы импульсами с первого выхода формирователя 5. Каждым импульсом со второго выхода формирователя 5 на управляющий вход порогового блока 7 подается сигнал разрешения сравнения количества фронтов, подсчитанного счетчиком 6 с пороговым значением. В случае повышения порожвого значения сигнал с выхода порогового блока 7, поступающий на управляющие входы регистра 8, регистра 9 суммы и блока. деления 10 разрешает поочередное осуществление следующих операций: запись двоичного кода количества фронтов сигнала в зоне анализа счетчика 6 в регистре 8; запись двоичного кода числа, представляющего собой сумму номеров зон, синфаэных фронтам сигнала рассматриваемой зоны анализа, с выходов сумматора 4 в регистр 9 суммы; деление числа, записанного в регистре 9 суммы, на число, представленное в регистре 8, блоком 10 деления.

Сигнал с выхода порогового блока 7 поступает также на элемент 11 задержки. По истечении времени, достаточного для осуществления операции деле ния, с выхода элемента 11 задержки на управляющий вход блока 12 памяти поступает сигнал разрешения записи в блок 12 памяти двоичного кода чйсла, представляющего результат деления. Блок 12 памяти хранит эту информацию до поступления следующего сигнала с элемента 11 задержки. Число, записанное в блок 12 памяти, представляет собой среднее в течение эоны анализа рассогласование входного сигнала и тактовых импульсов.

Дешифратор 13 выдает сигнал на соответствующем выходе в моменты времени, когда состояние разрядов делителя 2 частаты совпадает с состояниями соответствующих разрядов блока 12 памяти.

Таким образом производится сдвиг импульсов тактовой частоты на время, равное измеренному среднему рассогласованию.

Импульсы с выхода дешифратора 13 поступают на элемент 14 ИЛИ и затем используются для регенерации сигнала, Входной сигнал поступает на ДЛЭ 15, время задержки которой выбирается равным сумме длительностей зоныанализа и задержки элемента 11 задержки. В блоке 16 стробирования производится сдвиг тактовых импульсов на

809620 половину посылки и определение полярности входного сигнала в моменты времени, соответствующие измеренным положениям середины посылок. Формирователь 17 выдает на выход устройства регенерированный сигнал требуемой величины и стандартной длительности °

Предлагаемое устройство обладает повышенной точностью и помехоустойчивостью синхронизации. Кроме того, обеспечивается требуемая точность фазирования и сохранение синхронизма в перерывах связи и при передаче длительных сигналов одной полярности.

Устройство также позволяет уменьшить потери информации в процессе вхождения в синхронизм в начале сеанса свя- 1% зи и после длительных перерывов связи и обеспечивает прием коротких телеграмм.

Формула изобретения

1. Устройство тактовой синхронизации и регенерации, содержащее последовательно соединенные задающий гене- ратор и делитель частоты, выходы которого подключены соответственно ко входам формирователя сигнала фазовых эон и к управляющим входам дешифратора, к другим входам которого подклю;чены выходы блока памяти, а также последовательно соединенные элемент

ИЛИ, блок стробирования и формирователь выходного сигнала, при этом выходы дешифратора подключены ко входам элемента ИЛИ, о т л и ч а ю— щ е е с я тем, что,- с целью повышения точности и помехоустойчивости синхронизации, в него введены последовательно соединенные сумматор, регистр суммы и блок деления, а также 1О формирователь сигнала зон анализа, элемент задержки, регистр числа фронTQB сигнала и последовательно соединенные счетчик фронтов сигнала и пороговый блок, выход которого подключен к объединенным управляющим входам регистра суммы, регистра числа фронтов сигнала и блока деления и входу элемента задержки, выход которого подключен к управляющему входу блока памяти, к соответствующим входам которого подключены выходы блока деления, ape этом первый выход формирователя сиг нала зон анализа подключен к соответствующему входу сумматора и первому входу счетчика фронтов сигнала, второй вход которого объединен:с управляющими входами формирователя сигнала фазовых зон и сумматора, а выходы счетчика фронтов сигнала через регистр числа фронтов сигнала подключены к соответствующим входам блока деле" ния, причем второй выход формирователя сигнала зон анализа подключен к управляющему входу порогового блока, а ко входам сумматора соответственно подключены выходы формирователя сигнала фазовых зон.

2. Устройство по п.1, о т л и ч аю щ е е с я тем, что, с целью обеспечения синхронизации коротких сообщений и уменьшения потерь информации, введена дискретная линия задержки, вход которой объединен с управляющим входом формирователя сигнала фазовых зон,а выход подключен ко второму входу блока стробирования.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 594594, кл. Н 04 L 7/02, 1976 (прототип).

809620.Составитель Г.Теплова

Техред М. Голинка Корректор C . Мекмар

-Редактор Л.Пчелинская

Филиал ППП Патент, r.Óæãîðîä, ул.Проектная,4

Заказ 462/81 Тираж 709 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5