Устройство синхронизации

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОУСКОМУ СВИ НЗЛЬСЗЗУ

Сеез С©ветских

Сецмалнстнчесмих

Республик (ii)809621 (61) Дополнительное к авт. сеид-ву (22) Заявлено 1304 79 (21) 2755149/18-09 с присоединением заявки NP (23) Приоритет

Опубликовано 289281. Бюллетень N9 8

Дата опубликования описания 28Q 231

H 04 L 7/02

ГесуяврствеввыА коинтет

СССР яв давал изобретений я еткрмтиА (ÇÇ) УДЫ 621. 394, .662 (088. 8) (72) Автор. изобретения

В; Г. Таценко (П) Заявитель (54) УСТРОЙСТВО СИНХРОНИЗАЦИИ

Изобретение относится к радиотехнике и может использоваться в измерительных системах оптического диапазона.

Известно устройство синхронизации для измерения допплеровского сдвига частоты поднесущей в оптических изме рительных системах, содержащее первый сумматор, ко входам которого подключены выходы первого линейного фильтра и первого интегратора, а выход первого сумматора подключен к первому входу второго сумматора, выход которого через последовательно соединенные второй интегратор, нелинейный фазовый модулятор и третий сумматор подключен к первому входу первого коммутатора, к управляющему ходу которого подключен выход решающего блока, информа.ционный вход которого объединен с первым. входом первого блока вычитания, а первый выход первого коммутатора через последовательно соединенные логарифмический и дифференциальный усилители подключен к первому входу первого умножителя, ко второму и третьему входам которого подключены соответственно через фазосдвигающую цепь второй выход нелинейного фазового модулятора и через последователь- ЗО но соединенные третий интегратор и первый блок вычитания - выход второго умножителя, к первому входу которого подключен выход блока автоматической. регулировки усиления (АРу), при этом ко второму входу решающего блока подключен выход источника эталонного напряжения, а ко второму входу третьего суюаатора подключен выход источника опорйого напряжения (1) .

Однако известное устройство обеспечивает сравнительно невысокую точность синхронизации.

Цель изобретения — повышение точности синхронизации.

Поставленная цель достигается тем, что в устройство введены второй коммутатор, два усилителя и блок вычитания, а также последовательно соединенные третий усилитель, четвертый суьелатор и второй линейный фильтр, выход, которого подключен к третьему входу первого коммутатора, второй выход которого подключен ко второму входу второго умножителя, к третьему входу которого и управляющему входу второго коммутатора подключен выход решающего блоха, при этом ко второму и третьему вхо-.

809621 дам второго коммутатора подключены соответственно выход первого умножителя и первый выход первого блока вычитания, второй выход которого подключен.ко входу третьего усилителя, а выход второго коммутатора подключен к объединенным по входу второму сумматору, первому интегратору, первому линейному фильтру и блоку АРУ, при этом ко входам первого и второго усилителей подключены соответственно первый выход нелинейного фазового модулятора и выход третьего сумматора, а выходы первого и второго усилиТелей подключены ко входам второго блока вычитания, выход которого подключен ко второму входу четвертого сумматора.

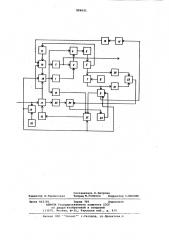

На чертеже приведена структурная электрическая схема предлагаемого устройства.

Устройство синхронизации содержит первый линейный фильтр 1, первый интегратор 2, первый сумматор 3, второй сумматор 4, второй интегратор 5, нелинейный Фазовый модулятор 6, третий сумматор 7, источник 8 опорного напряжения, первый коммутатор 9, блок 10 АРУ, фаэосдвигающую цепь 11, третий интегратор 12, первый блок 13 вычитания, первый умножитель 14, логарифмический 15 и дифференциальнь1й 16 усилители, решающий блок 17, источйик 18 эталонного напряжения, второй коммутатор 19, усилители 20 и 21, второй блок 22 вычитания, второй линейный фильтр 23, четвертый сумматор 24, третий усилитель 25 и второй умножитель 26, Предлагаемое устройство работает следующим образом., Смесь сигнала и шума поступает на первый вход блока 13 и на информационный вход решающего блока 17. Ко второму входу решающего"блока 17 подключен источник 18. Напряжение на информационном входе решающего блока 17 U пропорционально мощности принимаемого излучения. Постоянное напряжение с выхода источника 18

UpI,IIpoIIopIJионально пороговому значенйю мощности, при котором статистика сигнала на входе устройства синхронизации принимает пуассоновский характер. В решающем блоке 17 производится сравнение среднеквадратического значения напряжения U с опорным

Воя ° В случае, если U o UzII решающий блок 17 подает команду на первый

9 и второй 19 коммутаторы. При этом первый коммутатор 9 подключает ко второму входу второго умножителя 26 выход второго линейного фильтра 23 и отключает от него выход третьего сумматора 7, Второй коммутатор 19 отключает от входов первого линейнога фильтра 1, первого интегратора

2, блока 10. и второго сумматора 4 выход первого умножителя 14 и подключает к ним первый выход блока 13 °

Напряжение с первого выхода нелинейного Фазового модулятора 6 поступает на первый вход третьего сумматора. 7 и через усилитель 20 на вход блока 22, На второй вход сумматора 7 поступает сигнал от источника 8. Напряжение с выхода сумматора 7 через усилитель 21 поступает на другой вход блока 22. С выхода блока 22 напряжение поступает на второй вход четвертого сумматора 24, на первый вход которого через третий усилитель

25 поступает напряжение со второго выхода блока 13..

Напряжение с выхода четвертого сумматора 24 поступает на вход второго линейного фильтра 23, с выхода которого сигнал идет через первый коммутатор 9 на второй вход второго ум20 ножителя 26, на первый вход которого подается напряжение с выхода блока

10.

Напряжение с выхода второго умножителя 26 через третий интегратор 12 поступает на блок 13, выход которого через второй коммутатор 19 подключен ко входам блока 10, первого линейного фильтра 1, первого интегратора 2 и второго сумматора 4.

ЗО Напряжение на выходе первого линейного фильтра 1 пропорционально

Флюктуациям частоты ov(t) оптической несущей, а напряжение с выхода первого интегратора 2 -допплеровскому сдвигу Яд частоты модуляции. Выход первого интегратора 2 одновременно является выходом всего устройства синхронизации.

С выхода сумматора 4 напряжение через второй интегратор 5 поступает на вход нелинейного фазового модулятора 6, при этом напряженке на выходе второго интегратора 5 пропорционально оценке полной фазы входного сигнала. Таким образом, происходит подстройка фазы сигнала нелинейного фазового модулятора 6 к Фазе входного сигнала.

В случае, если уровень мощности принимаемого излучения таков, что щ U с UoII, решающий блок 17 выдает команды на первый 9 и второй коммутаторы, по которым второй коммутатор 19 подключает выход первого умножителя 14 ко входам блока 10, первого линейного Фильтра 1, IIepaoro интегратора 2 и второго сумматора 4, отключая от них выход блока 13, а первый коммутатор 9 подключает выход третьего сумматора 7 ко второму входу второго умножителя 26 и ко

60 входу логарифмического усилителя

15, Одновременно выход второго линейного фильтра 23 отключается от второго входа второго умножителя

26. Таким образом, на третий вход

65 .первого умножителя 14 поступает на809621 пряжение с выхода третьего сумматора

7, прошедшее второй умножитель 26, третий интегратор 12 и блок 13, а на первый вход — прошедшее логарифмический 15 и дифференциальный 16 усилители.

В остальном работа устройства синхронизации в этом режиме не отличается от режима, когда U ) Пап.

Предлагаемое устройство синхронизации позволяет улучшить точность измерения допплеровского сдвига частоты во всем диапазоне мощностей принимаемого излучения.

Формула изобретения

Устройство синхронизации для измерения допплеровского сдвига частоты поднесущей в оптических измерительных системах, содержащее первый сум- Щ матор, ко входам которого подключены выходы первого линейного фильтра и первого интегратора, а выход первого сумматора подключен к первому входу . второго сумматора, выход которого через последовательно соединенные второй интегратор, нелинейный фазовый модулятор и третий сумматор подключен к первому входу первого коммутатора, к управляющему входу которого подключен выход решающего блока, информационный вход которого объединен с первым входом первого блока вычитания, а первый выход первого коммутатора через последовательно соединенные логарифмический и дифференциальный усилители подключен к первому входу первого умножителя, ко второму и третьему входам которого подключены соответственно через фазосдвигающую цепь второй выход не- 4О линейного фазового модулятора и через последовательно соединенные третий интегратор и первый блок вы" читания - выход второго умножителя,. к первому входу которого подключен выход блока автоматической регулиров- ки усиления, при этом ко второму входу решающего блока подключен выход источника эталонного напряжения, а ко второму входу третьего сумматора подключен выход источника опорного напряжения, о т л и ч а ю щ е ес я тем, что, с целью повышения точности синхронизации, в него введены второй коммутатор, два усилителя и блок вычитания, а также последовательно соединенные третий усилитель, четвертый сумматор и второй линейный фильтр, выход которого подключен к третьему входу первого коммутатора, второй выход которого подключен ко второму входу второго умножителя," к третьему входу которого и управляющему входу второго коммутатора под- ключен выход решающего блока, при этом ко второму и третьему входам второго коммутатора подключены соответственно выход первого умножителя и первый выход первого блока вычитания, второй выход которого подключен ко входу третьего усилителя, а выход второго коммутатора подключен к объединенным по входу второму сумматору, первому интегратору, йервому линейному фильтру и блоку АРУ,, при этом ко входам первого и второго усилителей подключены соответственно первый выход нелинейного фазового модулятора и выход третьего сумматора, а выходы первого и второго. усилителей подключены ко входам второго блока вычитания, выход которого подключен ко второму входу четвертого суммато" ра °

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 648016 кл. Н 04 Ь 7/02, 1977

{ прототип) .

Составитель Е.Петрова тееред И.ролееке Корректор С.иекмер

Редактор Л.Пчелинская

Филиал ППП Патент г.Ужгород, ул.Проектная,4

Заказ 462/81 Тираж 709 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5