Временной коммутатор асинхронныхимпульсных сигналов

Иллюстрации

Показать всеРеферат

Союз Советскнк

ИЗОБРЕТЕНИЯ

«»S 09629 к авюескомю свидютвльствю (6t) Дополнительное к авт. саид-ву (22) Заявлено 10.04.79 (21) 2750732/18-09 (53)М К 3 с присоединением заявки М

H 04 Ь 11/20

t oñóäàðñòâåíìì комитет

СССР ио делам изобретеиий и открмтий (23) Приоритет

Опубликовано 280281. Бюллетень N9. 8

Дата опубликования описания 280281

М) У В б21. 394, ° 42 (088.8) A.Ô.Ëåîíoâ, В.П. Чуркин, A.A. Величенко, Ю.И.Иеланин н В.В.Климов (72) Авторы изобретения (73) Заявитель (5 4 ) ВРЕМЕННОЙ КОИИУ1А1ОР АСИНХРОННЫХ ИМПУЛЬСНЫХ

СИГНАЛОВ

Изобретение относится к импульс= ной технике и может использоваться для коммутации цифровых каналов .

Известен временной коммутатор асинхронных импульсных сигналов, содержащий управляющий блок, преобразователь, блок памяти, датчик меток времени, адресно-кодовые блоки и выходной блок (1) .

Однако в известном временном коммутаторе велики искажения коммутируемых сигналов.

Цель изобретения - уменьшение искажений коммутируемых сигналов .

Поставленная. цель достигается тем, 15 что во временной коммутатор асинхронных импульсных сигналов, содержащий управляющнй блок, преобразователь, блок памяти, датчик меток времени,. адресно-кодовые блоки и выходной 20 блок, введены приемник служебных сигналов, анализатор и буферные накопители, соответствующие выходы которых подключены ко входам анализатора, выход которого соединен с соответствукщими входами буферных накопителей, другие входы которых соединены с выходами адресно-кодовых блоков, выход датчика меток времени подключен .к соответствующим входам буферных на- ЗО копнтелей и к первому входу выходно" го блока, второй вход которого соединен с соответствующими выходами буферных накопителей и с первым входом преобразователя, второй вход которого соединен с соответствующими выходами буферных накопителей и с первыми входами блока памяти и приемника служебных сигналов, выход которого одключен ко входу управляющего блока, выход блока памяти соединен с третьим входом выходного блока.

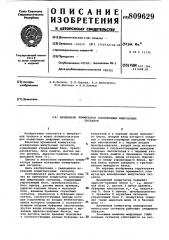

На чертеже изображена структурная электрическая схема временного коммутатора асинхронных импульсных сигналов.

Временной коммутатор содержит адресно-кодовые блоки 1.,- 1„, выходной блок 2, датчик 3 меток времени, буферные накопители 4 - 4,„ анализатор 5, блок б памяти, преобразователь

7, приемник 8 служебных сигналов, управляющий блок 9. Коммутатор содержит также адресную шину 10 и базовую шину ll °

Временной коммутатор асинхронных импульсных сигналов работает следующим образом.

Значащие моменты модуляции (ЗММ) входных сигналов уплотняются на вхо809629 де устройства и вместе с адресом соответствующего комплекта по адреснокодовому блоку 1 записываются в буферный накопитель 4 (БН,). Одновременно с записью адреса с БН 4 записывается код времени поступления ЗМИ, выда ваемый датчиком 3 меток времени, БН 4 обеспечивает запись нескольких управляющих слов, включающих в себя адрес канала, по которому поступил

ЗИМ, и код времени его поступления.

Емкость БН 4 определяется требуемой минимальной величиной краевых искажений. Очередность считывания информации на БН 4„- 4 осуществляется анализатором 5.

Информация о количестве управляю- t5 щих слов, записанных в каждом иэ

БН 4 — 4,передается по дополнительному выходу БН 4 на соответствующие входы анализатора 5, который осуществляет считывание информации из БН 4 Щ с наибольшим заполнением памяти.

При этом обеспечивается минимальная задержка при записи управляющих слов в БН 4.

Считываемый из БН 4 адрес активного канала поступает на адресную шину 10, а код меток времени — на фазовую шину 11. В блоке 6 памяти, преобразователе 7 и приемнике 8 служебных сигналов каждому входу коммутатора выделяется ячейка памяти .

В ячейку памяти блока 6 памяти записывается адрес выходного канального комплекта, с которым установлено соединение. Этот адрес считывается иэ блока 6 памяти при возбуждении адресной шины 10 и вместе с кодом времени передается в выходной блок 2.

Одновременно в выходной блок 2 иэ датчика 3 меток времени поступает код текущего времени. 40

В выходном блоке 2 информация в выходной канал выдается с постоянной задер>ккой относительно кода времени, поступающего по фазовой шине

11. При этом обеспечивается компенсация переменных временных задержек в групповом тракте.

С помощью преобразователя 7 осуществляется выделение информационных символов в каждом из коммутируемых каналов. При этом используются коды меток времени поступления ЗММ на вход БН 4> передаваемые по фаэовой шине 11.

Выделенные в преобразователе 7 символы(группы символов) передаются в приемник 8 служебных сигналов, выполненный, например, в виде логического блока, соединенного с запоминающим блоком. Логический блок может представлять собой обычный индиви- 40 дуальный приемник управляющих сигналов, запоминающие элементы которого соединены с запоминающим: блоком.

Запоминающий блок содержит индивидуальные для каждого коммутируемого канала ячейки памяти. При возбуждении адресной шины 10 информация с соответствующей ячейки запоминающего блока считывается в логический блок, анализируется и при необходимости, т.е. приеме определенного сигнала, выдается в управляющий блок 9. Такое решение позволяет уменьшить объем индивидуального оборудования, необходимого для передачи управляющей информации, и упростить сопряжение с управляющим блоком 9.

Применение предлагаемого устройства значительно увеличивает пропускную способность групповых трактов временных адресно-кодовых коммутационных систем, а следовательно, уменьшает количество и емкость пространственных ступеней коммутации.

Так, в среднескоростных системах коммутации применение данного временного коммутатора позволяет уменьшить объем оборудования коммутационных систем в 2-10 раз в зависимости от е>кости.

Применение группового преобразова» ния сигналов в сочетании с групповым приемом сигналов управления значительно уменьшает нагрузку на управляющий блок и обеспечивает более экономичное построение вычислительного комплекса.

Формула изобретения

Временной коммутатор асинхронных импульсных сигналов, содержащий управляющий блок, преобразователь, блок памяти, датчик меток времени, адреснокодовые блоки и выходной блок, о т л и ч а ю шийся тем, что, с целью уменьшения искажений коммутируемых сигналов, в него введены приемник слу>кебных сигналов, анализатор и буферные накопители, соответствующие выходы которых подключены ко входам анализатора, выход которого соединен с соответствующими входами буферных накопителей, другие входы которых соединены с выходами адресно-кодовых блоков, выход датчика меток времени подключен к соответствующим входам буферных накопителей и к первому входу выходного блока, второй вход которого соединен с соответствующими выходами буферных накопителей и с первым входом преобразователя, второй вход которого соединен с соответствующими выходами буферных накопителей и с первыми входами блока памяти и приемника служебных сигналов, выход которого подключен ко входу управляющего блока, выход блока памяти соединен с третьим входом выходного блока.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 566382, кл. Н 04 L 11/20, 1976.

809629

Составитель Н.Пантелеева

Редактор Л.Пчелинская ТехредЖ.Кастелевич Корректор С.Шекмар

Заказ 462/81 Тираж 709 Подписное

HHHHIIH Государственного комитета СССР по делам иэобретений и открытий

113035, Москва, Ж-35, Раутаская наб., д. 4/5

Филиал ППП Патент, г.ужгород, ул.Проектная, 4