Система для передачи и приема данныхс решающей обратной связью

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДВПИЬСТВУ

Союз Советских.Социалистических

Реслублик

<о809639 (61) Дополнительное к авт. санд-ву— (22) 3аявлено 13.04.79 (21) 2755157/18-09 (51)М. Кл 3

H L 25/40

Н 04 Ь 1/16 с присоединением заявки Йо—

Госудавствеииый комитет. СССР по делам изобретеиий и открытий (23) ПриоритетОпубликовано 28.0281. Вюллетвнь Н9 8 (53) УДК 821. .З94 (088.8) Дата опубликования описания 280231

A.Ã.ÀíäðóùåHêo, В.И.Глушков, В.Н.Бойко, В.A

В.В.Федоренко и С.В.Шпагин

/ - (72) Авторы нзобретенмя

/Ъ

1

t (71) Заявитель (54) СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДАННЫХ

С РЕШММЦЕИ ОБРАТНОЙ СВЯЗЬЮ

Изобретение относится к. связи и может использоваться, для организации: обмена информацией между двумя пунктами °

Известна система для передачи и приема данных с решающей обратной связью, содержащая на гередающей стороне последовательно соединенные датчик информации; элемент ИЛИ, накопитель и элемент И, выход которого подключен ко второму входу элемента ИЛИ, . и последовательно соединенные канал обратной связи, блок дешифрирования сигналов обратной связи и блок управ" ления, выход которого подключен ко. вторым входам накопителя и элемента

И, а.также кодирующий блок, выход которого соединен со входом дискрет-. його кайала связи; на приемной сторойе — декоднрующий блок, . первый .вход -которого соединен с выхбдом дискретного канала связи, решаюи(йй блок, выход которого подключен к первому входу блока управления, выходы которого соединены со входом блока формирования сигналов обратной связи и первыми входами накопителя и элемента:И, второй вход и выход которого соединены соответственно с выходом накопителя и входом получателя инфор- 30 мации, при этом выход блока формиро,вания сигналов обратной связи подклю.чен ко входу обратного канала связи (1) °

Однако извес тн а я с ис тема имеет сравнительно невысокую помехоустой-, чивость.

Цель изобретения — повышение ïoìåхоустойчивости.

Поставленная цель достигается тем, что на передающей стороне введен ком- паратор, входы которого соединены с выходами накопителя и датчика информации, ко входу которого подключен до- полнительный выход блока дешифрирования сигналов обратной связи, а выход компаратора соединен со вторым входом блока управления, дополньггельный выход которого подключен к третьему входу накопителя и первому входу кодирующего блока, второй вход которого соединен с выходом элемента И, на приемной стороне введены элемент

ИЛИ, ключ и компаратор, выход которого подключен ко второму входу блока управления, третий вход которого соединен с первым выходом декодирующего блока и первым входом ключа, второй вход и выход которого соединены соответственно с выходом элемен809639 та И и первым входом элемента ИЛИ, второй вход которого соединен со вторым выходом декодирующег0 блока и первым входом комнаратора, ко второму входу которого. подключен выход накопителя, вход которого соединен 5 с выходом элемента ИЛИ, причем второй вход декодирующего блока соединен с выходом рещающего блока.

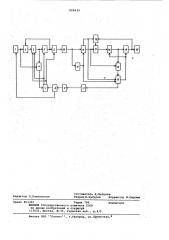

На чертеже приведена структурная электрическая схема предлагаемой сис- to темы.

Система для передачи и приема данных с решающей обратной связью содержит на передающей стороне датчик 1 информации, элемент 2 ИЛИ, накопитель

3, компаратор 4, элемент 5 И, кодирующий блок 6, блок 7 управления, блок 8 дешифрирования сигнаяов обратной связи, канал 9 обратной связи, дискретный канал 10 связи, а на приемной стороне - решающий блок ll, деко- 20 дирующий блок 12, элемент 13 ИЛИ, компаратор 14, блок 15 управления, ключ 16, блок 17 формирования сигналов обратной связи, накопитель 18 элемент 19 И и получатель 20 инфор- Я мацин.

Система работает следующим образом.

Сообщения от датчика 1 поступают на первый вход элемента 2 ИЛИ и с его выхода - на первый вход накопителя З.Сообщение, поступающее в накопитель З,сдвигает на его выход нулевую (если до этого момента информация в нем отсутствовала) информацию, которая приходит на входы компаратора 4 и элемента 5 И.

Одновременно на другой вход компаратора 4 с выхода датчика 1 поступает первое сообщение. В результате сравнения компаратор 4 вырабатывает сиг- 40 нал несовпадение, поступающий на. второй вход блока 7. Блок 7 по этому сигналу разрешает прохождение первого сообщения из накопителя 3 через эле.мент 5 И в кодирующий блок 6 и через 4 элемент 2 ИЛИ на вход накопителя 3.. для перезаписи. Кодирующий блок б преоб. разует сообщение в кодовую комбинацию, которая поступает в дискретный канал 10. С выхода дискретного канала о

10 кодовая комбинация поступает на входы декодирующего блока 12 и решающего блока 11. Решающий блок 11 вы-, рабатывает сигналы Верно илн Неверно, поступающие на первый вход блока 15 и на второй вход декодирующего блока,12.

По сигналу Неверно декодирующий блок 12 стирает принятую кодовую комбинацию, а блок 15 выдает в блок ф)

17 сигнал на формирование и выдачу. в канал 9 комбинации Запрос . Ilocледняя поступает на вход блока 8, с выхода которого сигнал Запрос поступает на вход блока 7. Блок 7 по сигналу Запрос разрешает повторное прохождение первого сообщения из накопителя 3 через соответствующие узлы системы в дискретный канал

10.

По сигналу Верно со второго выхода декодирующего блока 12 декодированное сообщение через элемент

13 ИЛИ поступает в накопитель 18 и на первый вход компаратора 14. Одновременно на первом выходе декодирующего блока 12 появляетоя сигнал, который открывает ключ 16 а также поступает на третий вход блока 15.

Если до этого момента информация в накопителе 18 отсутствует, то в результате сравнения на выходе компаратора 14 появляется сигнал Несовпадение, который поступает на второй вход блока .15. Последний разрешает по этому сигналу прохождение первого сообщения через элемент 19 И к получателю 20 и через ключ 16 и элемент 13 ИЛИ вЂ” на перезапись в накопитель 18 °

По сумме сигналов Верно и Несовпадение блоК 15 выдает в блок 17 сигнал на формирование комбинации Подтверждение, которая через канал 9 принимается блоком 8. С выхода блока 8 сигнал Подтверждение поступает в датчик 1, разрешая выдачу второго сообщения. Второе сообщение выдвигает на вход компаратора

4 первое сообщение из накопителя 3 в то время, как на другой вход компаратора 4 поступает второе сообщение непосредственно из датчика 1.

Если второе сообщение одинаковое с первым, на выходе компаратора 4, а следовательно, и на втором входе блока 7, появляется сигнал "Совпадение ", по которому на дополнительном выходе блока 7 формируется сигнал на стирание информации в накопителе 3 и формирование в кодирующем блоке б спе- . циальной кодовой комбинации х из числа размещенных. Последняя, аналогично предыдущей кодовой комбинации, через дискретный канал 10 поступает на входы решающего 11 и декодирующего 12 блоков.

Таким образом, в результате выдачи датчиком 1 подряд двух одинаковых сообщений в дискретный канал 10 не посылаются подряд две одинаковые кодовые комбинации.

Решающий блок ll и декодирующий блок 12 обрабатывает полученную кодовую комбинацию Х. Если решающий блок ll выдает сигнал Неверно, то работа системы аналогична ранее рассмотренной ее работе по сигналу Неверно . Если решающий блок 11 выдает сигнал Верно, а декодирующий блок 12 выдает сигнал о приеме комбинации Х, то на первом выходе декодирующего блока 12 возникает сигнал, соответствующий сообщению Х, 809639 по которому ключ 16 закрывается. Второй выход декодирующего блока 12 по сообщению Х остается закрытым. По сигналам Верно и Х блок 15 разрешает прохождение записанного первого сообщения иэ накопителя 18 через элемент 19 И получателю 20. Так как ключ 16 при этом закрыт, то перезапись информации в накопитель 18 не происходит. Сигнал Подтверждение

Формируется и выдается в канал 9 и 1О обрабатывается на передающей стороне так же, как и в рассмотренном выше случае.

Формула изобре,тения

Таким образом, в результате выдачи получателю 20 второго сообщенйя l5 одинакового с первым, приемная часть системы находится в том же состоянии, что и перед выдачей первого сообщения.

Если в дальнейшем датчиком 1 выдается третье сообщение, то оно обрабатывает-Щ ся так же,. как и первое, а четвертое, если оно одинаково с третьим, обрабатывается как и второе, и т.д. Любое отличное от предыдущего сообщение обрабатывается, как и первое сообщение . д

При трансформации сигнала .Подтверждение в Запрос с передающей. стороны повторно посылается ранее выданная кодовая комбинация.При этом на

-:;-ервый и второй входы компаратора 14

::оступают одинаковые сообщения и он т:сдает в блок 15 сигнал Совпадение . Из решающего блока 11 поступает сюда же сигнал Верно . По этим сигналам блок 15 выдает в блок

17 сигнал на выдачу сигнала подтверж- З5 дение.

На вторые входы накопителя 18.и элемента 19 И сигнал не подается, и сообщение в получатель 20 не поступает, 40 т.е. вставка информации исключается.

Предлагаемая система для передачи и приема данных обладает высокой эффективностью, так KIRK при ее испольэовании вероятность ошибочного приема 4 уменьшается на несколько порядков.

Система для передачи и приема данных с решающей обратной связью, содержащая на передающей стороне последовательно соединенные датчик информации, элемент ИЛИ, накопитель и эле- Ы мент И, выход которого подключен ко второму входу элемента ИЛИ, и последовательно соединенные канал обратной связи, блок дешифрирования сигналов обратной связи и блок управления, выход которого подключен ко вторым входам накопителя и элемента И, а также кодирующий блок, выход которого соединен со входом дискретного канала свяэиу на приемной стороне — декодирующий блок, первый вход которого соединен с выходом дискретного канала связи, рещающий блок, выход которого подключен к первому входу блока управления, выходы которого соединены со входом блока Формирования сигна- лов обратной связи и первыми входами накопителя и элемента И, второй вход

\ и выход которого соединены соответственно с выходом накопителя и входом получателя информации, при этом выход блока формирования сигналов обратной связи подключен ко входу обратного канала связи, о т л и ч а ющ а я с я тем, что, с целью повышения помехоустойчивости, в нее на передающей стороне введен компаратор, входы которого соединены с выходами накопителя и датчика информации, ко входу которого подключен дополнительный выход блока дешифрирования сиг« налов обратной связи, а выход компаратора соединен со вторым входом блока управления, дополнительный выход которого подключен к третьему входу накопителя и первому входу кодирующего блока, второй вход которого соединен с выходом элемента Иу на приемной стороне введены элемент ИЛИ, ключ и компаратор, выход которого подключен ко второму входу блока управления, третий вход которого соединен с первым выходом декодирующего блока и первым входом ключа, второй вход и выход которого соединены соответственно с выходом элемента И и первым входом элемента ИЛИ, второй вход которого соединен со вторый выходом декодирующего блока и первым входом компаратора, ко второму входу которого подключен выход накопителя, вход которого соединен с выходом элемента ИЛИ,причем второй вход декодирующего .блока соединен с выходом решакщего блока.

Источники информации, принятые во внимание при экспертизе

1. Пуртов Л.П. Элементы теории передачи дискретной информации, И., Связь, 1972 с .161-167, 185-191 (прототип).

809639

Составитель Е.Петрова

Техред Н.Бабурка Корректор М.Шароши

Редан тор Л. Пчелинская

Подписное

Филиал I1I111 Патент, r.Óæãîðîä, ул.Проектная,4

Эакаэ 463/82 Тираж 709.

ВНИИПИ Росударственного комитета СССР по делам изобретений и открытий:

113035, Москва, Ж-35, Раушская наб., д.4/5