Адаптивное вызывное устройство

Иллюстрации

Показать всеРеферат

СОюэ Советских

Социалкстическик

Респу6лик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

809666 (61) Дополиитсльиое к акт. скип-ву (22) Зачвлрио 27.04.79 (21 ) 2763268/18-09 (51)М, Кл.

Н 04 0 5/04 с присоединением заявки ¹

Государственный комитет

1."8) llриоритеу по делам изобретений и открытий

Опубликовано 28.02,81. Бюллетень № 8 (53) УДК 6-1.395... 63 (088.8) 1I,ата опубликования описания 28.02.81 (72) Авторы изобретения

1. И. Азаров и Ю. Н. Манякин (71) Заявитель

154) АЛА11ТИВНОЕ ВЫЗЪ|ВНОБ УГТРОЙГТВО

Изобретение относится к связи и может использоваться в аппаратуре передачи и приема избирательного вызова.

Известно адаптивное вызывное устройство, содержащее послсцоватсньио соединенные переключатель, преобразователь сигнала. 6JloK

5 синхронизации и дешифратор, последовательно соедииеиныс блок сравнения и интегратор, выход которого подключен ко входу блока индикации и к первому входу элемента И!1И, 1О а также управляющий регистр, делитель частоты и бистабильный элемент, выход которого подключен к первому входу элемента И, при этом выходы преобразователя ситнала и дешифратора подключены ко вхопам блока срав!

5 пения, выход управляющего регистра подключен к друтому входу дешифратора и ко входу переключателя, первый выход блока синхронизации подключен к первому входу пелителя частоты, первый выход которого подключен ко

20 второму входу элемента И, выход элемента И подключен ко второму входу элемента ИЛИ, а выход элемента сброса . к другому входу интегратора g I).

Онако известное устроиство имеет сравнительно невысокое быстродействие.

IIczb изобретения - повышение быстродействия.

Указанная цель достигается тем, что в известном устройстве второй выход блока синхронизации подключен к первому входу бистабильного элемента, выход элемента ИЛИ— ко второму входу делителя частоты, второй выход которого подключен ко входу управляюшсго регистра, третий выход делителя частоты чсрез элемент сброса подключен ко второму входу бистабильного элемента, а другой выход интегратора - к третьему входу Пснитсня частоты.

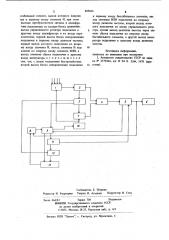

На чертеже приведена структурная электрическая схема предлагаемого устройства.

Адаптивное вызывкос устройст во содержи г псрсключатель I, преобразователь 2 сигнала. блок 3 сиихронизации, блок 4 сравнения. интегратор 5, блок 6 индикации, лсшифратор 7, элемент ИЛИ 8, делитель ч часгогы. управлявший регистр 10, элемент 11 сбр со, бисгзбильиый элемент 1 и элсмснг II 1.1.

809666

Зо

Формула изобретения

55

Устройство работает следующим образом.

Информационные последовательности всех каналов многоканальной системы связи, вызывные сигналы в которой представлены в виде кодовых последовательностей двух тональных частот, с помощью переключателя 1 поочередно подключается ко входу преобразователя 2, формирующего в соответствии с поступающей информацией определенные импульсные последовательности. Сформированные импульсные последовательности поступают на один из двух входов блока 4 и на вход блока

З,который вырабатывает тактовые импульсы для дешифратора 7 и исходные импульсы для делителя 9.

Управление работой переключателя-1 и смена кодовых последовательностей, занисанщах s дешифраторе 7 (каждому каншу соответствует своя кодовая последовательность), обеспечивается с помощью управляющего регистра 10, тактовые импульсы дня которого формируются с помощью делителя 9.

В устройстве римеияется синхронный способ обработки сигналов. При этом используется метод фазирования по рабочим импульсам, заключающийся в том, что блок 3 выделяет из всего потока информации моменты смены полярности рабочих импульсов и формирует в указанные моменты времени импульсы синхронизации. Эти импульсы обеспечивают подстройку фазы тактовых ймпульсов дешифратора 7. Кроме того, импульсы синхронизации поступают на вход бистабильного элемента 12 и переводят erо в другое состояние. Так как формирование импульсов синхронизации про- . исходит только в моменты смены полярности рабочих импульсов, то при наличии в анализируемом канале помех (шумовых или посторонних) и отсутствии вызывных сигналов импульсы синхронизации с выхода блока 3 не поступают, и бистабильный элемент 12 находится в одном и том же устойчивом состоянии (исключение составляют только помехи, структура которых конгруэнтиа структуре вызывных сигналов, однако вероятность появления таких помех по сравнению с шумовыми достаточно мала) .

Напряжение бистабильного элемента 12, состояние которого в данном случае определяется отсутствием импульсов синхронизации, прикладывается к первому входу элемента И 13, на второй вход которого поступают импульсы с первого выхода делителя 9. Поступление их производится через промежутки времени

t=(nfl) t где n - максимальное количество

О следующих подряд импульсов одной полярности в вызывных командах устройства; то - длительность одного импульса.

При наличии напряжения на обоих входах элемента И 13 послелций срабатывает и через элемент ИЛИ 8 сбрасывает делитель 9 (а также интегратор 5 через элемент 11) в исходное состояние. При этом устройство подключается к следующему каналу.

Если за время t=(nfl) t о поступает хоть один импульс синхронизации, переводящий бнстабильный элемент 12 в другое состояние, то элемент И 13 не срабатывает, и анализ данного канала продолжается. При этом блок 4 производит сравнение принимаемой кодовой последовательности с кодовой последовательпостыл, поступающей с выхода дешифратора

7. Сравнение кодовых последовательностей производится поимпульсно. Совпадение каждой пары импульсов фиксируется в интеграторе

5, который обеспечивает предварительное и полное интегрирование.

Если в результате предварительного интегрирования адресного признака, присущего анализируемому каналу, в поступающих сигналах не обнаружено (т.е. с выхода блока 4 импульсы совпадения в интегратор 5 не поступают), то с другого выхода интегратора 5 на третий вход делителя 9 поступает сигнал, устанавливающий делитель 9 в нулевое состояние.

Сброс интегратора 5 в этом случае обеспечивается с помощью элемента 11.

Если результаты предварительного интегрирования положительны, то анализ данного канала продолжается. По истечении времени полного интегрирования сигнал с выхода интегратора 5 поступает в блок 6и через элемент

ИЛИ 8 сбрасывает делитель 9 в исходное состояние, Сброс интегратора 5 производится аналогично ранее рассмотренным случаям.

Если результаты предварительного интегрирования положительны, а полное интегрирование вследствие каких-либо причин (обусловленных, например, воздействием помех) не произошло, то перевод устройства к анализу следующего канала осуществляется принудительно по истечении времени, обусловленного частотой тактовых импульсов, формируемых делителем 9.

Таким образом, предлагаемое устройство обеспечивает высокое быстродействие.

Адаптивное вызывное устройство, содержащее последовательно соединенные переключатель, преобразователь сигнала, блок синхронизации и дешифратор, последовательно соединенные блок сравнения и интегратор, выход которого подключен ко входу блока индикаш1и и к первому входу элемента ИЛИ, а также управляющий регистр, делитель частоты н би809666

Составитель Е, Петрова

Редактор Н. Везродная Техред И. Асталош Корректор Н. Стец

Заказ 464/82 Тираж 709 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 стабильный элемент, выход которого подключен к первому входу элемента И, при этом выходы преобразователя сигнала и дешифратора подключены ко входам блока сравнения, выход управляюгцего регистра подключен к другому входу дешифратора и ко входу пере, ключателя, первый выход блока синхронизации подключен к. первому входу делителя частоты, первый выход которого подключен ко второму входу элемента И, выход элемента И подключен ко второму входу элемента ИЛИ, а выход элемента сброса подключен к другому входу интегратора, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, второй выход блока синхронизации подключен к первому входу бистабильного элемента, выход элемента ИЛИ подключен ко второму входу делителя частоты, второй выход которого подключен ко входу управляющего регистра, третий выход делителя частоты через элемент сброса подключен ко второму входу бистабильного элемента, а другой выход интегратора подключен к третьему входу делителя частоты. о

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР по заявке У 2579244, кл. Н 04 0 3/04, 1978 (про-

$ 5 тотип) .