Контролируемый сумматор

Иллюстрации

Показать всеРеферат

О П И С А Н И Е II! SII26I

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 12.07.78 (21) 2644536/18-24 с присоединением заявки ¹ (23) Приоритет (43) Опубликовано 07.03.81. Бюллетень № 9 (45) Дата опубликования описания 07.03.81 (51) М. Кл. б 06 F 11/00

G 06 F 7/50

Государствеииый комитет

СССР по делам изобрегеиий и открытий (53) УДК 681.325 (088.8) е

В. И. Корнейчук, В. К. Моллов, В. П. Тарасенко;-Я. И. Торошанко и В. Х. Цоне@

Киевский ордена Ленина политехнический институт им. 50-летия Великой Октябрьской социалистиАеской. революции (72) Авторы изобретения (71) Заявитель (54) КОНТРОЛИРУЕМЫЙ СУММАТОР

Изобретение относится к вычислительной технике и может быть использовано при построении ЦВМ повышенной надежности.

Известен сумматор с контролем ошибок, каждый разряд которого содержит одно- 5 разрядный сумматор, а его входы и выходы через эмиттерный повторитель подключены к схеме неравнозначности, второй вход которой соединен с шиной опорного напряжения (1). Выходы схемы неравнозначности IO всех разрядов соединены через многовходовый элемент ИЛИ с шиной ошибки. В таком сумматоре обнаружение ошибок основывается на закономерности, заключающейся в том, что при правильной работе 15 арифметическая сумма инверсных входных сигналов одноразрядного сумматора и сигнала суммы, взятого с единичным весом, и сигнала переноса в следующий разряд, взятого весом 2, всегда равна 3. При непра- 20 вильной работе сумматора это соотношение нарушается, что определяется схемой неравнозначности.

В качестве прототипа выбран контролируемый сумматор, каждый разряд которого 25 содержит два полусумматора для формирования суммы по модулю 2 и переносов, элемент ИЛИ, объединяющий выходы переносов полусумматоров, в совокупности оба полусумматора и элемент ИЛИ обра- 30 зуют одноразрядный сумматор, элементы И

НЕ и два пороговых элемента, подключенHbIx к прямым и инверсным входам и выходам полусумматоров и элемента ИЛИ.

Входы полусумматоров всех разрядов подключены через многовходовой элемент

ИЛИ к шине ошибки сумматора (2).

При правильной работе сумма входов каждого порогового элемента равна определенному числу, называемому порогом.

При неправильной работе сумма входов одного из пороговых элементов превышает порог и на его выходе появляется сигнал ошибки.

Однако недостатком такого сумматора являются значительные аппаратурные затраты, а также невысокое быстродействие, так как схемы контроля в нем выполнены с использованием многоуровневой логики.

Целью изобретения являются уменьшение аппаратурных затрат и повышение быстродействия контролируемого сумматора.

Достигается это тем, что контролируемый сумматор, каждый разряд которого содержит одноразрядный сумматор и два пороговых элемента, причем выходы пороговых элементов всех разрядов контролируемого сумматора соединены с входамп элемента

ИЛИ, вход переноса однора" ðÿäíîãî сумматора каждого разряда контролируемого

811261

)0

i) мматора соединен с выходом аере»иоа предыдущего разряда контролируемого сумматора и с входом первого порогового элемента, имеющим вес + 1, два других входа первого порогового элемента, имеющего вес + 1, соединены с входами соответствующих разрядов операндов, выход суммы одноразрядного сумматора каждого разряда контролируемого сумматора соединен с входом второго порогового элемента соответствующего разряда, имеющим +1, выход переноса одноразрядного сумматора каждого разряда контролируемого сумматора соединен с выходом переноса из данного разряда, пороговые элементы имеют порог срабатывания + 1, причем в каждом разряде контролируемого сумматора вход первого порогового элемента, имеющий вход с весом — 1, соединен с выходом суммы соответствующего одноразрядного сумматора, выход переноса которого соединен с входом первого порогового элемента, имеющим вес — 2, и с входом второго порогового элемента, имеющим вес +2, три входа второго порогового элемента, имеющие вес — 1, соединены соответственно с выходом переноса предыдущего разряда контролируемого сумматора и с входами соответствующих разрядов операндов.

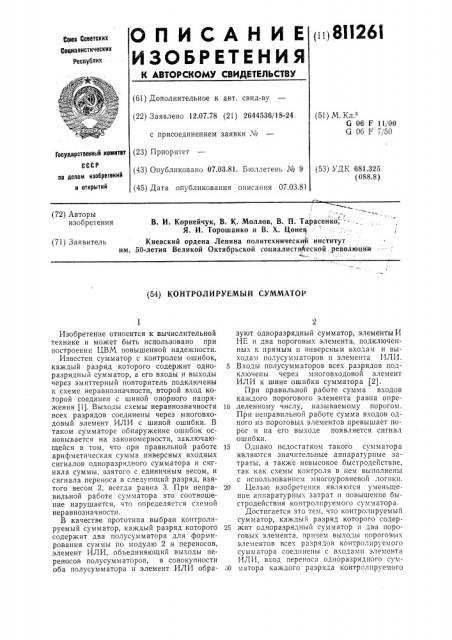

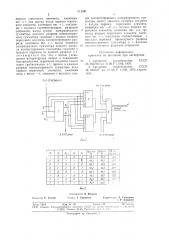

1-1а фиг, 1 изооражена функциональная схема L-го разряда сумматора (i= l, ..., и, где и — разрядность суммируемых чисел); на фиг. 2 — таблица работы схемы контроля сумматора.

Каждый i-и разряд сумматора содержит одноразрядный сумматор l, порого)зые элементы 2 и 3. Веса входов порогового элемента 2 равны +1, +1, +1, — 1, — 2, причем входы его с весом +1 соединены с входами операндов а, и b; переноса Р„ i-ro разряда, вход с весом — 1 подключен к выходу су.ммы S,, а вход с весом — 2 — к выходу переноса Р; одноразрядного сумматора 1 i-го разряда. Веса входов порогового элемента 3 равны — 1, — 1, — 1, +1, +2, причем входы его с весом — 1 соединены с входами операндов а, и b; и переноса

Р;, i-го разряда, вход с весом +1 подключен к выходу суммы S;, а вход с весом

+2 — к выходу переноса Р, одноразрядпогo сумматора 1 i-ro разряда.

Выходы пороговых элементов 2 и 3 всех разрядов соединены с входами м ноговходового элемента ИЛИ 4, выход которого является контрольным выходом сумматора.

Устройство работает следующим образом.

Входы пороговых элементов 2 и 3 подключены таким образом, что при появлении ошибки на выходах одноразрядных сумматоров 1 S,, Р; или на обоих выходах одновременно сумма входных сигналов одного пз пороговых элементов 2 и 3 превышает его порог, в результате чего на выходе этого порогового элемента появится едишгчный сигнал, вызывающий сигнал ошибки на выходе мпоговходового элемента ИЛИ 4.

В приведенной таблице на фиг. 2 указаны все возможные ошибки сумматора и соответствующий пороговый элемент, обнаруживающий конкретную ошибку.

1!рп ло кном появлении кода «О» вместо

«1» срабатывает пороговый элемент 2, а при ложном появлении кода «1» вместо

«О» — пороговый элемент 3.

Для примера рассмотрим работу сумматора на входном наборе ai = l, bi =0, Р;+1 — — 1. !!рп правильной работе на шине S, будет сигнал, соответствующий «О», а на шине

Р, — «1». При появлении на выходе S; сигнала «1» сумма входных кодов, подаваемых на пороговый элемент 3, равна 1, что превышает его порог срабатывания, и на выходе порогового элемента 3 появится сигнал ошибки. Если на шине Р, появится сигнал «О» вместо «!», срабатывает пороговый элемент 2.

При двойной ошибке сумматора, т. е. появлении «1» на выходе S, и «О» — на выходе Р;, срабатывает пороговый элемент 2.

Из таблицы видно, что в сумматоре обнаруживаются все единичные и двойные ошибки.

Число логических уровней, через которые проходит сигнал от входа к выходу в схеме данного сумматора, равно 2, а число логических уровней известного сумматора равно 3. Таким образом, быстродействие данного сумматора выше по сравнению с известным.

B данном сумматоре по сравнению с известным сумматором уменьшается также количество оборудования, так как известный сумматор содержит в цепи контроля одного разряда два пороговых элемента, три элемента НЕ и элемент И.

Для контроля одного разряда данного сумматора необходимы только два пятивходовых пороговых элемента.

Следует заметить также, что аппаратурпые затраты па реализацию пятивходового порогового элемента меньше по сравнению с семивходовыми и восьмпвходовыми пороговыми элеме с порогами 5 и 4.

Формула изобретения

Контролируемый сумматор, каждый разряд которого содержит одноразрядный сумматор и два пороговых элемента, причем выходы пороговых элементов всех разрядов контролируемого сумматора соединены с входами элемента ИЛИ, вход переноса одноразрядного сумматора каждого разряда контролируемого сумматора соединен с выходом переноса предыдущего разряда контролируемого с! мматора и с входом ((1! 261 йа l-. а,ала

А // l/,ааааа. ;;; r,-га,аале, и

g/

Фиг, с

Составитель В. Берукин

Текрсд T. Трушкина

Корректоры: A. Степанова и Р. Беркович

Редактор Е. Гончар

Заказ 750/4 Изд. ¹ 187 Тираж 740 Подписное

НПО «Поиск» Государственного комитета СССР по ислам llçîÁ. с-.сии,"i u oTi ы гий

113035, Москва, Я-35, Раушская иа5., и. 4 5

Типография, пр. Сапунова, о первого порогового элемента, имеющим вес +1, два других входа первого порогового элемента, имеющего вес +1, соединены с входами соответствующих разрядов операндов, выход суммы одноразрядного сумматора каждого разряда контролируемого сумматора соединен с входом второго порогового элемента соответствующего разряда, имеющим вес +1, выход переноса одноразрядного сумматора каждого разряда контролируемого сумматора соединен с выходом переноса из данного разряда, отл ичающи йся тем, что, с целью уменьшения аппаратурных затрат и повышения быстродействия, пороговые элементы имеют порог срабатывания +1, причем в каждом разряде контролируемого сумматора вход первого порогового элемента, имеющий вход с весом — 1, соединен с выходом суммы соответствующего одноразрядного сумматора, выход переноса которого соединен с входом первого горогового элемента, имеющим вес — 2, и с входом второго порогового элемента, имеющим вес +2, три входа второго порогового элемента, имеющие вес — 1, соединены соответственно с вы:;одом переноса предыдущего разряда контролируемого сумматора и с входами

10 соответствующих разрядов операндов.

Источники информации, принятые во вш1мание при экспертизе

15 1. Лвторское свидетельство СССР

¹ 365708, кл. G 06 Г 11/02, 1970.

2. Авторское свидетельство СССР № 500527, кл. G 06 F 11/00, 1973 (прототип).