Устройство для решения систем ли-нейных алгебраических уравнений

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

Оп NCAHNE

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (u)811275 (61) Дополнительное к авт. свид-ву (22) Заявлено 18. 09. 78 (21) 26652 32/18-24 (51)М. Кл с присоединением заявки ¹ .(23) Приоритет

G 06 F 15/324

Государственный комитет

СССР ио делам изобретений и открытий

Опубликовано 070381, Бюллетень 89 9

Дата опубликования описания 07. О 3. 81 (53) УДК 681.325.5

{088.8) Л. И. Сулин, К. П. Бочаров и B. В. Ходыр в (72) Авторы изобретения па

1

9 (71) Заявитель (54) УСТРОЙСТВО ДЛЯ РЕШЕНИЯ СИСТЕМ ЛИНЕЙНЫХ

АЛГЕБРАИЧЕСКИХ УРАВНЕНИЯ

Изобретение относится к вычислительной технике и может быть исполь-, зовано при разработке специализированных вычислительных машин и процессоров для решения систем линейных алгебраических уравнений.

Известно устройство для решения систем линейных алгебраических уравнений f1) содержащее интеграторы коэффициентов, интегратор свободного члена и интеграторы неизвестных, причем выходы интеграторов коэффициентов каждого столбца соединены-со входами интеграторов свободного члена того же столбца, выходы которых подключе- 15 ны ко входам интеграторов неизвестных того же столбца и ко входам интЕграторов коэффициентов соответствующих строк.

Недостатком этого устройства яв- 20 ляется большое количество используемого оборудования, а также запаздывание в обработке приращений и трудность решения систем уравнений высоких порядков, а также сравнительно малое быстродействие.

Известно также устройство для решения систем алгебраических уравнений {21, содержащее несколько групп регистров памяти коэффицен- 30 тов, к выходам которых подключены первые входы соответствующих блоков умножения кода коэффицентов на знак приращения переменной, регистры накопления величин невязок, выходы которых подсоединены к соответствующим входам блока уравновешивания, и цифровые интеграторы накопления переменных,входы каждого из которых соединены со. вторыми входами блоков умножения соответствующей группы и с соответствукщими выходами блока уравновешивания.

Недостатком этого устройства является большой объем требуемого оборудования даже для систем уравне.— ний невысокого порядка, причем сложность устройства увеличивается по мере увеличения порядка решаемой системы.

Из известных устройств наиболее близким по технической сущности к изобретению является устройство для решения систем линейных алгебраических уравнений 31, содержащее одноразрядные сумматоры-вычитатели, сдвиговые регистры,.реверсивные счетчики, блоки анализа, элементы

И, ИЛИ. Управляющие вхады сдвиго811275 вых регистров соединены с управляющей шиной, а выходы — с первыми входами соответствующих одноразрядных сумматоров-вычитателей, объединенных в п столбцов по (h +1) последовательно соединенных одноразрядных сумматоров-вычитателей в каждом. Управляющие входы одноразрядных сумматоров-вычитателей каждой строки соединены со входами соответствующего реверсивного советчика, выход 9 -го одноразрядного сумматоравычитателя каждого столбца соединен с первым входом (П +1) -го одноразрядного сумматора-вычитателя и с первым входом элемента ИЛИ, выход кото" рого соединен со входом (и +1) -го l5 сдвигового регистра. Выход знакового разряда (п +1) -ro сдвигового регистра соединен с входом соответствующего реверсивного счетчика. Выход(п+1) -го сдвигового регистр.. соединен со вто- Щ рым входом блока анализа и через первый элемент И вЂ” со вторым входом элемента ИЛИ и со вторым входом перого одноразрядного сумматора-вычитЬтеля соответствующего столбца, а через второй элемент И вЂ” со вторым входом (и +1) -го одноразрядного сумматора-вычитателя, выход которого соединен с третьим входом блока анализа.

Вторые входы элементов И всех столбцов и управляющие входы реверсивных счетчиков соединены с управляющей шйной.

Недостатком этого устройства также является большой объем оборудования.

Целью изобретения является упрощение устройства.

Поставленная цель достигается тем, что устройство, содержащее блок памяти коэффициентов и свободных членов, адресный вход которого 40 соединен с выходом счетчика адреса, регистры сдвига, элементы И, сумматор-накопитель, содержит сумматор единиц и коммутатор, первый вход кото-рого соединен с выходом счетчика 45 адреса. Первый вход каждого элемента

И соединен с соответствукщим выходом блока памяти коэффициентов и свободных членов, один из выходов которого подключен к первому входу сумматора-накопителя, второй вход которого соединен с выходом сумматора единиц, входы которого соединены соответсственно с.выходами элементов И. Выход каждого регистра сдвига соединен со своим первым входом и с вторым входом соответствующего элемента И.

Второй вход каждого регистра сдвига соединен с соответствующим выходом коммутатора, второй вход которого подключен к выходу сумматора-накопи- фG теля. Выход счетчика адреса является. входом устройства.

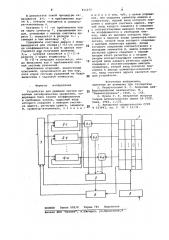

Схема устройства представлена на чертеже, где обозначены блок 1 памяти коэффициентов и свободных членов, счетчик 2 адреса, регистры сдвига

31 — 3п, элементы И 4 — 4„ сумматор единиц 5, сумматор-накопи— тель б н коммутатор 7.

Устройство работает следующим образом.

Для решения уравнения системы первоначально преобразуются к виду

И х,=б„ а;> х,, 1,2..., и

1=1 и коэффициенты системы di è свободные члены 4э записываются в блок

1 памяти

Начальные приближения корней заносятся в регистры 3 сдвига, Каждое(К +1) -е приближение корней вычисляется по следующей формуле: (К+1) -i (КФ1) " (К)

=6 е a;> х 1.> ai) х

j1 1 1

kent

Приближение в каждой ите-рации вычисляется за п1 циклов, в каждом из которых выполняется п1 так тов.

В каждом цикле выполняются следующие действия. В первом цикле, первом такте из блока 1 считываются младшие разряды всех коэффициентов О, (1 = 1,2, ..., Р) и логически умножаются на элементах

И 41 — 4П на младшие разряды чисел (приближений корней), находящихся в регистрах 3. Образованная на выходе сумматора единиц 5 сумма произведений младших разрядов всех коэффициентов на младшие разряды всех приближений корней складывается с содержимым сумматора-накопителя 6 и младшим разрядом свободного члена б, . В сумматоре-накопителе б делается сдвиг на один разряд в сторону старших разрядов. К счетчику

2 добавляется единица в младший разряд, что вызывает модификацию адреса. В первом цикле, втором такте повторяется процедура, аналогичная описанной в первом такте для следующих разрядов коэффициентов за исключением того, что во втором и последующих тактах цикла очередной разряд Ь, к сумме не добавляется.

В первом цикле такие такты повторяются rn раз.

Второй цикл начинается со сдвига содержимого сумматора-накопителя на (tn -1) разряд в сторону младших разрядов и циклического сдвига содер. жимого всех регистров 3 на один разряд в сторону младших разрядов. Таким образом, ко входам элементов И подключены очередные разряды приближений неизвестных, хранящихся в регистрах 3. Далее цикл вычислений выполняется, как и предыдущий.

Число циклов вычислений, которое требуется выполнить, равно N (по числу разрядов кодов чисел, хранимых э регистрах сдэига 3).

811275

Формула изобретения

ВНИИПИ Заказ 503/2 Тираж 745 Подписное

Филиал ППП "Патент", r.Óæãîðoä, ул.Проектная,4

В результате такой процедуры на-! числяется К+1 — е приближение корня >i которое находится в сумматоре-накопителе 6.

Значение К +1 -го приближения корня через сумматор 7, управляемым ко-, дом, снимаемым с выхода счетчика адреса 2, передается в регистр 3- замещая в нем величину Х

Содержимое счетчика адреса 2 моди-фицируется для чтения (j +1) -го столбца коэффициентов и все е циклов повторяются для получения величины которая заносится в (+1) -A регистр 3 через коммутатор 7. (К +1) -я итерация закончится, когда вычислены все и приближений корней сиСтемы уравнений.

Выполнение итераций, аналогичных описанной, продолжается до тех пор, пока корни системы уравнений не будут вычислены с заданной точностью.

Устройство для решения систем линейных алгебраических уравнений, содержащее блок памяти коэффициентов и свободных членов, адресный вход которого соединен с выходом счетчика адреса, регистры сдвига, элементы

И, сумматор-накопитель, о т л и ч а ю щ е е с я тем, что, с целью упрощения, оно соцержит сумматор единиц и коммутатор, первый вход которого соединен с выходом счетчика адреса, первый вход каждого элемента И соединен с соответствующим выходом блока памяти коэффициентов и свободных членов, один иэ выходов которого подключен к первому входу сумматора-накопителя, второй вход которого соединен с выходом сумматора единиц, входы которого соединены соответственно с выходами элементов И, выход каждого . регистра сдвига соединен с пЕрвым входом этого регистра и с вторым входом соответствующего элемента И, 15 второй вход каждого регистра сдвига соединен с соответствующим выходом сумматора, второй вход которого подключен к выходу сумматора-накопителя, вход счетчика адреса является входом устройства.

Источники информации„ принятые во внимание при экспертизе

1. Неслуховский К. С. Цифровые дифференциальные анализаторы, M.

"Машиностроение", 1968, с. 148.

2. Пухов Г. К. Избранные вопросы теории математических машин АН УССР, Киев, 1964, с.172.

3. Авторское свидетельство СССР

Р 543943, кл. G 06 F 15/32.