Устройство для интегрированияэлектрического сигнала

Иллюстрации

Показать всеРеферат

(ii) SI I 279

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

И АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ноаз советских социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 13.11.78 (21) 2682791/18-24 с присоединением заявки № (23) Приоритет (43) Опубликовано 07,03.81. Бюллетень № 9 (45) Дата опубликования описания 07.03.81 (51) М. Кл

6 06 6 7/18

Государственный комитет (53) УДК 681.335 (088.8) по делам изобретений н открытий (72) Авторы изобретения (71) Заявитель

А. И. Самойлов и А. H. Чечулина

Уральский электромеханический институт ин енеров железнодорожного транспорта (54) УСТРОЙСТВО ДЛЯ ИНТЕГРИРОВАНИЯ

ЭЛЕКТРИЧЕСКОГО СИГНАЛА ра (2).

Изобретение относится к вычислительной технике и может быть использовано для подсчета в реальном масштабе времени определенного интеграла с точно заданными пределами. интегрирования электрических сигналов при обработке и анализе сигналов.

Известны устройства для интегрирования, состоящие из операционного усилителя, конденсатора, включенного между его инвертирующим входом и выходом, резистора, включенного между входом интегратора и инвертирующим входом усилителя (1).

Погрешностью устройства являются необходимость введения компенсаторов дрейфа нуля и введения специальных элементов для задания начальных условий интегрирования, а также то, что они требуют время для установки начальных условий; кроме того, известные интеграторы не позволяют произвольно выбирать пределы интегрирования.

Известны также интегрирующие устройства, содержащие ряд последовательно включенных блоков задержки, выход каждого из которых через соответствующий весовой элемент соединен с входом сумматоОднако это устройство не позволяет раздельно получать значения интегралов разных типов.

Наиболее близким по технической сущ5 ности к изобретению является устройство, содержащее источник сигнала, блоки задержки, блоки регулирования амплитуды и сумматор (3). Это устройство предназначено для решения задачи выделения совокуп10 ности гармоник периодических несинусоидальных сигналов, а при соответствующем выборе времени задержки блоков задержки и соответствующем выборе коэффициентов передачи блоков регулирования может быть

15 использовано для подсчета определенного интеграл а.

Недостаток этого устройства состоит в невозможности раздельно получать на выходе устройства в текущем времени значения интегралов разных типов.

Цель изобретения состоит в расширении функциональных возможностей устройства для интегрирования, т. е. получение в реальном масштабе времени неопределенного интеграла с переменным верхним или нижним пределом, определенного интеграла с точно заданным интервалом интегрирования, определенного интеграла данного сиг3р нала с любой заданной весовой функциеи, 811279

3,остигается это тем, что в устройство для интегрирования электрического сигнала, содержащее блок задержки, вход которого соединен с источником сигнала, а выходы через блок весовых резисторов подключены к входам сумматора, введены блок формирования управляющих импульсов и трехпозиционный переключатель, сигнальный вход которого подключен к выходу сумматора, управляющие входы соединены с выходами блока формирования управляЮЩИХ IIIIII I>, 1ЬСО!1, <1 ??1>!ХОДЫ ЯВЛЯК)ТС11 Hl>Iодами устройства, причем вход блока формирования управляющих импульсов соединен с источником сигнала, а трехпозиционный переключатель содержит триггер, дифференцирующую цепь, формирователь прямоугольных импульсов и три ключа, входы и выходы которых являются соответственно сигнальным входом и выходами трехпозиционного переключателя, управляющий вход первого ключа подключен к первому выходу триггера, соединенному через последовательно включенные дифференцирующую цепь и формирователь прямоугольных импульсов с управляющим входом второго ключа, управляющий вход третьего ключа подключен к второму выходу триггера, входы которого являются управляющими входами трехпозиционного переключателя.

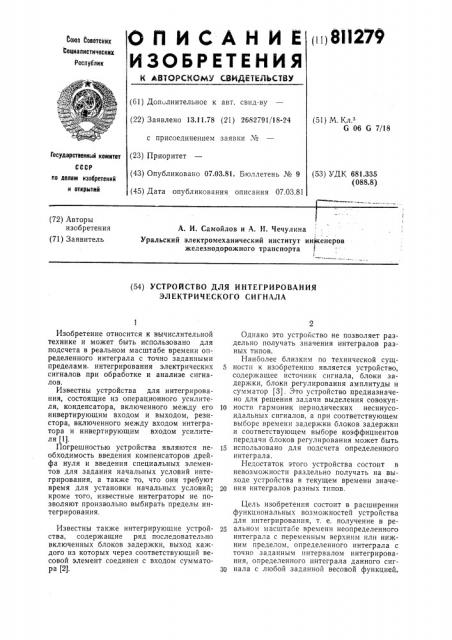

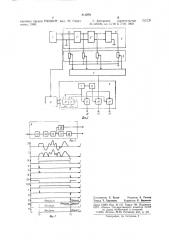

На фиг. 1 дана схема устройства для интегрирования электрического сигнала; на фиг. 2 — пример выполнения блока формирования управляющих импульсов; на фиг, 3 — временные диаграммы, поясняющие работу устройства.

Устройство содержит последовательно соединенные источник сигнала 1, блок задержки 2, осуществляющие дискретизацию сигнала во времени и состоящие из линии задержки с отводами через At, блок весовых резисторов 3, задающий метод численного интегрирования и выполненный в виде взвешивающих потенциометров, сумматор

4 и трехпозиционный электронный переключатель 5, один вход которого подключен к выходу сумматора 4, а вторые входы соединены с выходами схемы формирования управляющих импульсов 6, вход которой связан с выходом источника сигнала.

Блок задержки 2 имеет общее время задержки Т, равное длительности интервала интегрирования. Через интервалы задержки At сделаны отводы, к которым подключены потенциометры взвешивающего блока

3. С помощью потенциометров устанавливаются весовые коэффициенты.

Блок задержки может быть выполнен из звеньев 1.С или RC, может быть ультразвуковой или на магнитной ленте, но он должен быть линейным.

Входной интегрируемый сигнал U„,. (t), имеющий длительность Т от источника сигнала 1 поступает на вход блока задержки

1О

4

2. По мере продви>кения сигнала а отводах О, 1, 2, ... Л" будут действовать напряжения, равные мгновенным значениям сигнала U,,(ïAt), взятым через интервалы

At.

На сумматор 4 поступа1от мгновенные значения сигнала с отводов линии задержки в данный момент времени с некоторыми коэффициентами. Суммирование значений сигнала в момент 1= T по всем отводам даст после умножения íà At Опрсде,icirrriiii

1!1псгра,1, !!Оде IIITaIIIII, II(I методу прямО 1>ГО,! I,пикон ссл11 пссоныс коэфф!1!1пс1!Ть! равны 1.

При подаче сигнала iia блок задержки на выходе устройства имеем значения, соответственно равные неопределенному интегралу с переменным верхним пределом (выход 1)

U,„„(t) = ) U,„„(t — l) dl, при 0

U,„, (T) = J U„. (Т вЂ” l) dl, и ри t = Т; о неопределенному интегралу с переменным нижним пределом (выход 3) т

U,„„(t) = s U,„(t — l)dl при Т <2Т. — т

Следовательно, интересующее нас значение определенного интеграла будет на выходе сумматора 4 в момент t= Т. В этот момент импульсом с блока формирования управляющих импульсов 6 кратковременно переключатель 5 подключает выход сумматора к выходу 2 устройства.

До момента t=T интегратор выдает на выходе 1 неопределенный интеграл данного сигнала, а после момента t=T интегратор выдает на выходе 3 неопределенный интеграл данного сигнала с переменным нижним пределом.

Управляющий сигнал с блока формирования управляющих импульсов в виде биполярных прямоугольных импульсов длительностью 2Т должен управлять переключателем 5, подключая выход сумматора к выходу 1 устройства при t

Реальная схема с конечным числом отводов вместо интегралов выдает интегральную сумму.

При использовании формулы прямоугольников на сумматор нужно подавать значения сигналов с отводов О, 1, 2, ...,V — 1 или с отводов 1, 2, 3, ... М с весовыми коэффициентами «1». Для этого соответствующие движки потенциометров блока 3 должны быть выведены в верхнее положение, 8!1279

При использовании формулы трапеций на сумматор нужно подавать значения сигнала с 0 по N отводов, причем весовые коэффициенты нулевого и последнего отводов необходимо уменьшить в 2 раза. Для этого движки нулевого и последнего потенциометров блока 3 устанавливаются посередине.

При использовании формулы Симпсона (параболических трапеций) движки нулевого и последнего потенцио метр о в блока

3 нужно установить на /4 полного сопротивления, движки всех четных потенциометров — посередине, а всех нечетных полностью вывести вверх.

Устройство может подсчитывать определенный интеграл данного сигнала с любой заданой весовой функцией. Эта функция должна быть замоделирована в блоке 3.

Точность подсчета интеграла в данном устройстве определяется выбором интервала дискретизации At и может беспредельно увеличиваться путем уменьшения At.

Для учета этого множителя и других коэффициентов, входящих в формулы, в сумматоре предполагается соответствующий аттенюатор.

Трехпозиционный электронный переключатель 5 содержит дифференцирующую цепь 7, формирователь прямоугольных импульсов 8, три ключа 9, 10, 11, соединенные с выходами триггера 12 непосредственно, ключи 9 и 11, а ключ 10 соединен с выходом триггера 12 через дифференцирующую цепь 7 и формирователь прямоугольных импульсов 8.

В синхронных системах, когда точно известны начало и конец сигнала (они отмечаются синхроимпульсами), управляющие импульсы могут быть сформированы стандартными блоками — триггером и дифференцирующим устройством.

В несинхронных системах, когда начало и конец сигнала заранее известны, а сигналы являются однополярными или двухполярными без разрывов на оси времени (каковыми являются большинство практически встречающихся сигналов), управляющие импульсы можно сформировать с помощью блока, показанного на фиг. 2.

Блок формирования управляющих импульсов состоит из последовательно соединенных блоков определения модуля сигнала 13 и сигнатуры модуля 14, дифференцирующего устройства 15, коммутирующих диодов 16 и 17 и инвертора 18. В результате на выходе блока 6 формируются остроконечные импульсы начала и конца сигнала.

На фиг. 3 представлены временные диаграммы, поясняющие работу блоков 5 и 12.

Из диаграмм следует, что от момента t, до схема выдает неопределенный интеграл с переменным верхним пределом на открытый выход 19, в момент tz — определенный

65 интеграл на открытый выход 20, от момента tz до (2t> t) — неопределенный интеграл с переменным нижним пределом на открытый выход 21.

11рименение предложенного устройства позволяет существенно расширить функциональные возможности интегратора: позволяет подсчитывать в реальном масштабе времени неопределенные интегралы с переменными верхними и нижними пределами, подсчитывать определенный интеграл с точно заданным интервалом интегрирования, подсчитывать определенный интеграл данного сигнала с любой заданной весовой функцией; кроме того, применение предложенного устройства позволяет существенно упростить устройство для интегрирования и повысить точность интегрирования за счет имеющейся возможности использования более точных методов численного интегрирования и уменьшения шага дискретизации.

Формула изобретения

1. Устройство для интегрирования электрического сигнала, содержащее блок задержки, вход которого соединен с источником сигнала, а выходы через блок весовых резисторов подключены к входам сумматора, о т л и ч а ю щ е е с я тем, что, с целью расширения класса решаемых задач за счет получения как определенного, так и неопределенного интегралов, в него введен блок формирования управляющих импульсов и трех позиционный переключатель, сигнальныйй вход которого подключен к выходу сумматора, управляющие входы соединены с выходами блока формирования управляющих импульсов, а выходы являются выходами устройства, причем вход блока формирования управляющих импульсов соединен с источником сигнала.

2. Устройство по п. 1, отл и ч а ющееся тем, что трехпозиционный переключатель содержит триггер, дифференцирующую цепь, формирователь прямоугольных импульсов и три ключа, входы и выходы которых являются соответственно сигнальным входом и выходамп трехпозиционного переключателя, управляющий вход первого ключа подключен к первому выходу триггера, соединенному через последовательно включенные дпфференцирующую цепь и формирователь прямоугольных импульсов с управляющим входом второго ключа, управляющий вход третьего ключа подключен к второму выходу триггера, входы которого являются управляющими входам п трех позиционного переключателя.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 488222, кл. G 06 G 7/18, 1976.

2. Самойлов Л. И. Оптимальный фильтр для сигналов произвольной формы, сборник

811279 и Р/

22

7 научных трудов УЭМИИТ, выи. 20, Сверлловск, 1968.

8 3. Авторское свидетельство СССР № 326584, кл. G 06 G 7/18, 1969.

Составитель С. Белан Редактор Е. Гончар

Техред Т. Трушкина Корректор P. Беркович

Заказ 1349/1 Изд. № 187 Тираж 784 Подписное

НПО «Поиск» Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2