Устройство для измерения центральнойчастоты спектра сигнала

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Респубднк

<л813290

К АВТОРСКОМУ СВИДЕТВЛЬСТВУ (61) Дополнительное к авт. саид-ву(22) Заявлено 190379 (21) 2738706/18-21 (51)М. Кл.З

G 01 R 23/ОО с присоединением заявки М

Государственный комитет

СССР ио деяаи., изобретений и открытий (23) Приоритет (53) УДК 621. 317 (088.8) Опубликовано 15.0381. Бюллетень N9 10

Дата опубликования описания 150381

И. Е. Петров, Н. П. Бычков, A. В. Гуров, Б. С.

Л.В. Сабаев и С.Г. Чекин

P2) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЦЕНТРАЛЬНОЙ ЧАСТОТЫ

CHEKTPA СИГНАЛА

Изобретение QTHocHTcR к радиоиэмерительной технике.

Известно цифровое устройство для оптимального измерения частоты сигна- е ла, содержащее последовательно соединенные палосовой фильтр и аналогоцифровой преобразователь, а также регистры, умножители, генераторы аргументов, три гонометрические преобразователи, генератор амплитуд, накопители, квадраторы, сумматоры, блоки извлечения квадратного корня, вычитатель., блок вычисления отноше-ния, формирователь коэффициентов, управляющее и решающее устройство. B этом устройстве производится фильтрация закодированных сигналов двумя цифровыми фильтрами, детектирование и вычисление кодового значения рассогласования между истинным и измеренным значенияьы частоты и форьырование кодового значения измеренной частоты сигнала K1) .

Наиболее близким по технической сущности к предлагаемому устройству является цифровой панорамный измеритель частоты, в котором первые входы двух синхронных детекторов соединены с источником измеряемой частоты, их вторые входы подключены Зо к выходам квадратурного генератора, а выход каждого смесителя через последовательно соединенные фильтр нижних частот, дискретиэатор и аналогоцифровой преобразователь соединен с соответствующим входом блока вычисления, дискретного преобразования

Фурье, выход которого через квадратор соединен со входом блока грубой оценки, вЫход блока грубой оценки uac" тоты соединен со входом интерполятора, другой вход которого. соединен с соответствукщим выходом квадратора, причем вторые входы дискретизатора, соединены с выходами задающего генератора сигналов дискретизации. В

:этом устройстве путем перебора отсчетов энергетического спектра сигнала, формируеьых в устройстве, нахождения максимальных .значений .и последующей интерполяции формируется точная оценка частоты 12).

Недостатками данных устройств являются большое количество оборудования и низкое быстродействйе.

Цель изобретения - сокращение оборудования и повышение быстродействия.

Поставленная цель достигается тем, что в устройстве, содержащем два сме813290 сителя, первые входы которых соединены с источником входного сигнала, вторые входы подключены к выходам квадратурного генератора, а выходы смесителей через последовательно сое диненные фильтры, нижних частот и дискретизаторы, вторые входы которых

5 подключены к выходу задающего генератора сигналов дискретизации, соединены с аналого-цифроными преобразователями, выходы которых соединены соответственно со входами вычислителя,,последний выполнен в виде блока перемножения комплексных чисел, первый и второй входы которого непосредственно, а третий и четвертый входы через ячейки памяти соединены с входаь и вы- 15 числителя, первый и второй выходы блока умножения комплексных чисел соединены с соответствующими входами блока деления, выход которого соединен с блоком шифрации. 20

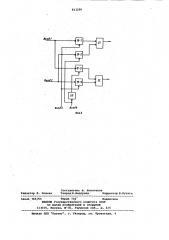

На фиг. 1 показана структурная схема устройства для измерения центральной частоты спектра сигнала, на фиг. 2 — c."òðóêòóðà блока умножения комплексных чисел

Схема содержит смесители 1 и 2, квадратурный генератор 3, фильтры 4 и 5 нижних частот, дискретиэаторы 6 и 7, аналого-цифровые преобразователи 8 и 9, генератор 10 сигналов дискретизации, вычислитель 11, состоящий из ячеек 12 и 13 памяти, блока 14 умножения комплексных чисел, блоков 15 и 16 накопления, блока 17 деления, блока 18 шифрации. Блок 14 умножения комплексных чисел содержит множитель 19-1-19-4 инвеста 20

f знака, с мматооы 21 и 22. Блоки накопления .15 и 16 поедставляют собой последовательно соединенные сумматор, первый вход которого подключен к 40 входу блока, к ячейки памяти, выход которой соединен со вторым входом сумматора и подключен к выходу блока.

Блок 18 шифрации представляет со.бой элементы И ИЛИ, соединенные между собой таким образом, что н соответствии с каждым значением кода, снимаемого с выхода блока 17 деления, формируется значение кода частоты.

Этот блок может быть выполнен в виде постоянного запоминающего устройства, в ячейках которого хранятся коды частоты, а адресом для выбора соответствующей ячейки памяти является код с выхода блока деления. устройство для измерения центральной частоты спектра сигнала работает следующим образом.

На смесителе 12 подаются сдвинутые одно относительно другого íà K /2 гармонические колебания от квадратур- 60 ного генератора 3. (Относительно этого значения частоты в предлагаемом устройстве производится измерение отклонения частоты исследуемого сигнала) . Фильтры 4, 5 обеспечивают выдв- Я ление низкочастотных составляющих спектра колебаний. Дискретизаторы 6 и

7 квантуют по времени компоненты низкочастотного анализируемого сигнала с шагом Т, задаваемым генератором 10.

Аналого-цифровые преобразователи 8 и

9 преобразуют дискретные значения сигнала в цифровую форму.

Цифровая часть устройства реализует алгоритм формирования оценки цен тральной частоты энергетического спектра сигнала в соответствии с выражениями: и, 4)т=а :,) к х „„x<=arctqV;

n=i

; у "и (й=," и- X ) и )

Rgg Хи-q X n) где х и»„ — комплексно-сопряженное значение сигнала в (и-1) Т момент времени, х — комплексное значение сигнала и в и Т момент времени, и 1,2,...,N — количестно анализируемых выборок входного сигнала, необходимых для выработ-. ки оценки частоты т

Выборки входного сигнала хи=хи+)хи с выхода аналого-цифровых преобразователей 8 и 9 поступают в ячейки 12 и 13 вычислителя 11, где они хранятся до поступления от аналого-цифровый преобразователей 8 и 9 следующих выборок сигнала, а на перный и третий входы блока 14 умножения комплексных чисел. Таким образом, на первый и третий входы блока 14 умножения комплексных чисел поступают выборки входного сигнала X„ è Хи с 5 а на второй и четвертый входы этого блока с выхода ячеек оператинной памяти 12 и 13 выборки входного сигна° с б ла хи „и х„„., задержанные на один такт Т. В блоке 14 умножения комплексных чисел вычисляется произведение двух комплексных чисел в соответствии с выражением: с s c

Xè „ хи-(хи- -1хи-4 Ьи+ Хи) = с с, ь s ° с s 6 3

=(X„-q Хи+ (и-< X )ij(XN< Хи-X„ Хи ) с S с Ъ

Коды хи- xN „, хи, хи поступают на соответствующие входы умножителей

19-1-19-4, причем код хи "поступает

S на второй вход третьего умножителя

19-3 через инвертор 20 знака. Произведения (хи <.,хи ) и (х„., хзи) с выходов первого и второго умножителей

19-1-19-2 поступают на входы сумматора 21, с выхода которого код сумки поступает в блоки 16 и 15. Произведе-: с s с ния (х,„ хи) и (-xn q х„) с выходов третьего и четвертого умножителей

19-3 и 19-4 поступают на входы другого сумматора 22,с выхода которого код суммы поступает в другой блок 16 накопN ». ° и »ления. КодыЯс(X„, хи) и Л(х», хи) и- и=

813290 с выходов блоков 15 и 16 накопления поступают в блок 17 деления, в котором производится деление кодаЗщ(1 х,к

% И=1 хи), на код Ке(х хи) °

Полученный в результате деления код р с выхода блока 17 деления поступает в блок 18 шифрации, в котором

5 по этому коду формируется значение оценки частоты wT=arc д . Полученная оценка является оценкой максимально го правдоподобия частоты узкополосного комплексного случайного процесса.

В известном устройстве объем операций для вычисления одной оценки .частоты по и отсчетам энергетического спектра сигнала (на выходах N цифровых фильтров й-ой кратности) в и раэ больше, чем в предлагаемом. поскольку в последнем реализован один коррелятор. Следователь|о, быстродействие предлагаемого изобретения в N 2(} раз выше, чем известного.

Объем аппаратуры в известном цифровом панорамном измерителе примерно в 1,5 раза больше, чем в предлагаемом изобретении из-за большой памяти в блоке вычисления дискретного пре-. образования Фурье и из-за сложного интерполятора,при примерно одинаковом объеме всех остальных узлов.

Формула изобретения

Устройство для измерения централь ной частоты спектра сигнала, содержащее два смесителя, первые входы которых соединены с источником входного сигнала, их вторые входы подключены к выходам квадратурного генератора, а выходы смесителей через последовательно соединенные фильтры нижних частот и дискретизаторы, вторые входы которых подключены к выходу генератора сигналов дискретизации, соединены с аналого-цифровыми преобразователями, выходы которых соединены соответственно со входами вычислителя, отличающееся тем,что,с целью сокращения оборудования и повышения быстродействия, вычислитель выполнен в виде блока переключения комплексных чисел, первый и второй входы которого непосредственно, а третий и четвертый входы через ячейки памяти соединены со входами вычислителя, первый и второй входы блока умножения комплексных чисел через блоки накопления соединены с соответствующими входами блока деления, выход которого соединен с блоком шифрации.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 478261, кл. G 01 и 23j00.

2. Авторское свидетельство СССР

Р 569961, кл. G 01 и 23/00.

813290 дно УЗ Вхо фиг.2

Составитель s. Новоселов

Редактор Л. Повхан Техред М. Федорнак Корректор В. Бутяга

Закаэ 765/ 55 Тираж 732 Подписное

ВНИИПИ Государствейного комитета СССР по делам иэобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4