Устройство для программной реали-зации переключательных cxem

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

<>81 1

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 25.12.78 (21) 2718714/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл з

G 06 F 7/00

Гасударственный комитет

СССР ло делам изобретений и открытий (53) УДК 681.327 (088.8) Опубликовано 15.03.81. Бюллетень № 10

Дата опубликования описания 25.03.81

„.Й. Конндратьег, Ю. Б. Кошевов, А. И. Мариночкин, Ю. М. Фут и В. И. Хохлов (72) Авторы изобретения (71) 3аявктель (54) УСТРОЙСТВО ДЛЯ ПРОГРАММНОЙ РЕАЛИЗАЦИИ

ПЕРЕКЛЮЧАТЕЛЬНЫХ СХЕМ

Изобретение относится к автоматике, в частности к программному управлению технологическим оборудованием.

Известно устройство для программной реализации переключательных схем, содержащее матрицу коммутирующих элементов, блок памяти и блок управления (1).

Недостатком его является невозможность вычисления скобочных форм булевых функций.

Наиболее близким к предлагаемому является устройство для программной реализации переключэтельных схем, содержащее триггер, триггер результата, элемент И, элемент ИЛИ, первый и второй узел инвертирования(2).

Недостатком его является невозможность реализации скобочных форм.

Цель изобретения — расширение функциональных возможностей за счет реализации скобочных форм.

Поставленная цель достигается тем, что в устройство введены блок проверки на нечетность, ячейки памяти, распределитель и блок подсчета числа, ответвлений диаграммы, причем первые входы блока проверки

2 на нечетность, ячейки памяти и распределителя объединены между собой и являются управляющим входом устройства, второй вход блока проверки на нечеткость является входом аргумента, а выход соединен с первым входом триггера и вторым входом ячейки памяти, выход которого соединен со вторым входом распределителя, третий вход которого подключен к выходу ячейки памяти, а выходы распределителя соединены с входами блока подсчета числа ответвлений

ip д и а г р а м м ы, выход которого соединен со вторым входом триггера.

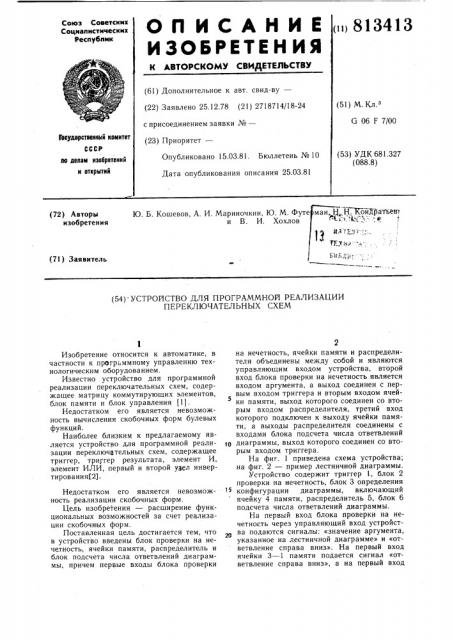

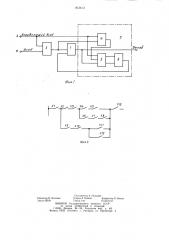

На фиг. 1 приведена схема устройства; на фиг. 2 — пример лестничной диаграммы.

Устройство содержит триггер 1, блок 2 проверки на нечетность, блок 3 определения конфигурации диаграммы, включающий ячейку 4 памяти, распределитель 5, блок 6 подсчета числа ответвлений диаграммы.

На первый вход блока проверки на нечетность через управляющий вход устройства подаются сигналы: «значение аргумента, указанное на лестничной диаграмме» и «ответвление справа вниз». На первый вход ячейки 3 — 1 памяти подается сигнал «ответвление справа вниз», а на первый вход з

8l распределителя 3 — 2 подаются сигналы:

«ответвление слева вниз», «ответвление справа вниз» и «ответвление справа вверх». Блок

6 подсчета числа ответвлений диаграммы может, например состоять из двоичного реверсивного счетчика и дешифратора. Двоичный реверсивный счетчик имеет вход «сложение», вход «вычитание» и вход установки нуля, выходы двоичного реверсивного счетчика соединены со входами дешифратор». При этом первым вхо,io» блока 3- -3 нужно припять вход «вычитание» двоичного реверсивного счетчика, вторым входом блок» 3- - 3 нужно принять вход «сложение» двоичного реверсивного счетчика, а выходом блока 3 — 3 будет выход дешифратора.

Устройство работает следующим образом.

В кс3

Дл3! любой переключательной схемы Бычисле11ие ведется в следующем порядке: вычпсле1!Не н»чин»ется с аргумента, p;Ictto.ltlже«ного в верхней левой части схемы (для схехсы п» сриг. 2 этс3 аргумент Хl ) . .Затем

П Р 0 !3 Е Р 51 К3 Т С 31 П 0 С:I Д 0 Б» ТЕЛ Ы! 0 Б СС . Я Р Г У 1<1 ?? ??????, ?? ????????????1???????????? it?? ???????? ???? ?????????????? ???????????????????? ??????????????????, ???? ???????????????????? 01?????????????????? ???? ?????????????????? ???????????? ????????. ?????? ?????????????? ??????????????!???????? ???????? ???????????????????? ??3 ??????????!????,??!?? ?????????????? ?????????????????? ?? ??13??,???????????????? ??i>iwucrtenilå по этой сту-!!с пи, ня

Iè÷IIoé LEI3ã!p»ììû прп Бычислеnuu используются также ответвления «слева вниз».

Эти <1твств Ienuu п» фиг. 2 обозначены стрелками слева от аргх меь!тс1« Х2, Х4, Х! 1.

В начале вычисле!!ия значение функции уста« liiлпваесся равное !. В процессе вычисления функция может принимать значение 0 в двух случаях.

При»!ер 1. Функция принимает 3!1ачение

«О» при проверке аргумента, имею«;его «ответвление спр»вя», если действительное значение этого аргумент» совпадает со значением аргумента, указанного на лестничной диаграмме, и значение функции при проверке предыду1цего аргумента было равно . !

/риссер 2. Функция принимает значение

«О» при проверке аргумента, не имеющего

«ответвления справа», если действительное

3413 значение этого аргумента противоположно значению аргумента, указанного на лестничной диаграмме и значение функции при проверке предыдущего аргумента было равно 1.

В первом случае сразу же (по наличию ответвления справа) обнаруживается дизъюнктивный член (параллельная цепочка) для той части функции, в которую входит проверяемый аргумент, и установка значения «0» для функции означает, что про-!

О веренный член дизъюнкции равен 1, следовательно, вся дизъюнкция равна 1 и остается найти лишь последний аргумент последнего члена дизъюнкции, после проверки которого функция вновь должна принять !

5 значение равное l, Этот последний аргумент находят по следующему правилу. По ходу вычисления (описанному выше) подсчиты«»ется число ответвлений «справа вниз» и

«справя вверх». Тот ближайший шаг вычислений, в котором число ответвлений «спра о ва вверх» превышает на единицу число ответвлений «справа вниз» указывает на последний аргумент последнего члена данной .! и з.1> к> н к ц и и . П р и 3TQ»1 ф х: H K IL H SI нимяет значение 1 и вычисление продолжается.

Если же при проверке аргумента, имеющего «ответвление «справа вниз», его дейст«ительное состояние не совпадает с состоянием, указанным на лестничной диаграмме и предыду!цее значение функции равно ., то это значение функции сохраняется. Это

î n3 I3eT, что проверенный член дизьюнкции равен 0 и необходимо вычислять остальные пены дизъюнкции.

Во втором случае необходимо выяснить имеет IH часть функции, в которую входит только что проверенный аргумент, дизъюнктпвный член. Если такого члена нет, то можно утверждать, что функция равна «О» и это значение сохраняется до конца вычислений, Наличие дизъюнктивного члена опредсляется по следующему правилу. По ходу

I«>l tEIcления функции подсчитывается количество ответвлений «слева вниз» и «справа

«низ». Если в каком-то из шагов вычислений число ответвлений «справа вниз» превысит на единицу число ответвлений «слева

45 вниз», это является указанием на наличие дизьюнктивного члена к той части функции, которая приняла значение «О». При этом в следующем шаге вычислений функция вновь принимает значение 1 и вычисление

50 продолжается.

Описанный порядок и правила вычисления позволяют однозначно определить значение функции, а, следовательно, автоматизировать процесс программной реализации лгобой сколь-угодно минимизированной перекл!Очательной схемы.

В начале вычисления триггер 1 находится в единичном состоянии (значение функции равно 1) . В процессе вычисления после813413 довательно, по шагам для каждого аргумента переключзтельной схемы на первый вход блока 2 подаются сигналы: «значение аргумента, указанного на лестничной диаграмме» и «ответвление справа», а на второй вход этого блока подается сигнал действительного состояния аргумента. Если для какого-либо аргумента, действительное состояние аргумента совпадает с значением аргумента, указанного на лестничной диаграмме, и имеется сигнал «ответвление справа», то на выходе блока 2 проверки на нечетность появляется сигнал, устанавливающий триггер 1 в нулевое состояние, функция принимает значение О (пример 1, описанный в кратком пояснении процесса вычисления) .

Наличие сигнала «ответвление справа» при установке триггера 1 в нулевое состояние запоминается в ячейке 4 памяти. Сигналы с выхода триггера 1 и ячейки 4 памяти, поступающие на второй и третий входы распределителя 5 организуют работу распределителя 5 таким образом, что на первый выход распределителя 5 подаются сигналы «ответвление справа вниз», а на второй выход распределителя 5 подаются сигналы «ответвление справа вверх». Эти сигналы соответственно поступают на первый и второй входы блока 6. Когда количество сигналов «ответвление справа вверх» превысит на единицу количество сигналов «ответвление справа вниз», на выходе блока 6 появляется сигнал, устанавливающий триггер 1 в единичное состояние (функция принимает значение 1) и вычисление продолжается.

Если же для какого-либо аргумента, действительное состояние аргумента не совпадает с значением этого аргумента, указанного на лестничной диаграмме, и сигнала

«ответвление справа» нет, то на выходе блока проверки на нечетность также появляется сигнал, устанавливающий триггер 1 в нулевое состояние, функция принимает значение О.

Отсутствие сигнала «ответвление справа» при установке триггера 1 в нулевое состояние запоминается в ячейке 4 памяти.

Сигналы с выхода триггера 1 и ячейки 4 памяти организуют работу распределителя

5 таким образом, что на первый выход распределителя 5 подаются сигналы «ответвление слева вниз», а на второй выход распределителя 5 подаются сигналы «ответвление справа вниз». Эти сигналы, соответственно,. поступают на первый и второй входы блока

6. Когда количество сигналов «ответвление справа вниз» превысит на единицу количество сигналов «ответвление слева вниз»

J на выходе блока 6 появляется сигнал, устанавливающий триггер 1 в единичное состояние (функция принимает значение 1) и вычисление продолжается. После проверки всех аргументов реализуемой переключательной схемы значение функции (1 или О) снимается с. выхода устройства.

Предлагаемое устройство для программной реализации переключательных схем по сравнению с известными образцами аналогичного оборудования расширяет функциональные возможности и повышает надежность устройства.

Формула изобретения

Устройство для программной реализации переключательных схем, содержащее триггер, выход которого является выходом устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет реализации скобочных форм в него введены блок проверки на нечетность, ячейка намяти, распределитель и блок подсчета числа ответвлений диаграммы, причем первые входы блока проверки на нечетность, зп ячейки памяти и распределителя объединены между собой и являются управляющим входом устройства, второй вход блока проверки на нечетность является входом аргумента, а выход соединен с первым входом триггера и вторым входом ячейки памяти, выход которого соединен со вторым входом распределителя, третий вход которого подключен к выходу ячейки памяти, а выходы распределителя соединены с входами блока подсчета числа ответвлений диаграммы, 40 выход которого соединен со вторым входом триггера.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Ко 454547, кл. G 06 F 7/00, 1972.

45 2. Авторское свидетельство СССР

_#_e 610104, кл. G 06 F 7/00, 1975.

813413

Х73

Редактор Н. Воловик

Заказ 285/61

Составитель Е. Пупырев

Техред А. Бойкас Корректор О. Билак

Тираж 745 Подписное

ВНИИПИ .Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4