Устройство для умножения двоичныхчисел b дополнительных кодах

Иллюстрации

Показать всеРеферат

ОЛ ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскин

Социалистических

Реслублик (ii)813418

l=== ДФ (61) Дополнительное к авт. свид-ву— (5!) М.К . (22) Заявлено 21.08.78 (21) 26609!4/18-24

G 06 F 7/52 с присоединением заявки №вЂ” (23) Приоритет—

Гееударстеенный комитет СССР па делан изобретений и атнрытий

Опубликовано 5.03.81. Бюллетень № 10 (53) УДК 681.325 (088.8) Дата опубликования описания 25.03.81 (72) А вторы изобретения

Ю. Я. Ледянкин, Б. Н. Малиновский, Л. Г. Козлов и В. П. Боюн

Ордена Ленина институт кибернетики АН Украинской CCP (71) Заявитель (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ДВОИЧНЫХ ЧИСЕЛ

В ДОПОЛНИТЕЛЬНЫХ КОДАХ

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах специальных цифровых вычислительных машин.

Известно устройство последовательного типа для умножения двоичных чисел, содержащее регистры множимого, множителя

5 и частичного произведения, элементы И, инвертор. Устройство позволяет выполнять умножение двоичных чисел в дополнительных кодах (I).

Недостатком такого устройства является невысокое быстродействие, связанное с необходимостью выполнения корректирующих циклов суммирования для учета умножения множимого на знак множителя. Особенно значительное понижение быстродействия происходит при небольшой разрядности множителя.

Наиболее близким к предлагаемому является устройство последовательного типа для умножения двоичных чисел, содержащее регистр множимого, регистр множителя, регистр частичного произведения, узел 20 суммирования, элемент И, причем входы регистров множимого и множителя соединены с входными шинами множимого и множителя соответственно, а выходы — с первым

2 и вторым входами элемента И, выход регистра множимого соединен также со вторым входом этого регистра, выход элемента И соединен с первым входом узла суммирования, выход узла суммирования соединен со входом регистра результата, выход регистра результата соединен со вторым входом узла суммирования и с выходной шиной результата. Данное устройство позволяет выполнять умножение двоичных чисел как в прямых, так и в дополнительных кодах без специальной коррекции результата за счет расширения разрядной сетки сомножителей (2) и (3) .

Недостатком данного устройства является невысокое быстродействие при выполнении умножения двоичных чисел в дополнительных кодах, связанное с расширением разрядной сетки сомножителей, которое увеличивает общее число циклов суммирования.

Цель изобретения — повышение быстродействия устройства.

Для достижения поставленной цели в устройство, содержащее регистр множимого, регистр множителя, регистр результата, узел суммирования, элемент И, причем вхо813418

15

Формула изобретения ды регистров множимого и множителя соединены с входными шинами множимого и множителя устройства соответственно, выход регистра множимого соединен со вторым входом этого регистра, выход элемента И соединен с первым входом узла суммирования, выход узла суммирования соединен со входом регистра результата, выход регистра результата с выходной шиной результата устройства и со вторым входом узла суммирования, введены триггер модификации сдвига и два преобразователя кода в дополнительный, причем выход регистра множимого подключен к установочному входу триггера модификации сдвига, управляющий вход которого соединен с управляющим входом устройства, выходы триггера модификации сдвига и регистра множителя с информационными входами первого и второго преобразователей кода в дополнительный соответственно, управляющие входы которых соединены с выходом знакового раз.ряда регистра множителя, выходы первого и второго преобразователей кода в дополнительный соединены с первым и вторым входами элемента И соответственно.

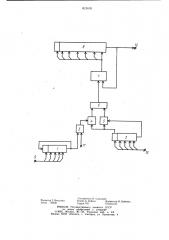

На чертеже приведена схема устройства.

Устройство содержит регистр 1 множимого, регистр 2 множителя, триггер 3 модификации сдвига, первый 4 и второй 5 преобразователи кода в дополнительный, элемент И 6, узел 7 суммирования, регистр 8 результата, входные шины 9 и 10 множимого и множителя соответственно, управляющий вход 11 устройства, выходную шину 12 результата.

При работе устройства в регистры множимого и множителя записываются сомножители в дополнительном коде с учетом знаков. Если множитель положительный, то нулевое значение его знакового разряда определяет режим работы первого 4 и второго

5 преобразователей (режим без преобразования). Оба сомножителя будут поступать на вход элемента И 6 без изменения. При этом первые m микротактов сдвига кода множимого триггер 3 будет установлен в нулевые или единичное состояние в зависимости от текущего разряда множимого. Но начиная с (m + 1)-го микротакта, когда он будет установлен в состояние, соответствующее знаковому разряду множимого, и далее в течение m микротактов состояние триггера 3 не меняется. Если множитель отрицательное число, то его единичный знаковый разряд определяет режим работы первого

4 и второго 5 преобразователей кода (режим преобразования чисел в дополнительный код). В этом случае на входы элемента

И 6 поступает дополнительный код от исходного значения сомножителей. Триггер

3 модифйкации сдвига работает здесь так го

Зо

<о

50 же, как описано выше. В узле 7 суммирования производится сложение разрядов текущего и прошлого частичных произведений с учетом переноса возникшего при предыдущем суммировании.

В предлагаемом устройстве может быть реализован способ умножения, начиная как со старших, так и с младших разрядов множителя. Введение триггера модификации сдвига и двух преобразователей позволяет производить умножение двоичных чисел в дополнительных кодах без коррекции и без расширения разрядной сетки сомножителей, что приводит к уменьшению общего числа циклов суммирования почти вдвое, к повышению быстродействия устройства в 1, 8 раз по сравнению с известным устройством.

Устройство для умножения двоичных чисел в дополнительных кодах, содержащее регистр множимого, регистр множителя, регистр результата, узел суммирования, элемент И, причем входы регистров множимого и множителя соединены с входными шинами множимого и множителя устройства соответственно, выход регистра множимого соединен со входом этого регистра, выход элемента И соединен с первым входом узла суммирования, выход узла суммирования соединен со входом регистра результата, выход регистра результата с выходной шиной результата устройства и со входом узла суммирования, отличающееся тем, что, с целью повышения быстродействия, в него введены триггер модификации сдвига и два преобразователя кода в дополнительный, причем выход регистра множимого подключен к установочному входу триггера модификации сдвига, управляющий вход которого соединен с управляющим входом устройства, выходы триггера модификации сдвига и регистра множителя с информационными входами первого и второго преобразователей кода в дополнительный соответственно, управляющие входы которых соединены с выходом знакового разряда регистра множителя, выходы первого и второго преобразователей кода в дополнительный соединены с первым и вторым входами элемента И соответственно.

Источники информации, принятые во внимание при экспертизе

1. Карцев М. А. Апифметика цифровых машин. М., «Наука», 1969, с. 484 — 489., рис. 4 — 19.

2. Карцев М. А. Арифметика цифровых машин. М., «Наука», 1969, с. 459, рис. 4 — 14 (прототип).

3. Карцев М. А. Арифметика цифровых машин. М., «Наука», 1969, с. 488.

813418

Составитель Н. Слюсарев

Редактор Т. Веселова Техред А. Бойкас Корректор Н. Бабинец

Заказ 285/61 Тираж 745 Подписное

ВНИИ11И Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4